XADC 功能介绍和应用指南

宋祈真 2019-01-25

一、XADC 功能介绍

XADC 是内嵌在 Xilinx 7 系列 FPGA 芯片和 Zynq7000 可编程 SOC 芯片中的的高速 AD 转换器模块。

该模块内有两个 12 位 AD 转换器(确保 10 位可靠精度),采样速率达到每秒 1 兆次。XADC 可测量多

达 17 个外部模拟通道的输入信号,同时还能对芯片的温度和供电电压进行监测和报警。XADC 能自动

循环扫描所有的模拟输入通道,大大地减轻了主机的负担。特别是 Zynq7000 芯片内部集成了 2 个 ARM9

处理机芯片、FPGA 逻辑和 AD 转换器,丰富的资源构成完整的信号采集和处理系统,特别适合对精度

要求不是太高但对成本又较敏感的测控仪器仪表等方面的应用,既可简化设备又可提高性价比,因

此很受业界欢迎。

有关 XADC 的官方资料主要包含在 Xilinx的“7SeriesFPGAsXADCGuide(UG480)”和“XADC

Wizard v3.3 LogicCORE IP Product Guide(PG091)”等技术文档中。这些资料内容丰富,但也比

较庞杂,用户需要耗费大量时间才能消化理解。同时已有资料对应用实例的介绍又不太详尽。笔者

主要对这两份资料的内容进行了梳理和精简,省略了仿真和 JTAG 方面的内容,重点放在介绍和理解

XADC 控制寄存器的操作方式。最后展示了在 Vivado 和 SDK 开发环境下的一个简单 XADC 应用实例。

希望此文能帮助有兴趣的读者能在较短时间内能掌握和应用 XADC。

本文在短时间内完成,加上笔者水平有限,错误和缺漏难于避免,敬请原谅和批评指正。

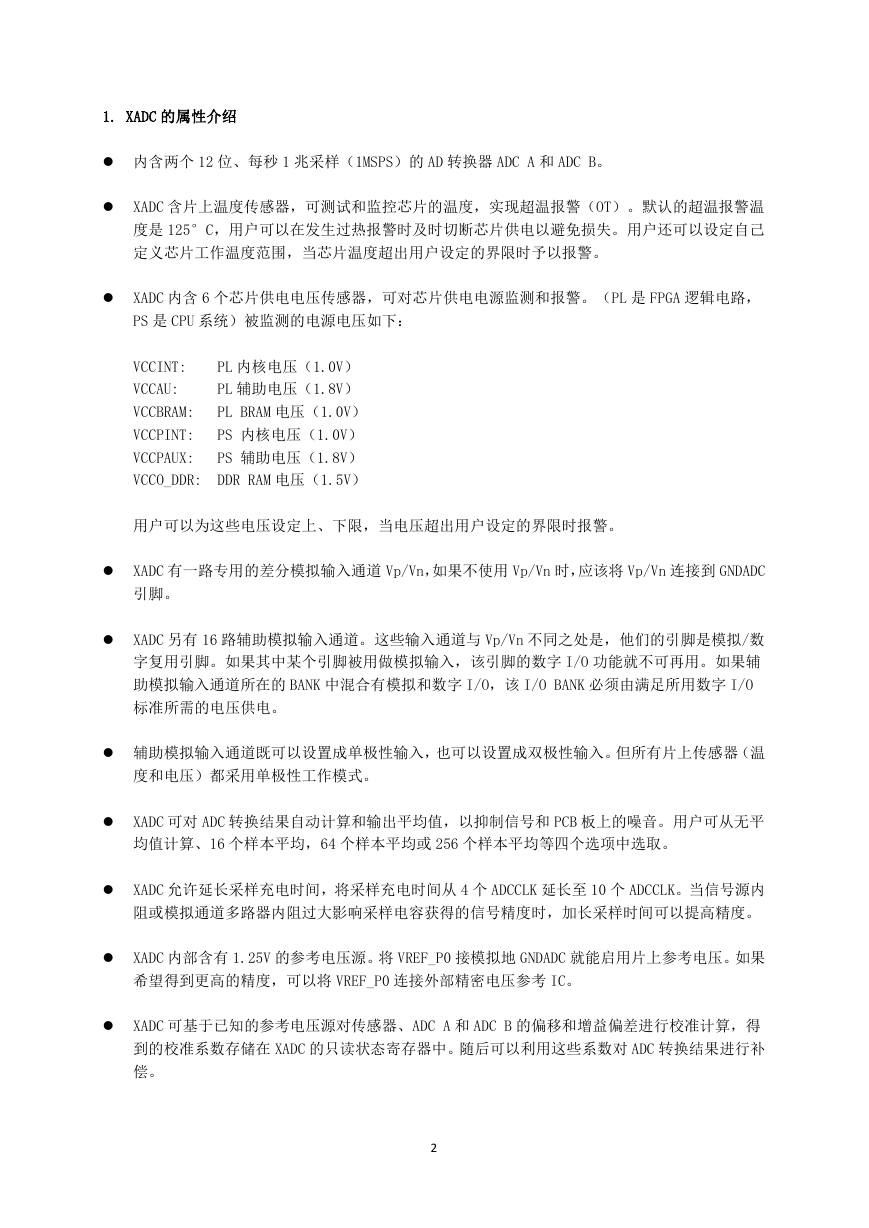

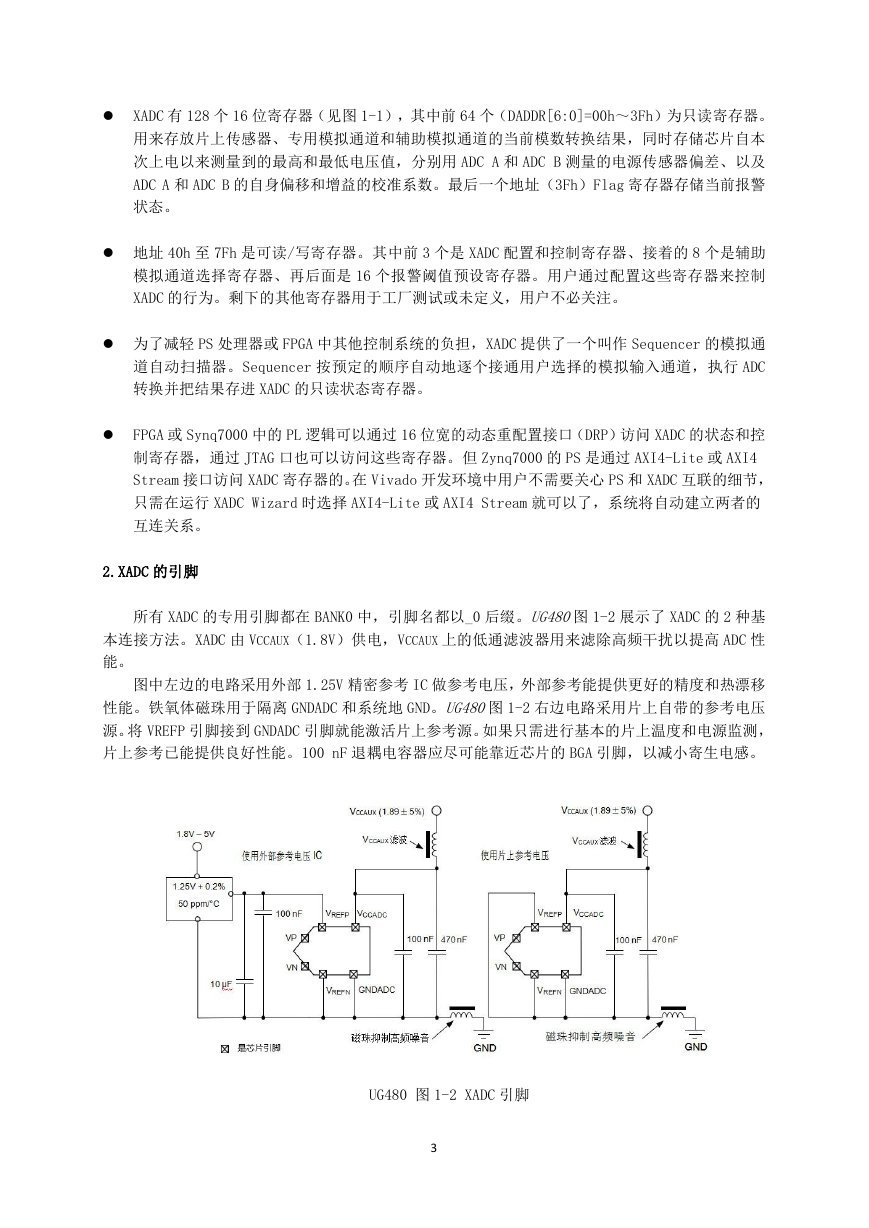

UG480 图 1-1 XADC 原理框图

本文的参考资料主要来自 Xilinx的 UG480和 PG091等技术文档,为便于读者对照原文查阅更详

细的信息,本文引用的表格或插图仍采用原文的编序。

1

�

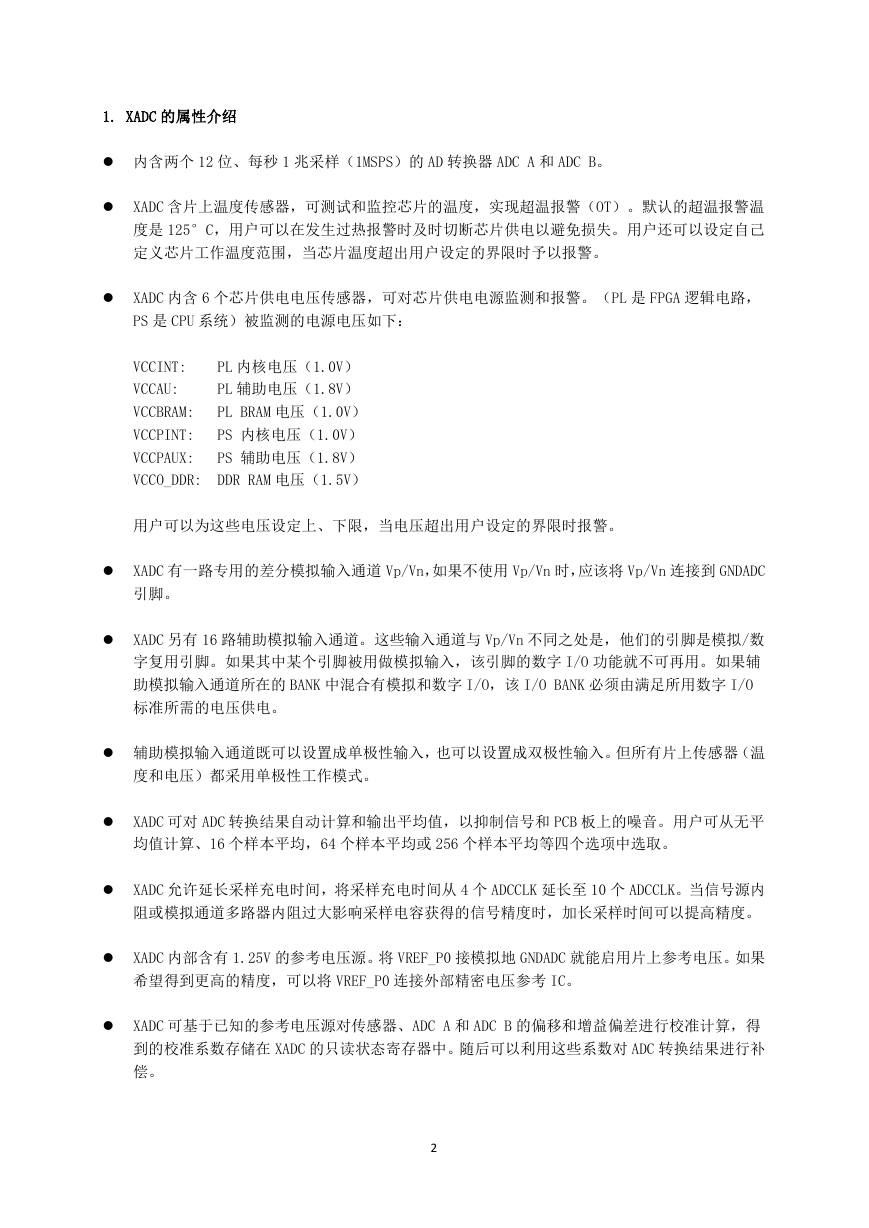

1. XADC 的属性介绍

内含两个 12 位、每秒 1 兆采样(1MSPS)的 AD 转换器 ADC A 和 ADC B。

XADC 含片上温度传感器,可测试和监控芯片的温度,实现超温报警(OT)。默认的超温报警温

度是 125°C,用户可以在发生过热报警时及时切断芯片供电以避免损失。用户还可以设定自己

定义芯片工作温度范围,当芯片温度超出用户设定的界限时予以报警。

XADC 内含 6 个芯片供电电压传感器,可对芯片供电电源监测和报警。(PL 是 FPGA 逻辑电路,

PS 是 CPU 系统)被监测的电源电压如下:

VCCINT:

VCCAU:

VCCBRAM:

VCCPINT:

VCCPAUX:

VCCO_DDR:

PL 内核电压(1.0V)

PL 辅助电压(1.8V)

PL BRAM 电压(1.0V)

PS 内核电压(1.0V)

PS 辅助电压(1.8V)

DDR RAM 电压(1.5V)

用户可以为这些电压设定上、下限,当电压超出用户设定的界限时报警。

XADC 有一路专用的差分模拟输入通道 Vp/Vn,如果不使用 Vp/Vn 时,应该将 Vp/Vn 连接到 GNDADC

引脚。

XADC 另有 16 路辅助模拟输入通道。这些输入通道与 Vp/Vn 不同之处是,他们的引脚是模拟/数

字复用引脚。如果其中某个引脚被用做模拟输入,该引脚的数字 I/O 功能就不可再用。如果辅

助模拟输入通道所在的 BANK 中混合有模拟和数字 I/O,该 I/O BANK 必须由满足所用数字 I/O

标准所需的电压供电。

辅助模拟输入通道既可以设置成单极性输入,也可以设置成双极性输入。但所有片上传感器(温

度和电压)都采用单极性工作模式。

XADC 可对 ADC 转换结果自动计算和输出平均值,以抑制信号和 PCB 板上的噪音。用户可从无平

均值计算、16 个样本平均,64 个样本平均或 256 个样本平均等四个选项中选取。

XADC 允许延长采样充电时间,将采样充电时间从 4 个 ADCCLK 延长至 10 个 ADCCLK。当信号源内

阻或模拟通道多路器内阻过大影响采样电容获得的信号精度时,加长采样时间可以提高精度。

XADC 内部含有 1.25V 的参考电压源。将 VREF_P0 接模拟地 GNDADC 就能启用片上参考电压。如果

希望得到更高的精度,可以将 VREF_P0 连接外部精密电压参考 IC。

XADC 可基于已知的参考电压源对传感器、ADC A 和 ADC B 的偏移和增益偏差进行校准计算,得

到的校准系数存储在 XADC 的只读状态寄存器中。随后可以利用这些系数对 ADC 转换结果进行补

偿。

2

�

XADC 有 128 个 16 位寄存器(见图 1-1),其中前 64 个(DADDR[6:0]=00h~3Fh)为只读寄存器。

用来存放片上传感器、专用模拟通道和辅助模拟通道的当前模数转换结果,同时存储芯片自本

次上电以来测量到的最高和最低电压值,分别用 ADC A 和 ADC B 测量的电源传感器偏差、以及

ADC A 和 ADC B 的自身偏移和增益的校准系数。最后一个地址(3Fh)Flag 寄存器存储当前报警

状态。

地址 40h 至 7Fh 是可读/写寄存器。其中前 3 个是 XADC 配置和控制寄存器、接着的 8 个是辅助

模拟通道选择寄存器、再后面是 16 个报警阈值预设寄存器。用户通过配置这些寄存器来控制

XADC 的行为。剩下的其他寄存器用于工厂测试或未定义,用户不必关注。

为了减轻 PS 处理器或 FPGA 中其他控制系统的负担,XADC 提供了一个叫作 Sequencer 的模拟通

道自动扫描器。Sequencer 按预定的顺序自动地逐个接通用户选择的模拟输入通道,执行 ADC

转换并把结果存进 XADC 的只读状态寄存器。

FPGA 或 Synq7000 中的 PL 逻辑可以通过 16 位宽的动态重配置接口(DRP)访问 XADC 的状态和控

制寄存器,通过 JTAG 口也可以访问这些寄存器。但 Zynq7000 的 PS 是通过 AXI4-Lite 或 AXI4

Stream 接口访问 XADC 寄存器的。在 Vivado 开发环境中用户不需要关心 PS 和 XADC 互联的细节,

只需在运行 XADC Wizard 时选择 AXI4-Lite 或 AXI4 Stream 就可以了,系统将自动建立两者的

互连关系。

2.XADC 的引脚

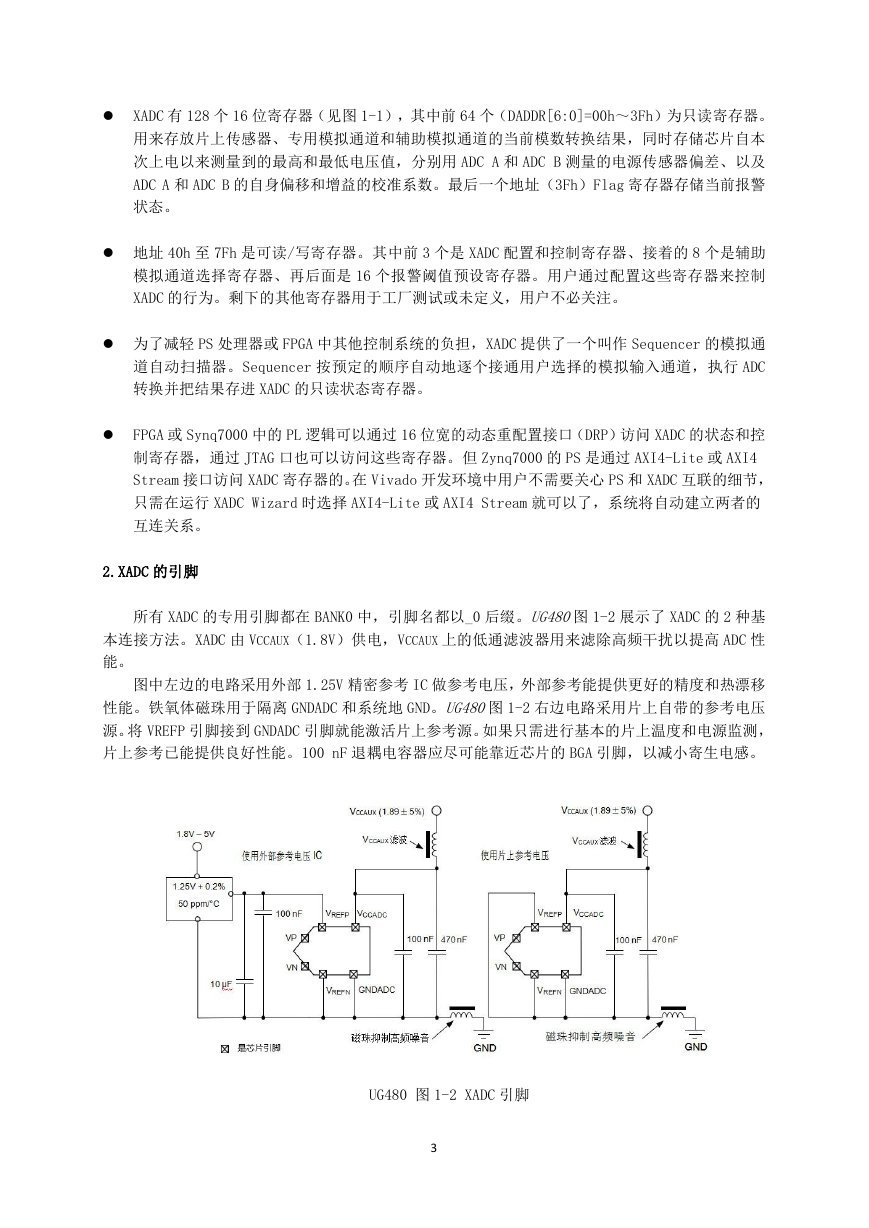

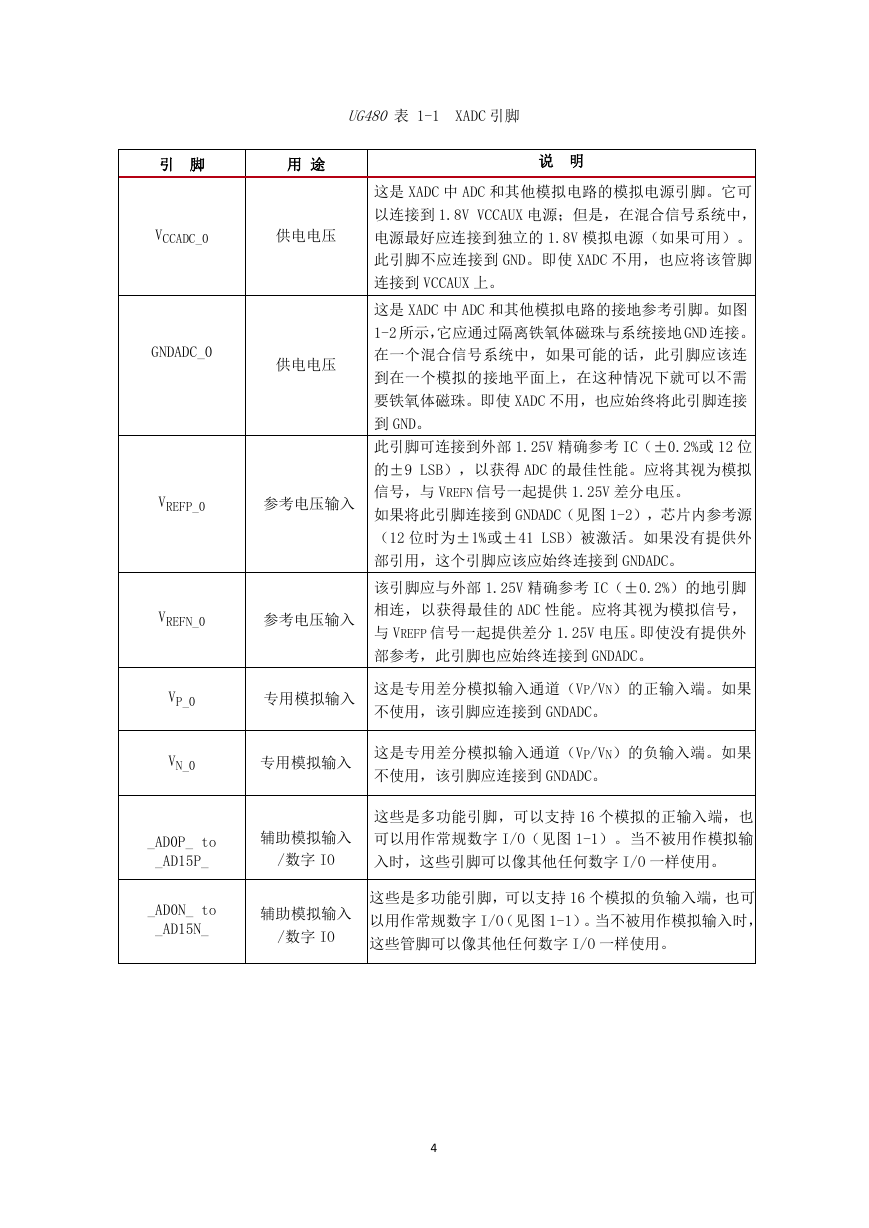

所有 XADC 的专用引脚都在 BANK0 中,引脚名都以_0 后缀。UG480图 1-2 展示了 XADC 的 2 种基

本连接方法。XADC 由 VCCAUX(1.8V)供电,VCCAUX 上的低通滤波器用来滤除高频干扰以提高 ADC 性

能。

图中左边的电路采用外部 1.25V 精密参考 IC 做参考电压,外部参考能提供更好的精度和热漂移

性能。铁氧体磁珠用于隔离 GNDADC 和系统地 GND。UG480图 1-2 右边电路采用片上自带的参考电压

源。将 VREFP 引脚接到 GNDADC 引脚就能激活片上参考源。如果只需进行基本的片上温度和电源监测,

片上参考已能提供良好性能。100 nF 退耦电容器应尽可能靠近芯片的 BGA 引脚,以减小寄生电感。

UG480 图 1-2 XADC 引脚

3

�

UG480 表 1-1

XADC 引脚

引 脚

用 途

说 明

VCCADC_0

供电电压

GNDADC_0

供电电压

VREFP_0

参考电压输入

VREFN_0

参考电压输入

这是 XADC 中 ADC 和其他模拟电路的模拟电源引脚。它可

以连接到 1.8V VCCAUX 电源;但是,在混合信号系统中,

电源最好应连接到独立的 1.8V 模拟电源(如果可用)。

此引脚不应连接到 GND。即使 XADC 不用,也应将该管脚

连接到 VCCAUX 上。

这是 XADC 中 ADC 和其他模拟电路的接地参考引脚。如图

1-2 所示,它应通过隔离铁氧体磁珠与系统接地 GND 连接。

在一个混合信号系统中,如果可能的话,此引脚应该连

到在一个模拟的接地平面上,在这种情况下就可以不需

要铁氧体磁珠。即使 XADC 不用,也应始终将此引脚连接

到 GND。

此引脚可连接到外部 1.25V 精确参考 IC(±0.2%或 12 位

的±9 LSB),以获得 ADC 的最佳性能。应将其视为模拟

信号,与 VREFN 信号一起提供 1.25V 差分电压。

如果将此引脚连接到 GNDADC(见图 1-2),芯片内参考源

(12 位时为±1%或±41 LSB)被激活。如果没有提供外

部引用,这个引脚应该应始终连接到 GNDADC。

该引脚应与外部 1.25V 精确参考 IC(±0.2%)的地引脚

相连,以获得最佳的 ADC 性能。应将其视为模拟信号,

与 VREFP 信号一起提供差分 1.25V 电压。即使没有提供外

部参考,此引脚也应始终连接到 GNDADC。

VP_0

VN_0

专用模拟输入

这是专用差分模拟输入通道(VP/VN)的正输入端。如果

不使用,该引脚应连接到 GNDADC。

专用模拟输入

这是专用差分模拟输入通道(VP/VN)的负输入端。如果

不使用,该引脚应连接到 GNDADC。

_AD0P_ to

_AD15P_

辅助模拟输入

/数字 IO

这些是多功能引脚,可以支持 16 个模拟的正输入端,也

可以用作常规数字 I/O(见图 1-1)。当不被用作模拟输

入时,这些引脚可以像其他任何数字 I/O 一样使用。

_AD0N_ to

_AD15N_

辅助模拟输入

/数字 IO

这些是多功能引脚,可以支持 16 个模拟的负输入端,也可

以用作常规数字 I/O(见图 1-1)。当不被用作模拟输入时,

这些管脚可以像其他任何数字 I/O 一样使用。

4

�

二、XADC 的状态和控制寄存器

XADC 的所有功能都是通过状态和控制寄存器实现的。了解这些寄存器的位定义功能可以帮助用

户理解 Vivado 的 XADC Wizard 中的设计界面和掌握应用 XADC IP 的 API 函数。下面做详细介绍。

1. XADC 的状态寄存器

XADC 的前 64 个地址位置(DADDR[6:0]=00h 到 3Fh)是只读状态寄存器。用来存储片上传感器和

外部模拟通道的模数转换结果。每个传感器和外部模拟输入通道都有一个唯一的通道地址,每个模

拟通道的测量结果存储在通道选择寄存器(48h 和 49h)中指定地址的状态寄存器中(见 UG480 表

4-1)。

例如,ADC 多路复用器通道 0(温度传感器)的测量结果存储在通道地址 00h 的状态寄存器中。

来自 ADC 多路复用器信道 1(VCCINT)的结果存储在地址 01h。

状态寄存器还存储从设备加电或 XADC 的最后一次用户重置开始记录的芯片上传感器的最大和最

小测量值。表 3-1 定义了状态寄存器。

UG480 表 3-1 状态寄存器(只读)

名

温度

VCCINT

VCCAUX

VP/VN

VREFP

地址

00h

01h

02h

03h

04h

VREFN

05h

VCCBRAM

未定义

Supply A offset

ADC A offset

06h

07h

08h

09h

说明

温度传感器测量结果存储在此位置。数据放在在 16

位寄存器的最高 12 位。

VCCINT 测量结果存储在该位置。数据放在在 16 位寄存

器的高 12 位。

VCCAUX 测量结果存储在该位置。数据放在在 16 位寄存

器的高 12 位。

专用模拟输入通道上的转换结果存储在此寄存器中。

数据在 16 位寄存器中与最高位对齐的。

参考输入 VREFP 上的转换结果存储在此寄存器中。数

据在 16 位寄存器中与最高位对齐的。

参考输入 VREFN 上的转换结果存储在此寄存器中。该

通道在双极模式下进行测量。通过双极模式下的测量,

可以测量到 0V(VREFN)左右的微小正负偏移。电源传

感器也用于测量 VREFN,因此 1 LSB=3V/4096。数据在

16 位寄存器中是最高位对齐的。

VCCBRAM 电源监视器测量结果存储在该位置。数据在 16

位寄存器中是最高位对齐的。

这些位置未使用,并且包含无效数据。

用 ADC A 计算的传感器偏移校准系数存储在此位置。

ADC A 的偏移校准系数存储在此位置。

5

�

ADC A gain

未定义

(1)

VCCPINT

VCCPAUX

(1)

VCCO_DDR(1)

0Ah

0Bh to

0Ch

0Dh

0Eh

0Fh

ADC A 的增益误差校准系数存储在此位置。

这些位置未使用,并且包含无效数据。

PS 电源 VCCPINT 上的转换结果存储在此寄存器中。数据

在 16 位寄存器中是最高位对齐。测量 VCCPINT 时使用电

源传感器。

PS 电源 VCCPAUX 的转换结果存储在此寄存器中。数据在

16 位寄存器中是最高位对齐的。测量 VCCPAUX 时使用电

源传感器。

PS 电源 VCCO_DDR 的转换结果存储在此寄存器中。数据在

16 位寄存器中是最高位对齐的。测量 VCCO_DDR 时使用电

源传感器。

VAUXP[15:0]/

VAUXN[15:0]

10h to 1Fh

辅助模拟输入通道上的转换结果存储在此寄存器中。

数据在 16 位寄存器中是最高位对齐的。

Max temp

20h

自通电或上次 XADC 复位后记录的最大温度测量

值。

Max VCCINT

Max VCCAUX

Max VCCBRAM

21h

自通电或上次 xadc 重置后记录的最大 VCCINT 测量值。

22h

自通电或上次 xadc 重置后记录的最大 VCCAUX 测量值。

23h

自通电或上次 XADC 重置后记录的最大 VCCBRAM 测量值。

Min temp

24h

自通电或上次 XADC 复位后记录的最低温度测量值。

Min VCCINT

Min VCCAUX

Min VCCBRAM

VCCPINT

(1) max

VCCPAUX

(1) max

VCCO_DDR

(1) max

Unassigned

25h

自上电或上次 XADC 复位后记录的最小 VCCINT 测量值。

26h

27h

28h

29h

2Ah

2Bh

自上电或上次 XADC 复位后记录的最小 VCCAUX 测量值。

自上电或上次 XADC 复位后记录的最小 VCCBRAM 测量值

自上电或上次 XADC 复位后记录的最大 VCCPINT 测量值

自上电或上次 XADC 复位后记录的最大 VCCPAUX 测量值

自上电或上次 XADC 复位后记录的最大 VCCO_DDR 测量值

未定义

6

�

VCCPINT

(1) min

VCCPAUX

(1) min

VCCO_DDR

(1) min

未定义

Supply B offset

ADC B offset

ADC B gain

2Ch

2Dh

2Eh

2Fh

30h

31h

32h

自上电或上次 XADC 复位后记录的最小 VCCPINT 测量值

自上电或上次 XADC 复位后记录的最小 VCCPAUX 测量值

自上电或上次 XADC 复位后记录的最小 VCCO_DDR 测量值

未定义

用 ADC B 计算的电源传感器偏移校准系数存储在此位

置。

ADC B 的偏移校准系数存储在此位置。

ADC B 的增益误差校准系数存储在该位置。

Undefined

33h to 3Eh 未使用

Flag

3Fh

此寄存器包含常规状态信息(请参见 Flag Register)

注 1:这些通道仅适用 Zynq-7000 AP SoC 器件。

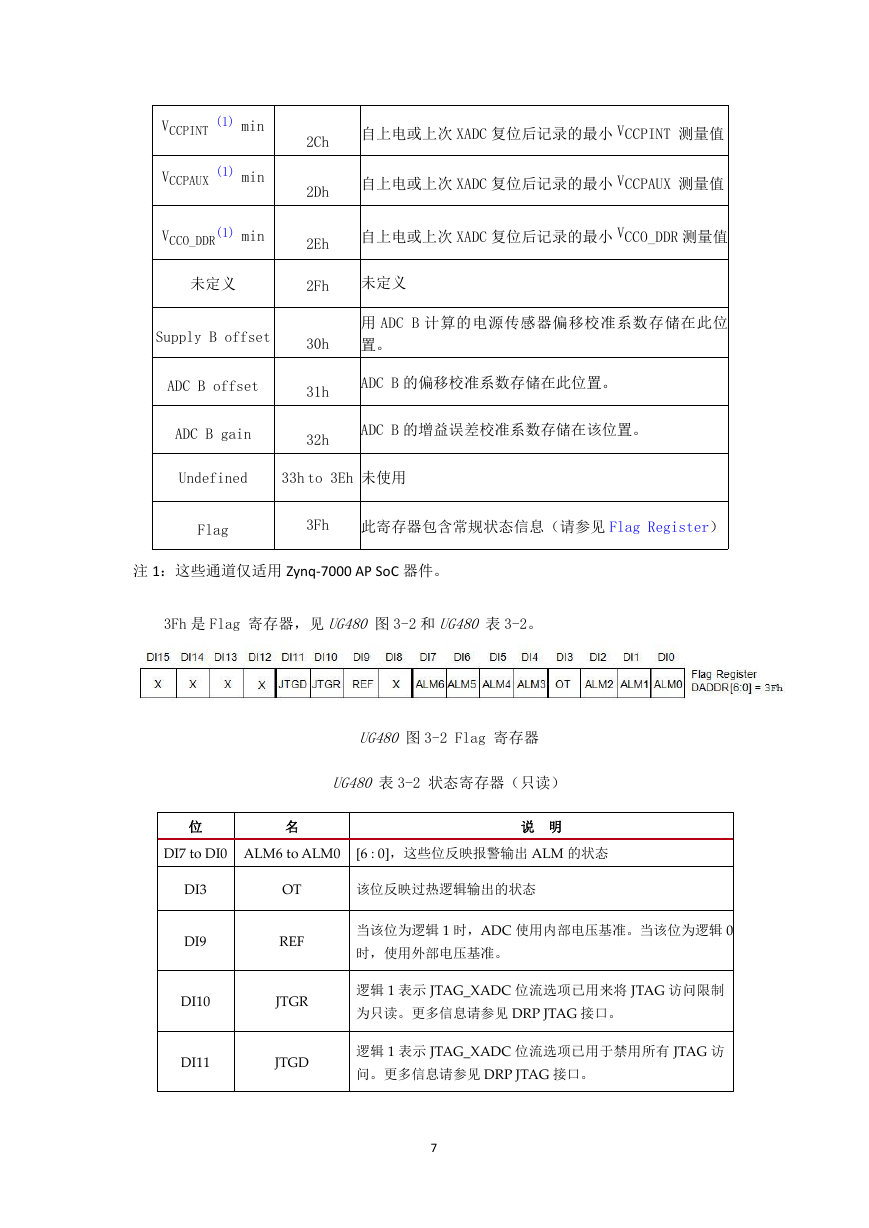

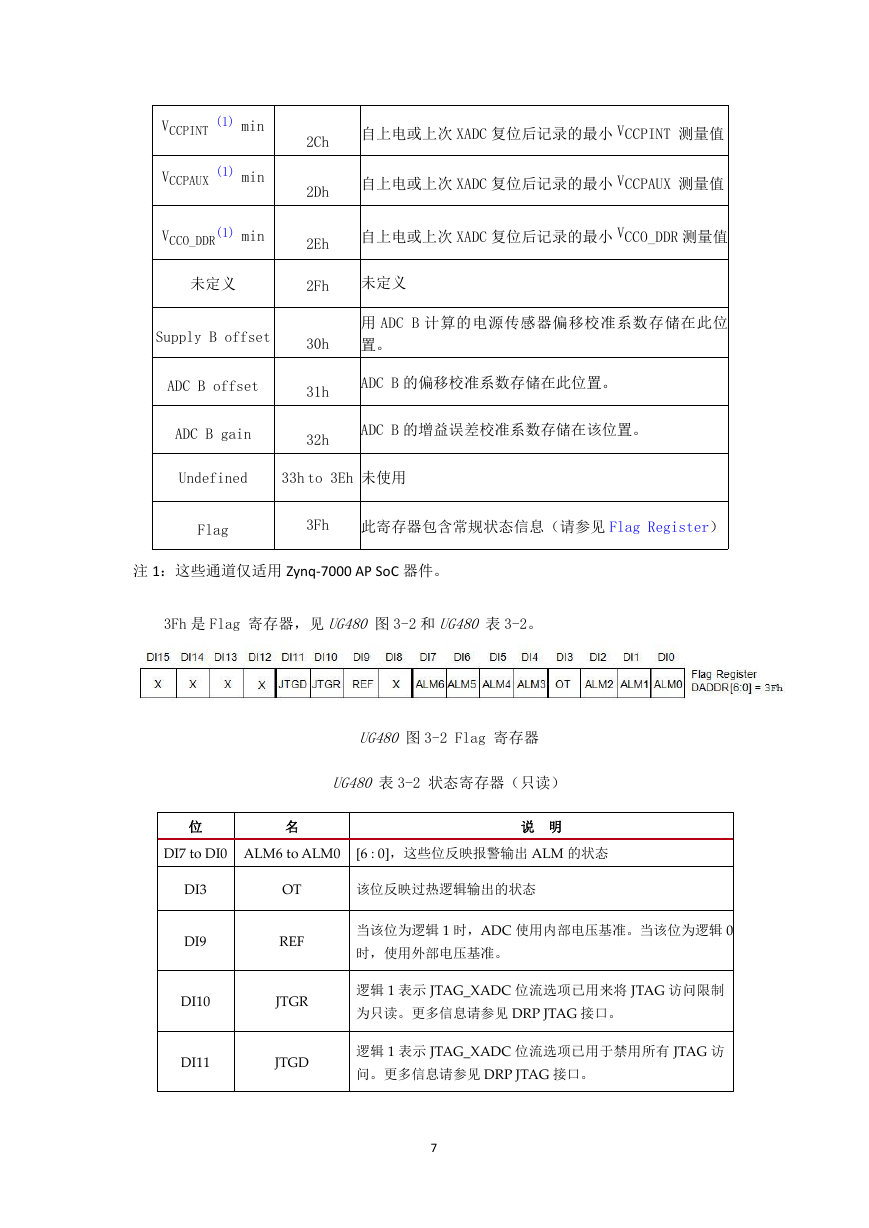

3Fh 是 Flag 寄存器,见 UG480 图 3-2 和 UG480 表 3-2。

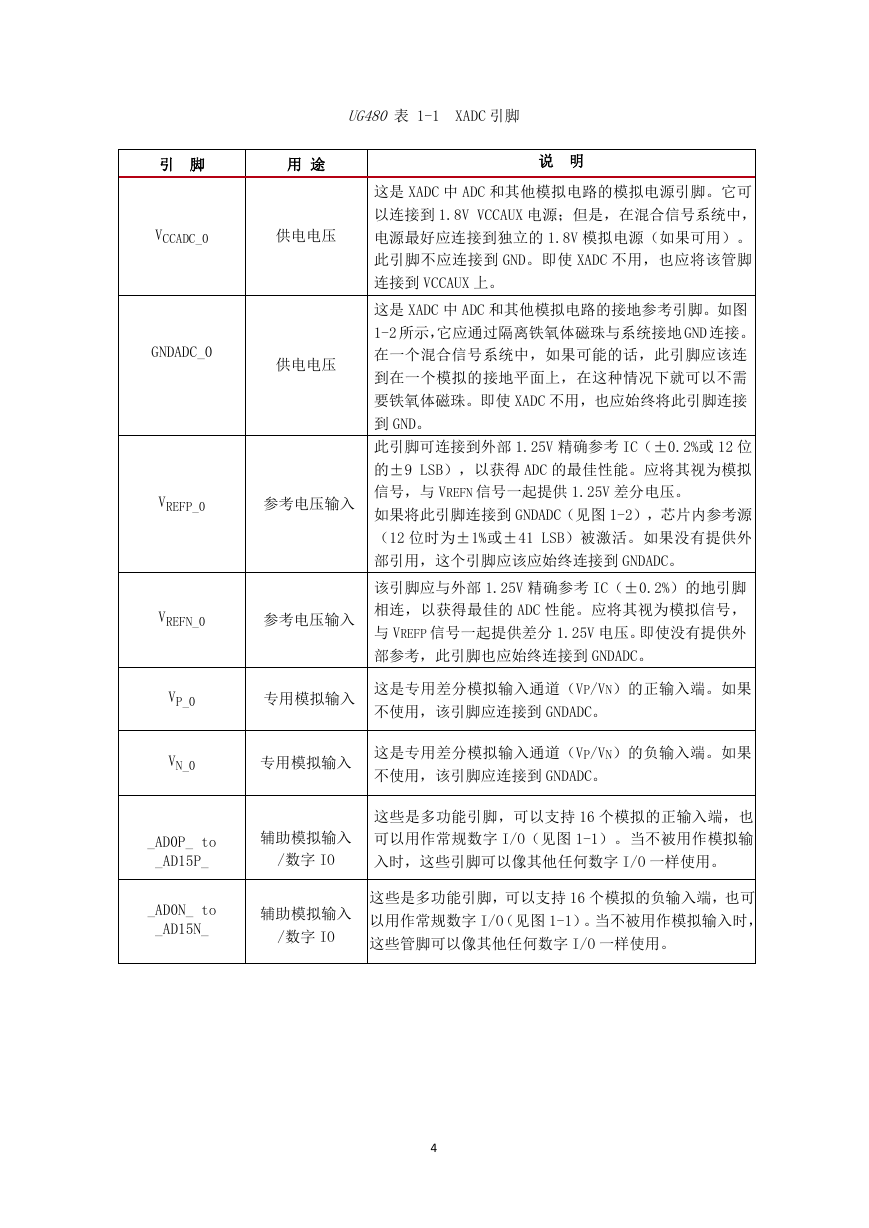

UG480 图 3-2 Flag 寄存器

UG480 表 3-2 状态寄存器(只读)

位

名

说 明

DI7 to DI0 ALM6 to ALM0

[6 : 0],这些位反映报警输出 ALM 的状态

DI3

DI9

OT

REF

该位反映过热逻辑输出的状态

当该位为逻辑 1 时,ADC 使用内部电压基准。当该位为逻辑 0

时,使用外部电压基准。

DI10

JTGR

逻辑 1 表示 JTAG_XADC 位流选项已用来将 JTAG 访问限制

为只读。更多信息请参见 DRP JTAG 接口。

DI11

JTGD

逻辑 1 表示 JTAG_XADC 位流选项已用于禁用所有 JTAG 访

问。更多信息请参见 DRP JTAG 接口。

7

�

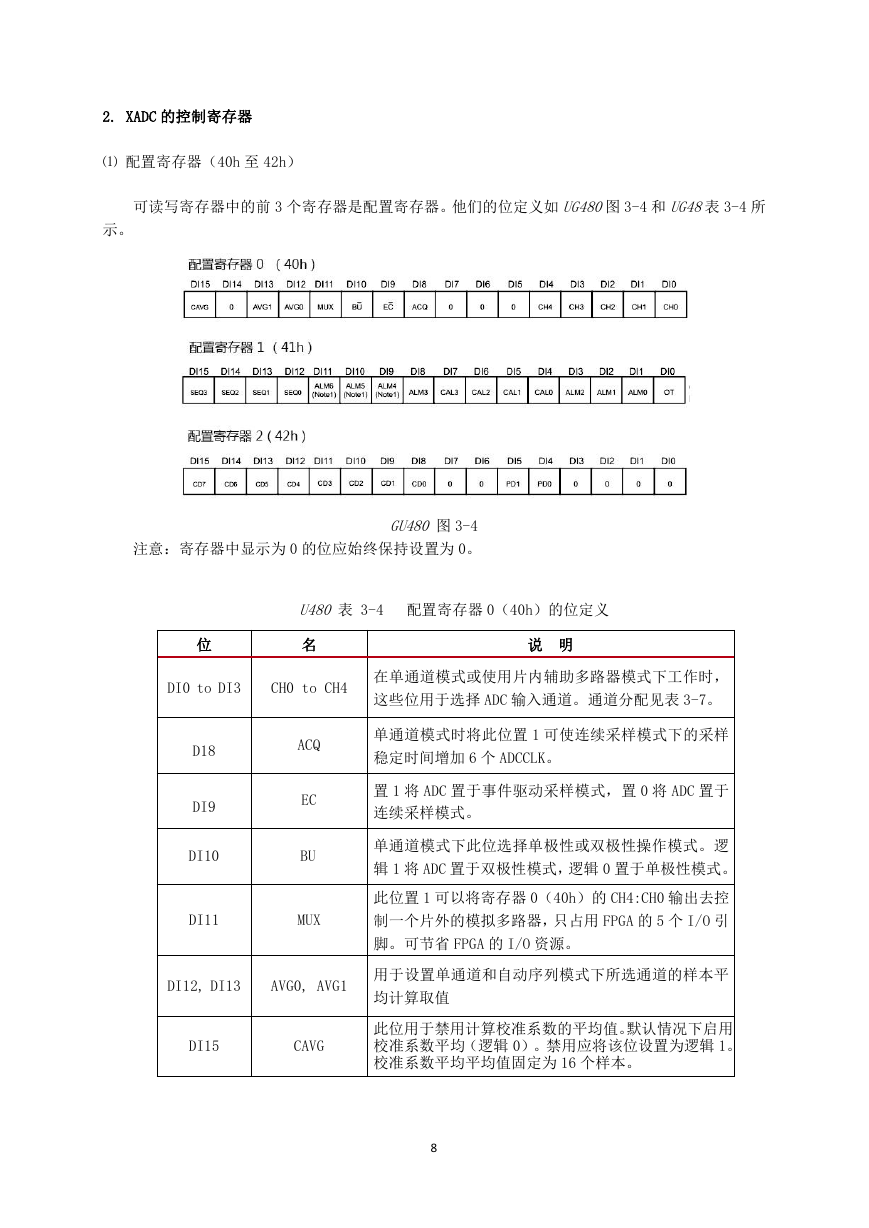

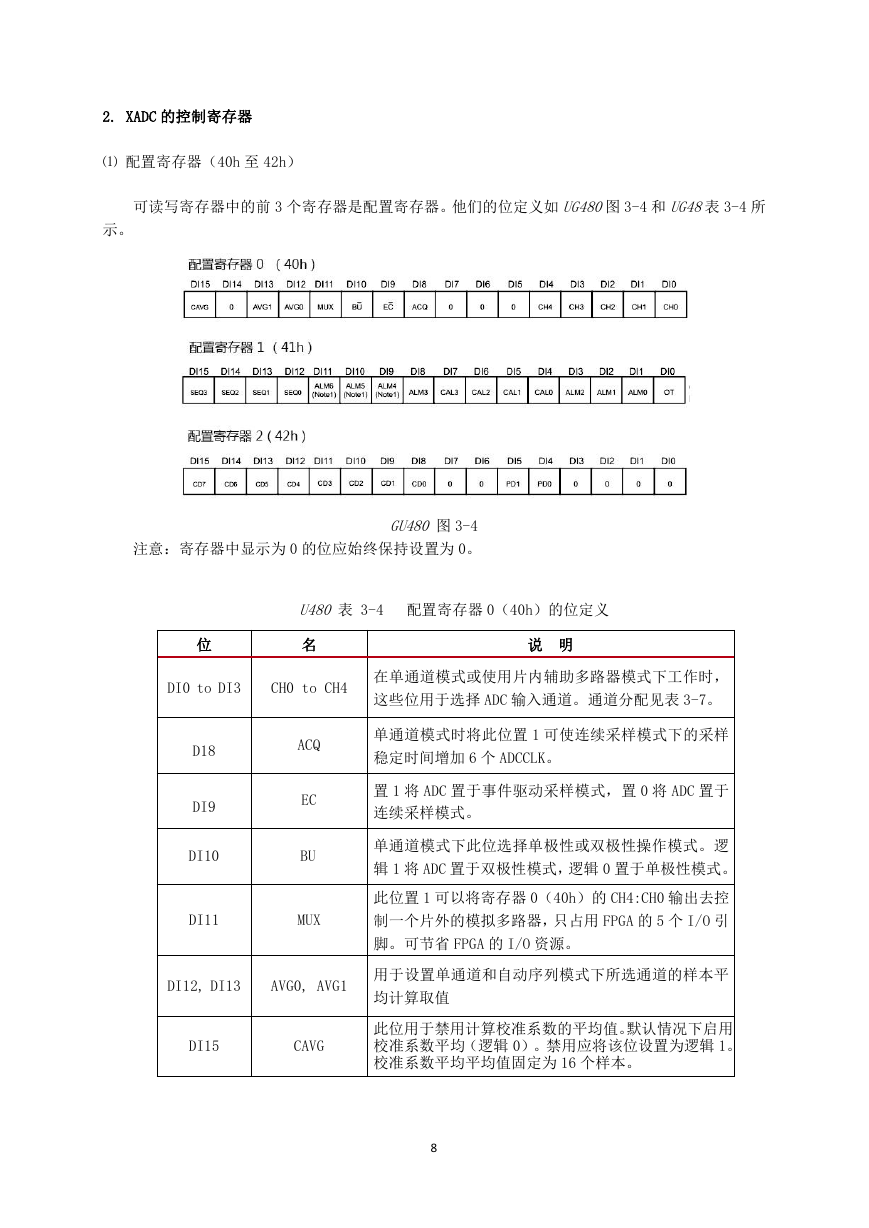

2. XADC 的控制寄存器

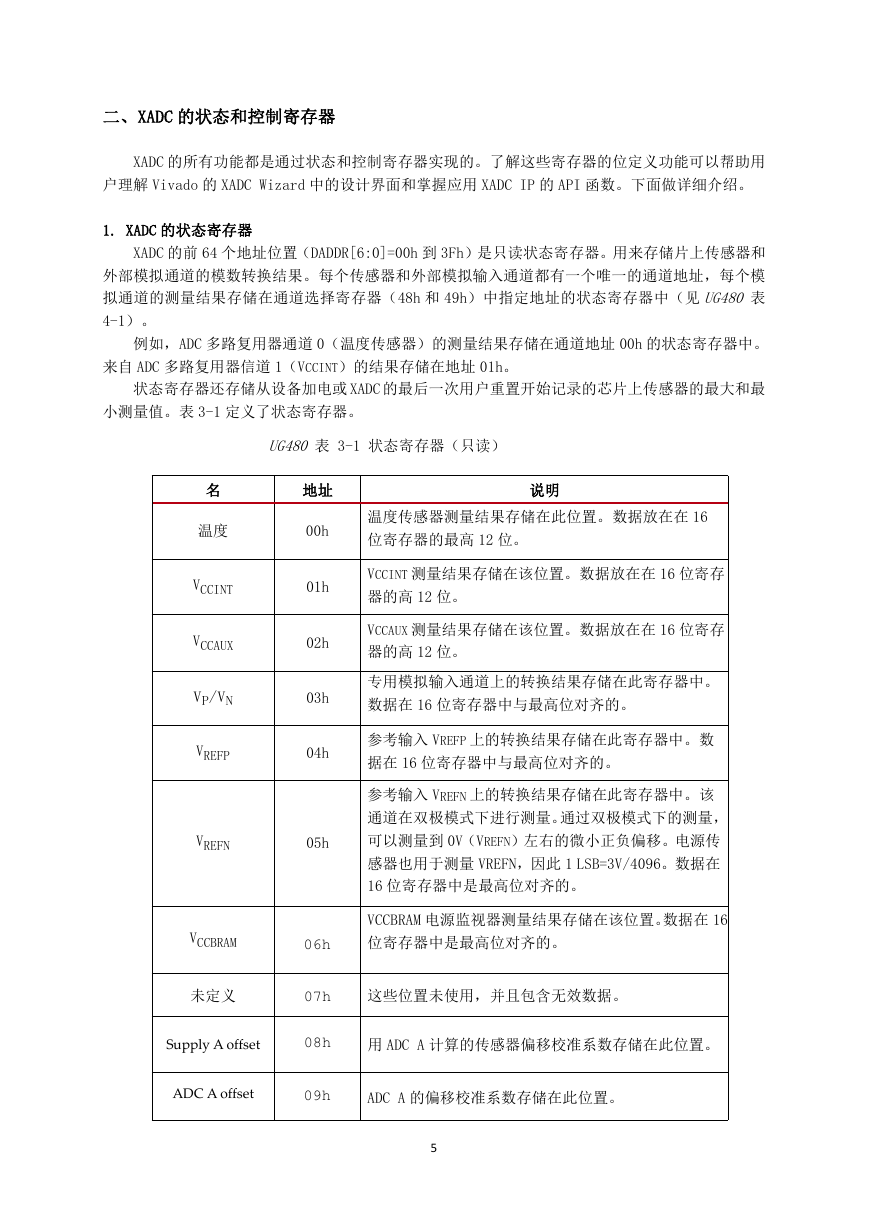

⑴ 配置寄存器(40h 至 42h)

可读写寄存器中的前 3 个寄存器是配置寄存器。他们的位定义如 UG480图 3-4 和 UG48表 3-4 所

示。

GU480 图 3-4

注意:寄存器中显示为 0 的位应始终保持设置为 0。

U480 表 3-4 配置寄存器 0(40h)的位定义

位

名

说 明

DI0 to DI3

CH0 to CH4

在单通道模式或使用片内辅助多路器模式下工作时,

这些位用于选择 ADC 输入通道。通道分配见表 3-7。

D18

DI9

DI10

ACQ

EC

BU

DI11

MUX

单通道模式时将此位置 1 可使连续采样模式下的采样

稳定时间增加 6 个 ADCCLK。

置 1 将 ADC 置于事件驱动采样模式,置 0 将 ADC 置于

连续采样模式。

单通道模式下此位选择单极性或双极性操作模式。逻

辑 1 将 ADC 置于双极性模式,逻辑 0 置于单极性模式。

此位置 1 可以将寄存器 0(40h)的 CH4:CH0 输出去控

制一个片外的模拟多路器,只占用 FPGA 的 5 个 I/O 引

脚。可节省 FPGA 的 I/O 资源。

DI12, DI13

AVG0, AVG1

用于设置单通道和自动序列模式下所选通道的样本平

均计算取值

DI15

CAVG

此位用于禁用计算校准系数的平均值。默认情况下启用

校准系数平均(逻辑 0)。禁用应将该位设置为逻辑 1。

校准系数平均平均值固定为 16 个样本。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc