数字系统设计课程设计报告

( 2011 – 2012 年度第二学期)

题 目: 基于 FPGA 的 SOPC 交通灯实时控制系统设计

学 号:

学生姓名:

成 绩:

日期:2012 年 6 月 3 日

�

交通灯实时控制系统设计报告

【摘要】分析了现代城市交通控制与管理问题的现状,结合城乡交通的实际情况阐述了

交通灯控制系统的工作原理,给出了一种简单实用的城市交通灯控制系统的实现方案,

即基于 FPGA 的 SOPC 交通灯实时控制系统设计。

一、设计要求

1、显示交通控制灯

使用开发板上的 3 个 LED 分别代表红、绿、黄三个灯。

2、数字显示

交通灯要有数字显示,作为时间提示,以便人们更直观地把握时间。其中绿灯亮 30

秒,黄灯亮 5 秒,红灯亮 30 秒,如此循环。每个灯亮的时候,数码管显示该灯亮的剩

余时间,即数码管倒计时显示。

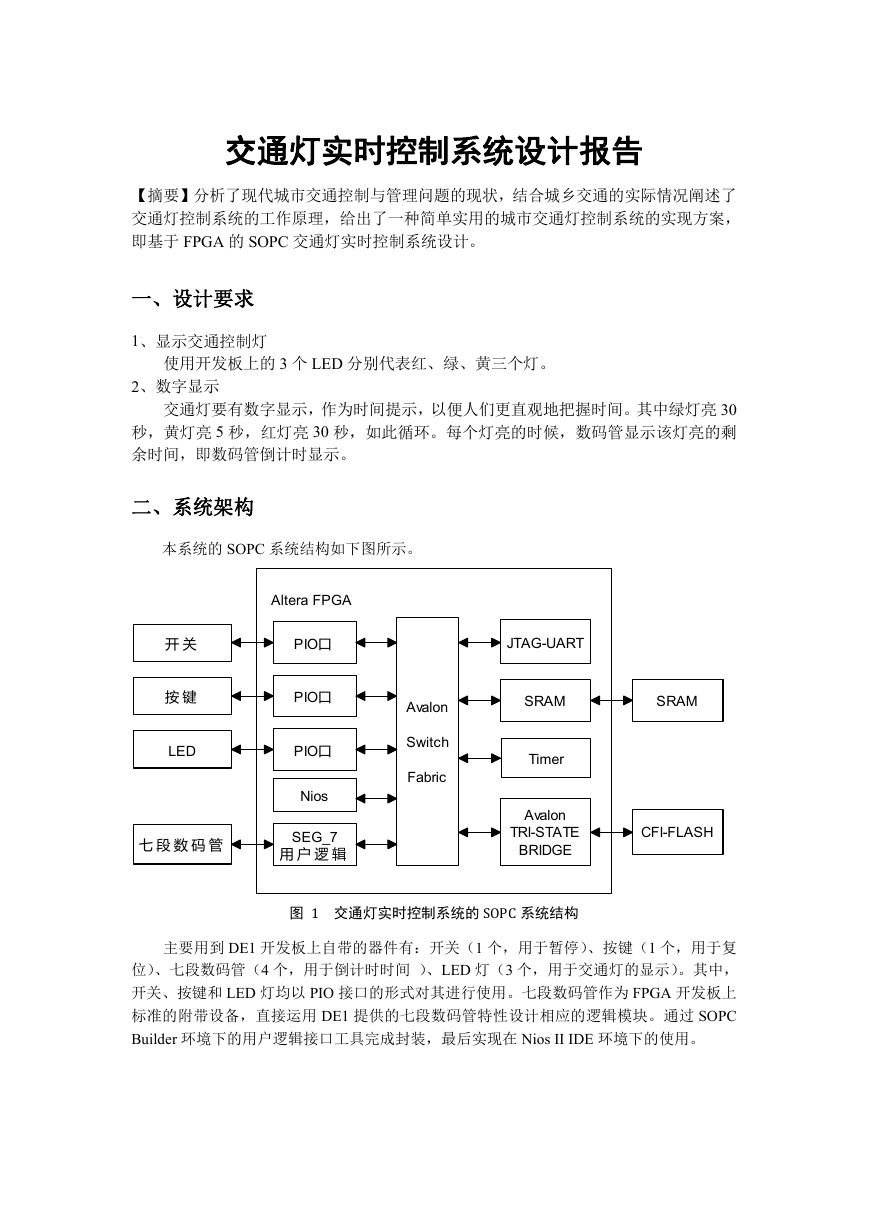

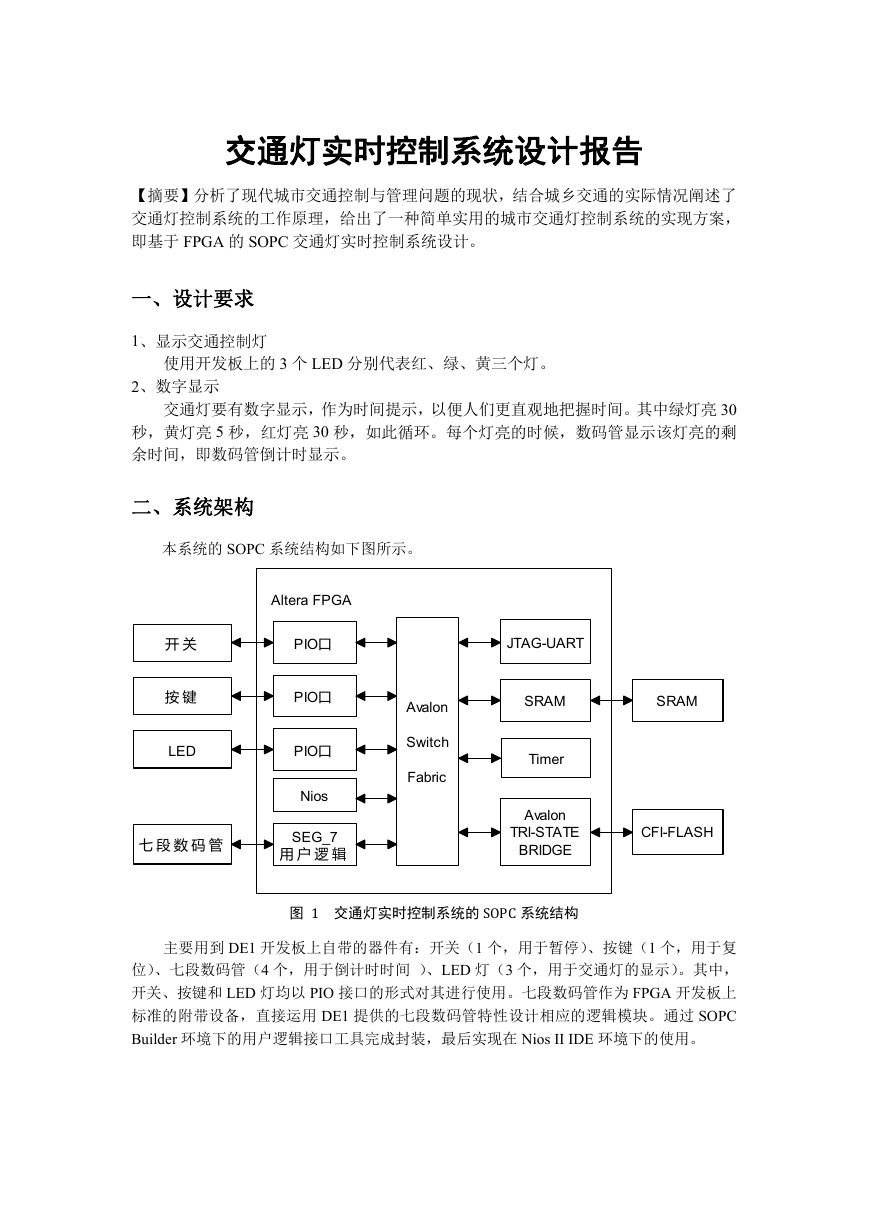

二、系统架构

本系统的 SOPC 系统结构如下图所示。

开 关

按 键

LED

Altera FPGA

PIO口

PIO口

PIO口

Nios

Avalon

Switch

Fabric

七 段 数 码 管

SEG_7

用 户 逻 辑

JTAG-UART

SRAM

Timer

Avalon

TRI-STATE

BRIDGE

SRAM

CFI-FLASH

图1 交通灯实时控制系统的SOPC 系统结构

主要用到 DE1 开发板上自带的器件有:开关(1 个,用于暂停)、按键(1 个,用于复

位)、七段数码管(4 个,用于倒计时时间 )、LED 灯(3 个,用于交通灯的显示)。其中,

开关、按键和 LED 灯均以 PIO 接口的形式对其进行使用。七段数码管作为 FPGA 开发板上

标准的附带设备,直接运用 DE1 提供的七段数码管特性设计相应的逻辑模块。通过 SOPC

Builder 环境下的用户逻辑接口工具完成封装,最后实现在 Nios II IDE 环境下的使用。

�

三、硬件设计

1、创建 Quartus II 工程

打开 Quartus II 开发环境,在新建工程的向导中,选择 DE1 开发板提供的 FPGA 芯片

Cyclone II 2C20F484C7。

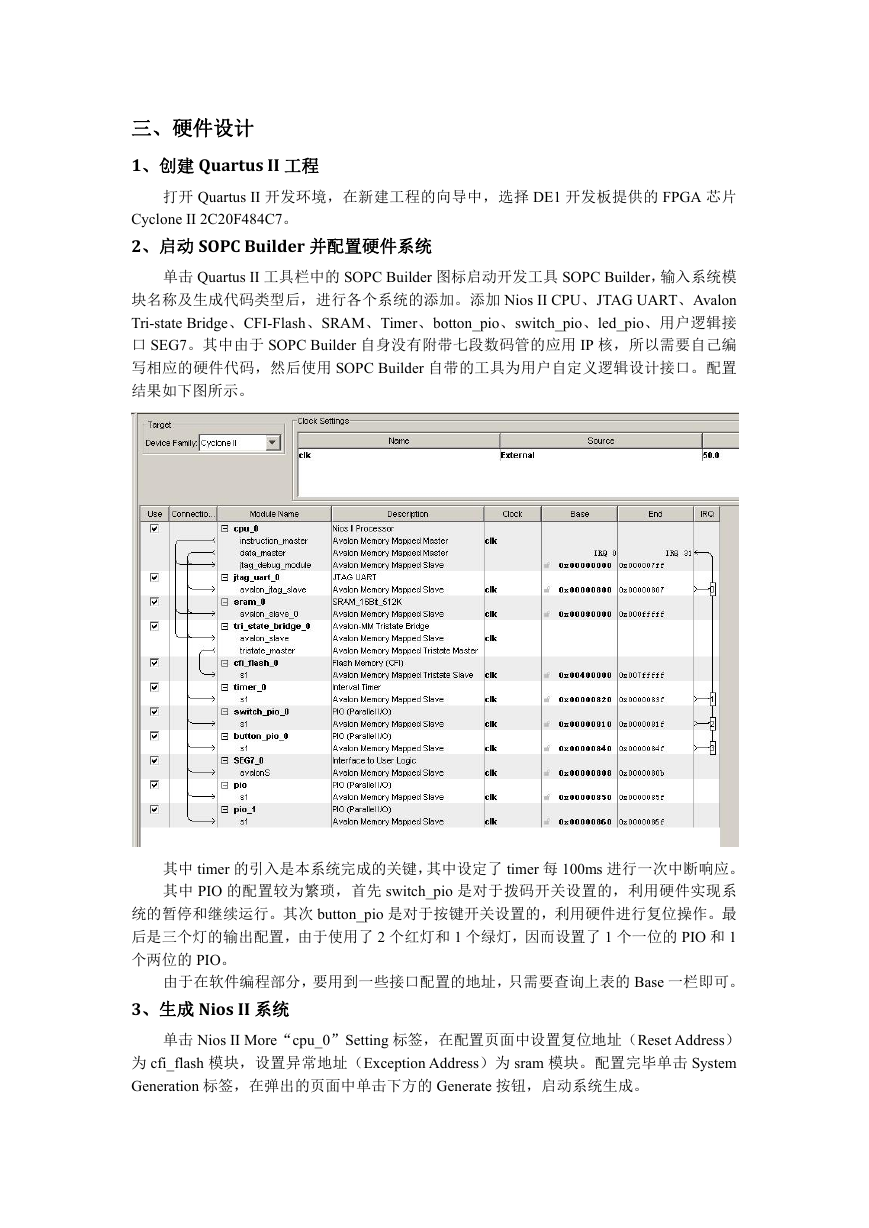

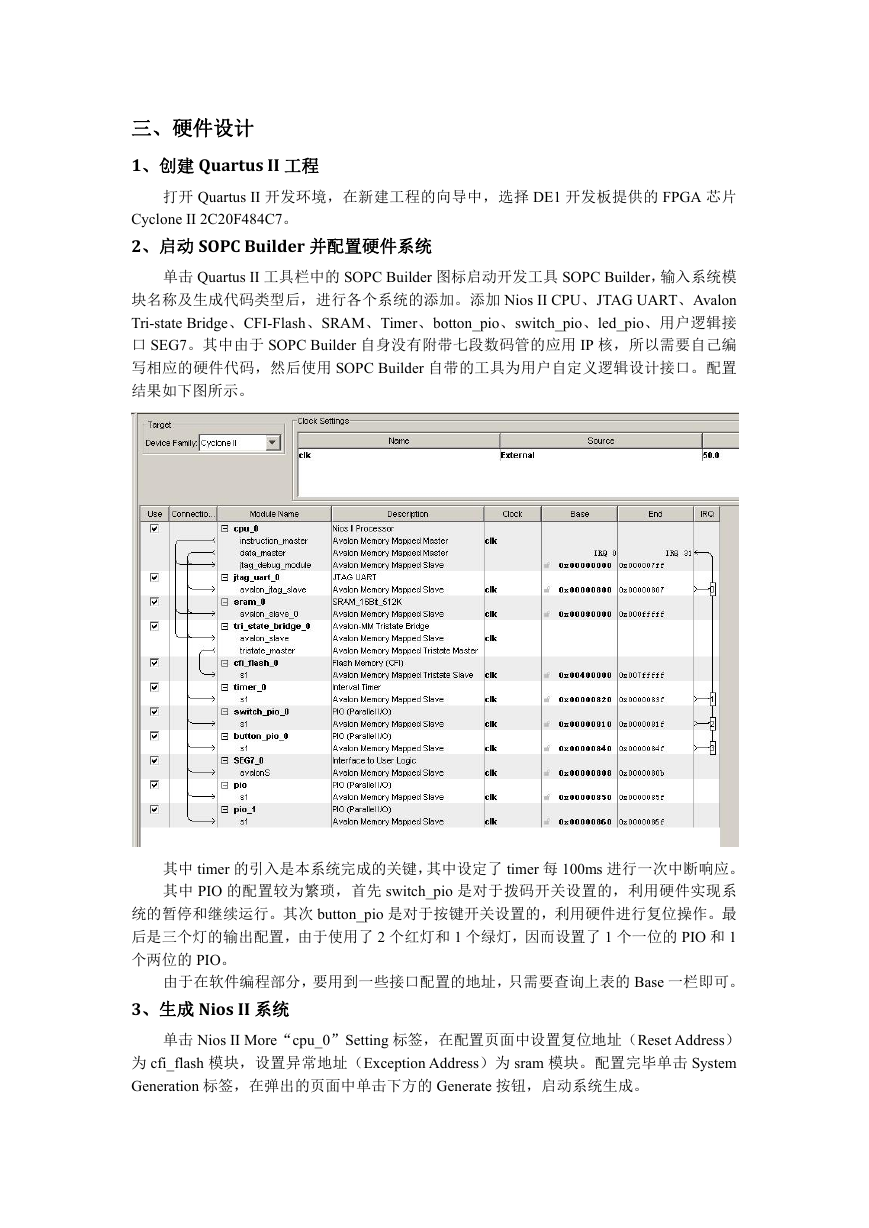

2、启动 SOPC Builder 并配置硬件系统

单击 Quartus II 工具栏中的 SOPC Builder 图标启动开发工具 SOPC Builder,输入系统模

块名称及生成代码类型后,进行各个系统的添加。添加 Nios II CPU、JTAG UART、Avalon

Tri-state Bridge、CFI-Flash、SRAM、Timer、botton_pio、switch_pio、led_pio、用户逻辑接

口 SEG7。其中由于 SOPC Builder 自身没有附带七段数码管的应用 IP 核,所以需要自己编

写相应的硬件代码,然后使用 SOPC Builder 自带的工具为用户自定义逻辑设计接口。配置

结果如下图所示。

其中 timer 的引入是本系统完成的关键,其中设定了 timer 每 100ms 进行一次中断响应。

其中 PIO 的配置较为繁琐,首先 switch_pio 是对于拨码开关设置的,利用硬件实现系

统的暂停和继续运行。其次 button_pio 是对于按键开关设置的,利用硬件进行复位操作。最

后是三个灯的输出配置,由于使用了 2 个红灯和 1 个绿灯,因而设置了 1 个一位的 PIO 和 1

个两位的 PIO。

由于在软件编程部分,要用到一些接口配置的地址,只需要查询上表的 Base 一栏即可。

3、生成 Nios II 系统

单击 Nios II More“cpu_0”Setting 标签,在配置页面中设置复位地址(Reset Address)

为 cfi_flash 模块,设置异常地址(Exception Address)为 sram 模块。配置完毕单击 System

Generation 标签,在弹出的页面中单击下方的 Generate 按钮,启动系统生成。

�

4、集成 Nios II 系统到 Quartus II 工程

首先在 Quartus II 环境下创建一个顶层模块,创建一个 Verilog HDL 文件作为顶层并打

开编辑器。在顶层文件中输入声明开发板所支持的所有信号引脚的 Verilog 代码。在工程文

件夹中找到由 SOPC Builder 生成的 Nios II 系统代码文件,在其中找到系统模块描述的代码,

将该部分代码拷贝到顶层文件中,并使用之前声明的信号引脚对模块进行实例化。最后对

FPGA 器件引脚进行锁定,编译 Quartus II 工程,生成最后的硬件下载文件。

四、软件设计

1、启动 Nios II IDE 并构建工程

启 动 Nios II IDE 新 建 工 程 , 在 新 建 工 程 的 对 话 框 中 选 择 Altera Nios II C/C++

Application,在弹出的对话框中进行配置。其中,在 SOPC Builder System 中打开合适的 Nios

II 系统 ptf 文件,选择 Hello World 模板,新工程配置结束。点击 Finish 按钮,生成工程。

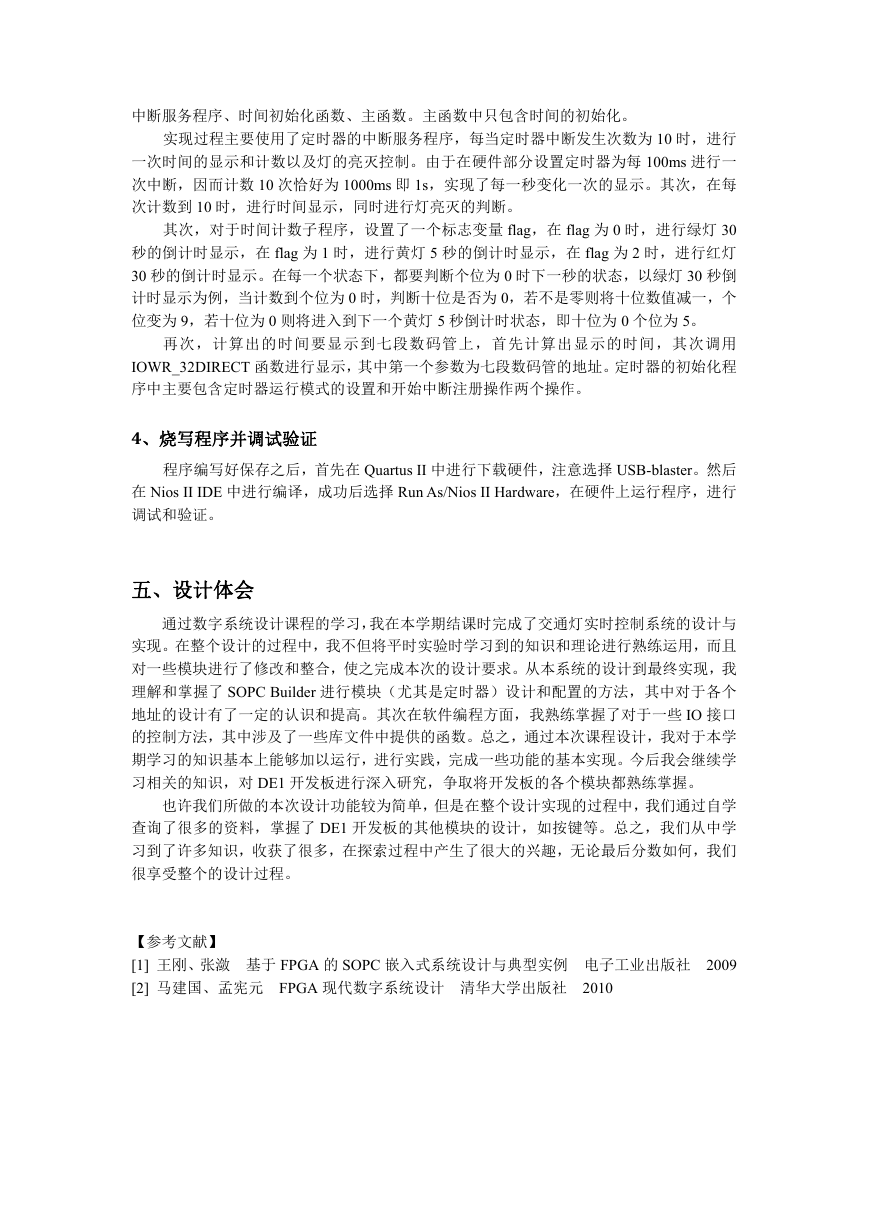

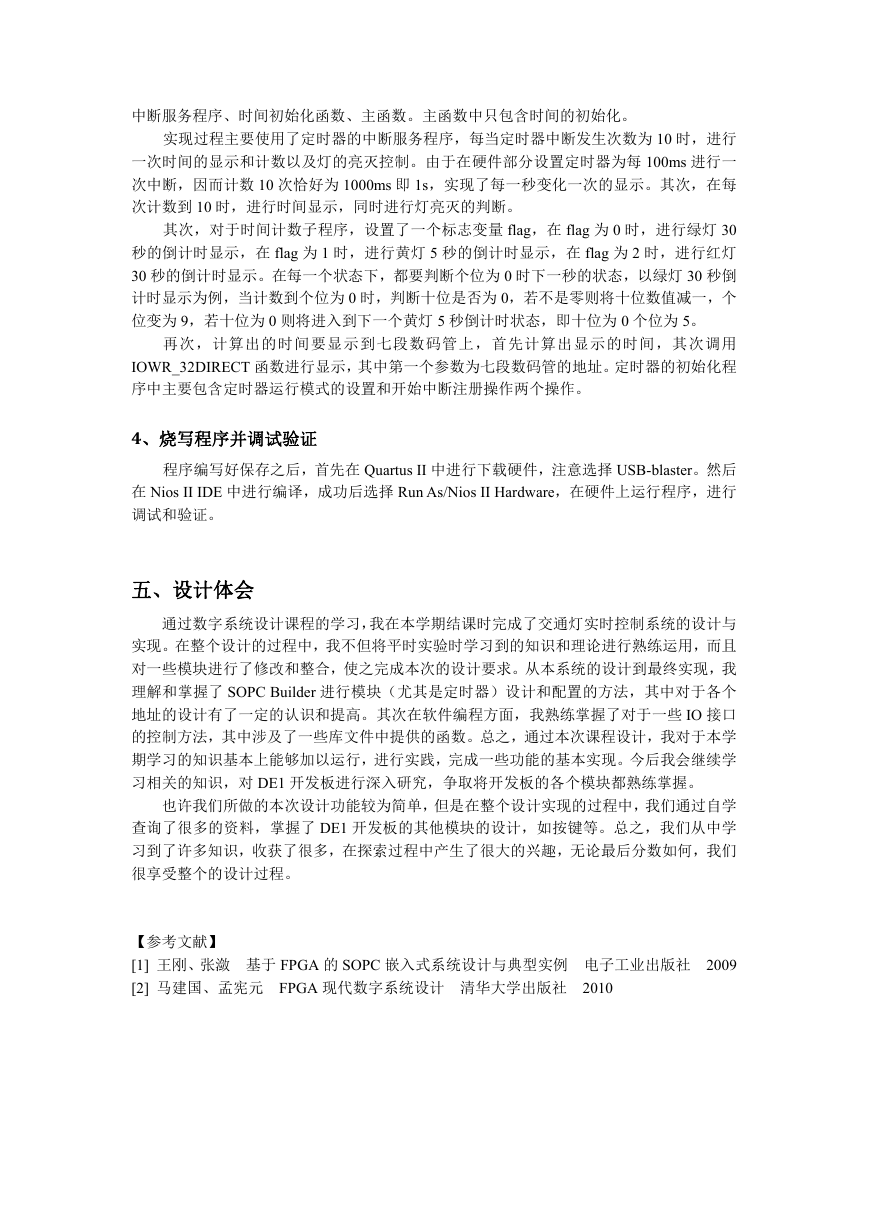

2、程序设计流程图:

开 始

时 间 初 始 化

调 用 时 间 按 初 始 化 函 数

进 入 中 断 服 务 子 程 序

开 始

定 时 器 运 行 ( 一 直 运 行 )

定 义 变 量 count, 初 值 为 0

定 时 器 是 否 到 100ms

NO

YES

中 断 服 务 子 程 序

返 回 中 断 服 务 程 序 调 用 点

count++

count==10?

YES

NO

时 间 显 示

调 用 时 间 实 现 函 数

时 间 计 算

调 用 时 间 计 算 函 数

LED灯 亮 灭 的 控 制

结 束

3、编写代码

根据设计要求,源代码中包含时间计数函数、时间显示在七段数码管上的函数、timer

�

中断服务程序、时间初始化函数、主函数。主函数中只包含时间的初始化。

实现过程主要使用了定时器的中断服务程序,每当定时器中断发生次数为 10 时,进行

一次时间的显示和计数以及灯的亮灭控制。由于在硬件部分设置定时器为每 100ms 进行一

次中断,因而计数 10 次恰好为 1000ms 即 1s,实现了每一秒变化一次的显示。其次,在每

次计数到 10 时,进行时间显示,同时进行灯亮灭的判断。

其次,对于时间计数子程序,设置了一个标志变量 flag,在 flag 为 0 时,进行绿灯 30

秒的倒计时显示,在 flag 为 1 时,进行黄灯 5 秒的倒计时显示,在 flag 为 2 时,进行红灯

30 秒的倒计时显示。在每一个状态下,都要判断个位为 0 时下一秒的状态,以绿灯 30 秒倒

计时显示为例,当计数到个位为 0 时,判断十位是否为 0,若不是零则将十位数值减一,个

位变为 9,若十位为 0 则将进入到下一个黄灯 5 秒倒计时状态,即十位为 0 个位为 5。

再次,计算出的时间要显示到七段数码管上,首先计算出显示的时间,其次调用

IOWR_32DIRECT 函数进行显示,其中第一个参数为七段数码管的地址。定时器的初始化程

序中主要包含定时器运行模式的设置和开始中断注册操作两个操作。

4、烧写程序并调试验证

程序编写好保存之后,首先在 Quartus II 中进行下载硬件,注意选择 USB-blaster。然后

在 Nios II IDE 中进行编译,成功后选择 Run As/Nios II Hardware,在硬件上运行程序,进行

调试和验证。

五、设计体会

通过数字系统设计课程的学习,我在本学期结课时完成了交通灯实时控制系统的设计与

实现。在整个设计的过程中,我不但将平时实验时学习到的知识和理论进行熟练运用,而且

对一些模块进行了修改和整合,使之完成本次的设计要求。从本系统的设计到最终实现,我

理解和掌握了 SOPC Builder 进行模块(尤其是定时器)设计和配置的方法,其中对于各个

地址的设计有了一定的认识和提高。其次在软件编程方面,我熟练掌握了对于一些 IO 接口

的控制方法,其中涉及了一些库文件中提供的函数。总之,通过本次课程设计,我对于本学

期学习的知识基本上能够加以运行,进行实践,完成一些功能的基本实现。今后我会继续学

习相关的知识,对 DE1 开发板进行深入研究,争取将开发板的各个模块都熟练掌握。

也许我们所做的本次设计功能较为简单,但是在整个设计实现的过程中,我们通过自学

查询了很多的资料,掌握了 DE1 开发板的其他模块的设计,如按键等。总之,我们从中学

习到了许多知识,收获了很多,在探索过程中产生了很大的兴趣,无论最后分数如何,我们

很享受整个的设计过程。

【参考文献】

[1] 王刚、张潋 基于 FPGA 的 SOPC 嵌入式系统设计与典型实例 电子工业出版社 2009

[2] 马建国、孟宪元 FPGA 现代数字系统设计 清华大学出版社 2010

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc