数字逻辑实验指导书

曹广义, 肖敏

2016/10/10

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

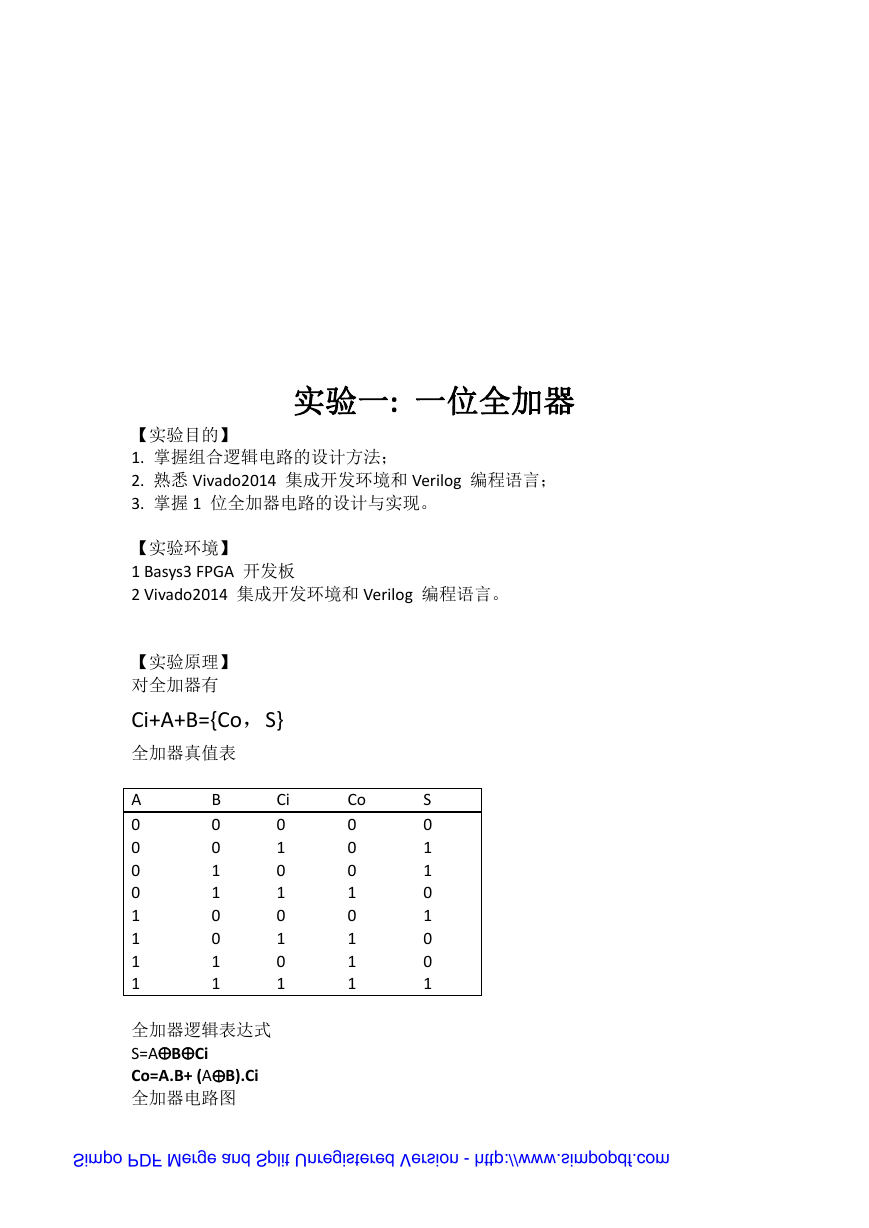

实验一: 一位全加器

【实验目的】

1. 掌握组合逻辑电路的设计方法;

2. 熟悉 Vivado2014 集成开发环境和 Verilog 编程语言;

3. 掌握 1 位全加器电路的设计与实现。

【实验环境】

1 Basys3 FPGA 开发板

2 Vivado2014 集成开发环境和 Verilog 编程语言。

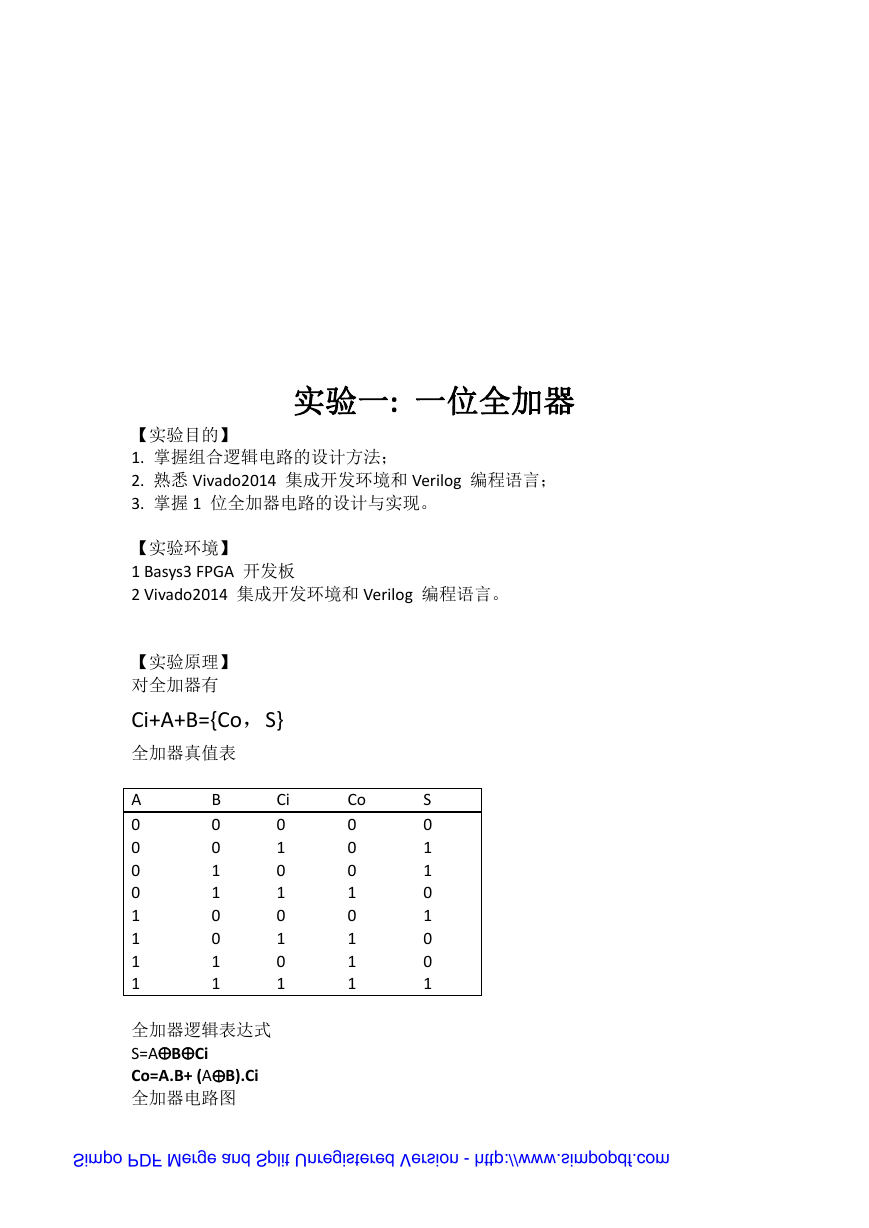

【实验原理】

对全加器有

Ci+A+B={Co,S}

全加器真值表

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

Ci

0

1

0

1

0

1

0

1

Co

0

0

0

1

0

1

1

1

S

0

1

1

0

1

0

0

1

全加器逻辑表达式

S=ABCi

Co=A.B+ (AB).Ci

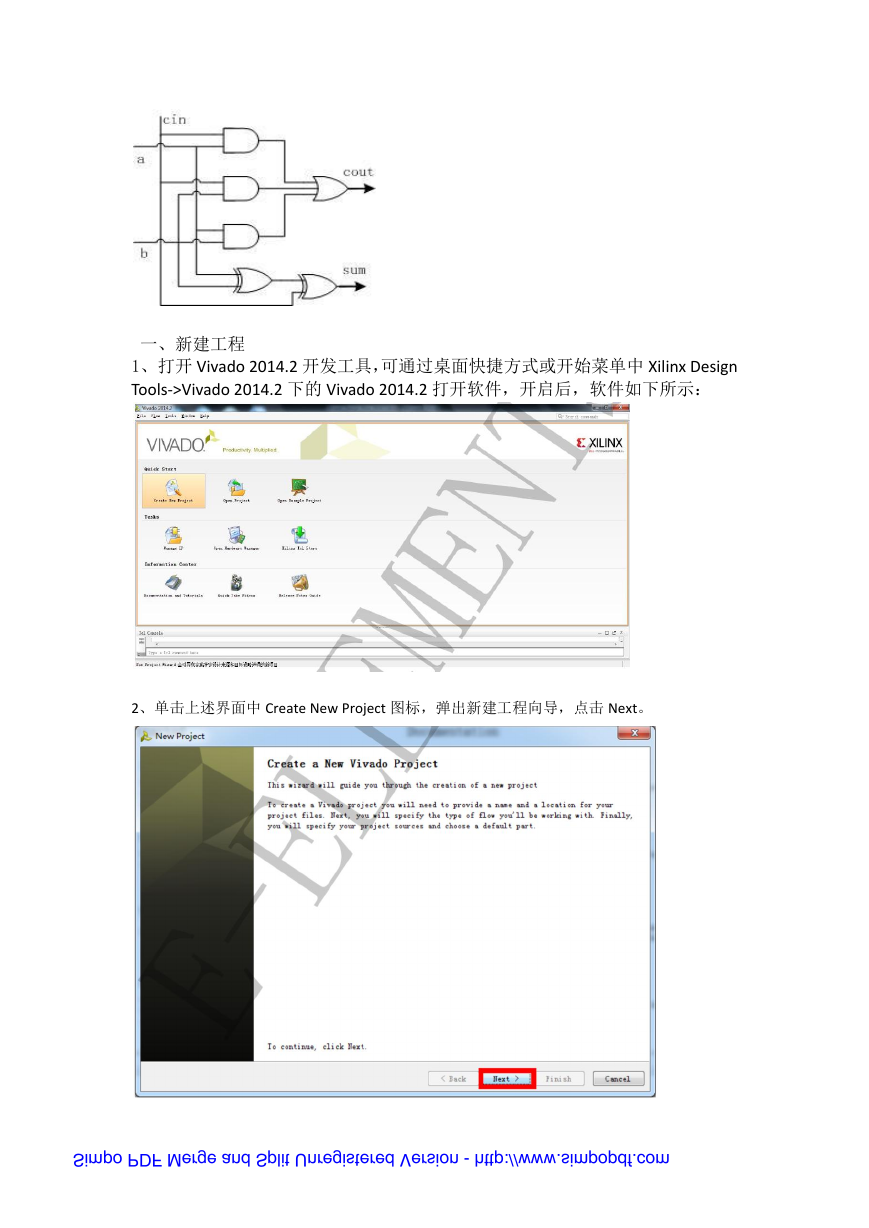

全加器电路图

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

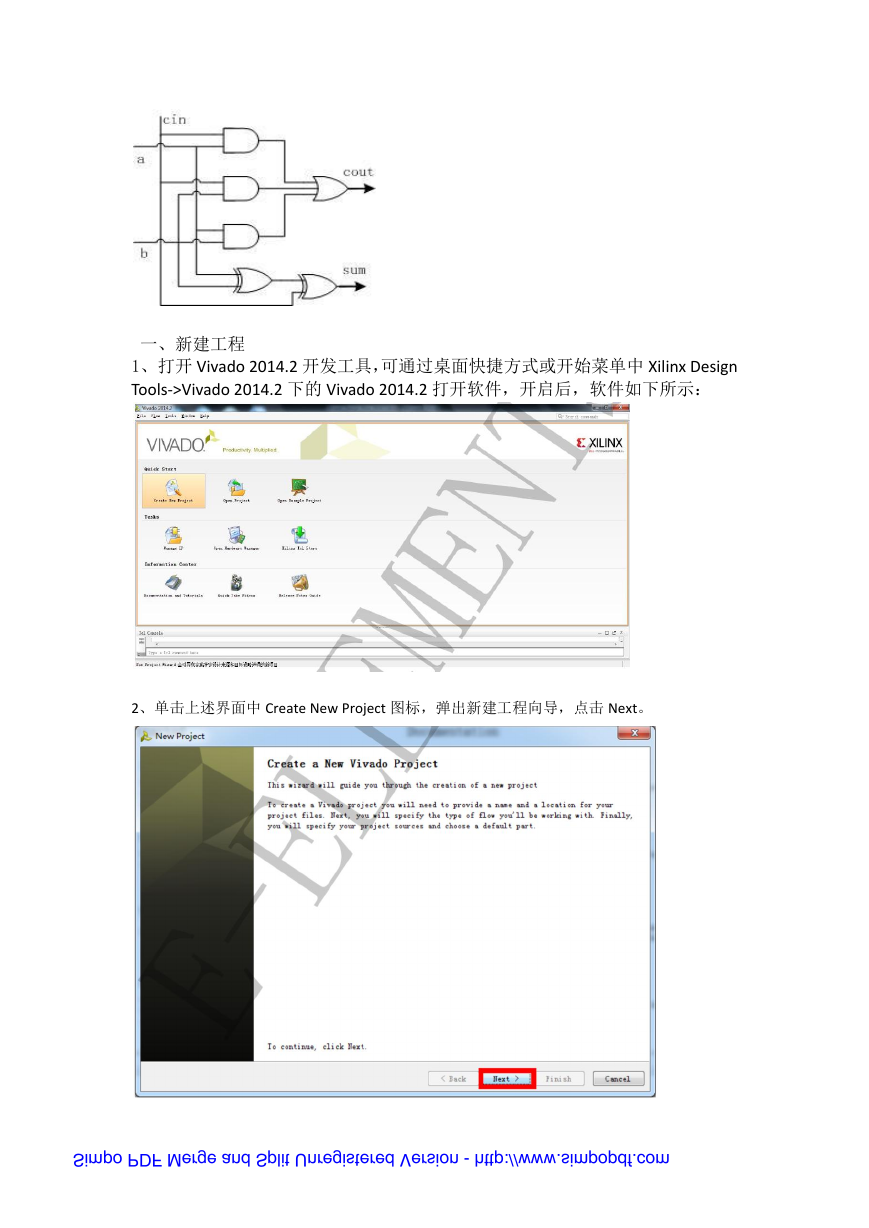

一、新建工程

1、打开 Vivado 2014.2 开发工具,可通过桌面快捷方式或开始菜单中 Xilinx Design

Tools->Vivado 2014.2 下的 Vivado 2014.2 打开软件,开启后,软件如下所示:

2、单击上述界面中 Create New Project 图标,弹出新建工程向导,点击 Next。

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

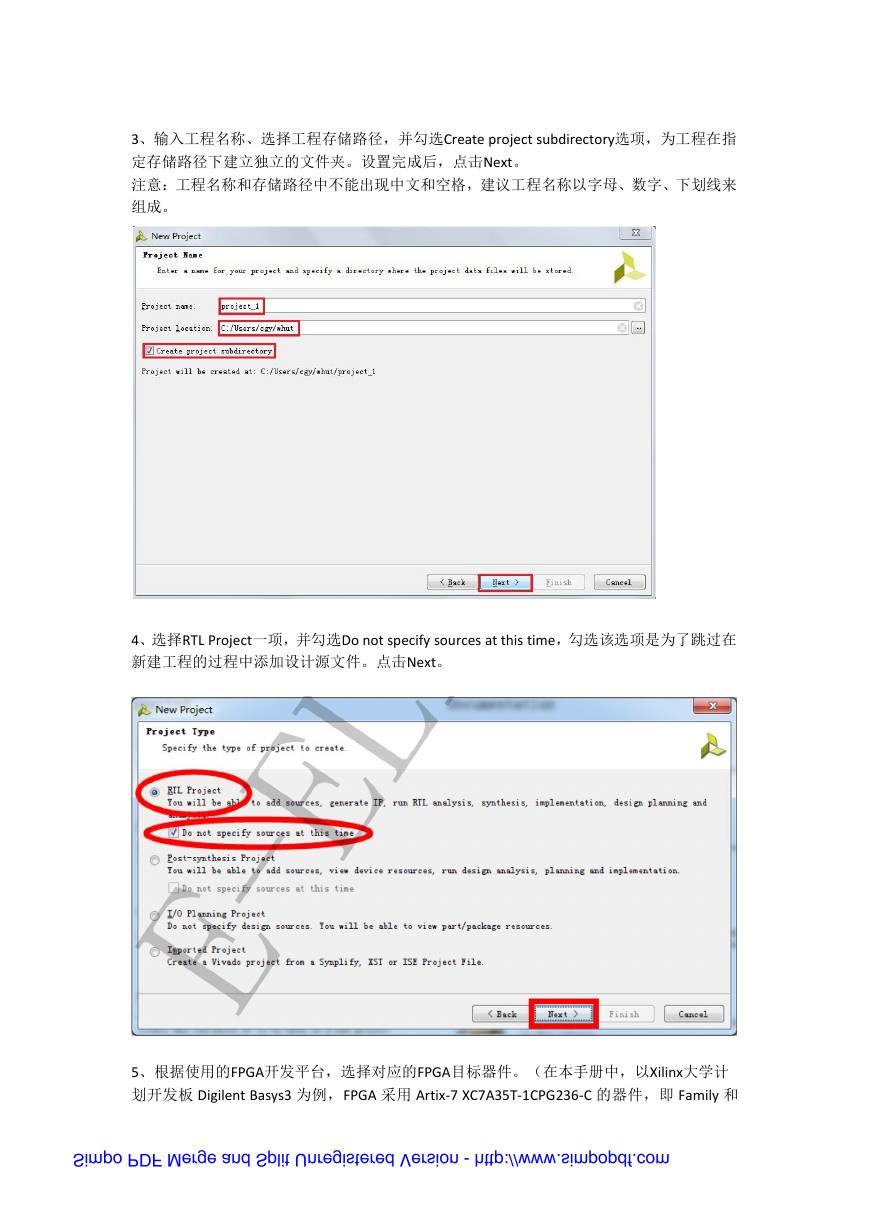

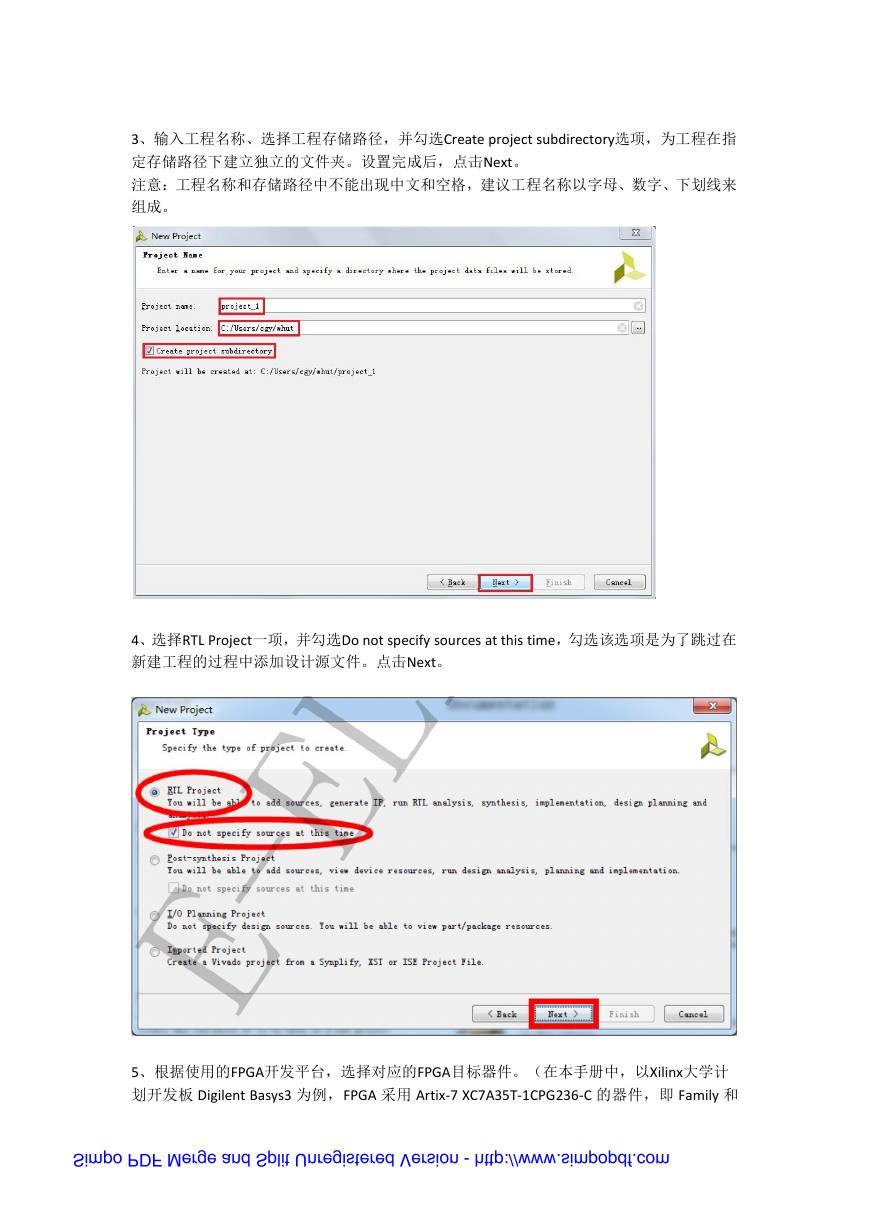

3、输入工程名称、选择工程存储路径,并勾选Create project subdirectory选项,为工程在指

定存储路径下建立独立的文件夹。设置完成后,点击Next。

注意:工程名称和存储路径中不能出现中文和空格,建议工程名称以字母、数字、下划线来

组成。

4、选择RTL Project一项,并勾选Do not specify sources at this time,勾选该选项是为了跳过在

新建工程的过程中添加设计源文件。点击Next。

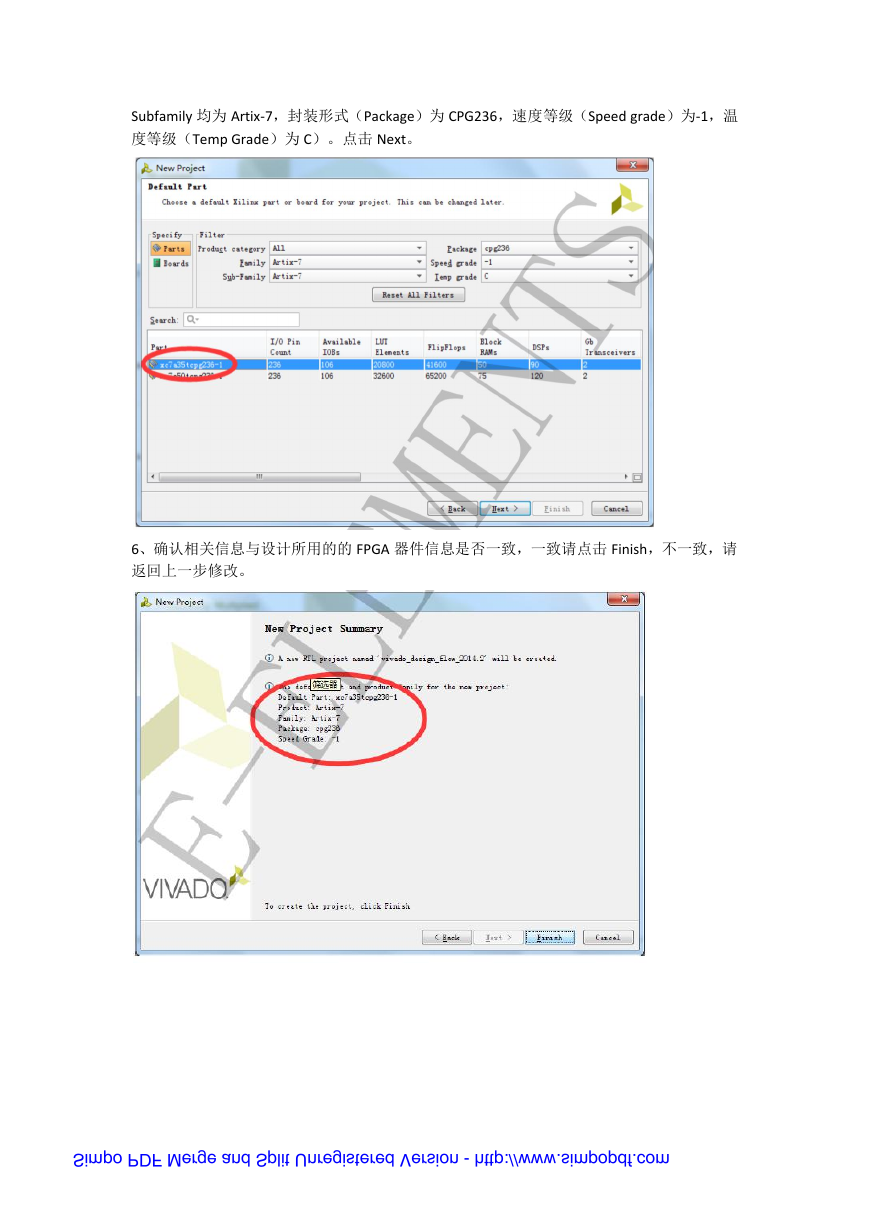

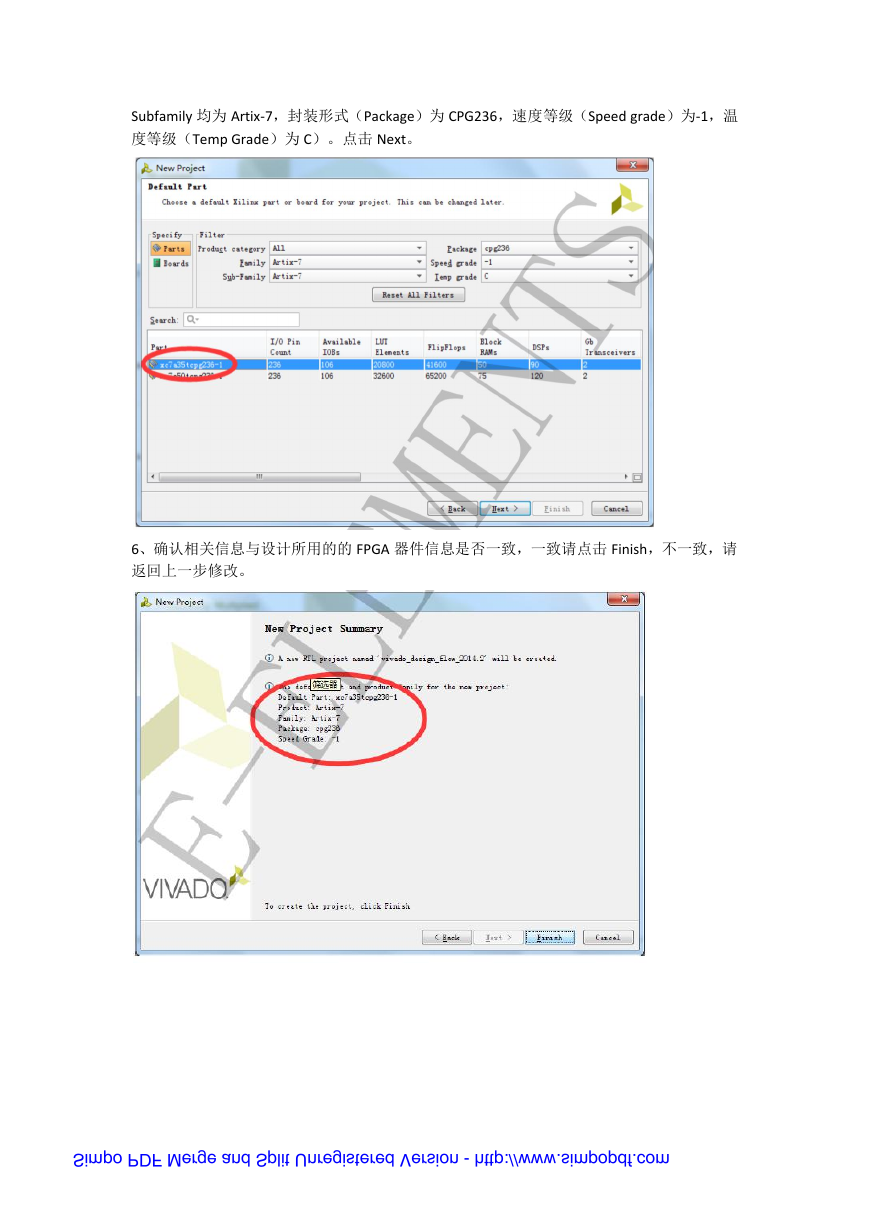

5、根据使用的FPGA开发平台,选择对应的FPGA目标器件。(在本手册中,以Xilinx大学计

划开发板 Digilent Basys3 为例,FPGA 采用 Artix-7 XC7A35T-1CPG236-C 的器件,即 Family 和

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

Subfamily 均为 Artix-7,封装形式(Package)为 CPG236,速度等级(Speed grade)为-1,温

度等级(Temp Grade)为 C)。点击 Next。

6、确认相关信息与设计所用的的 FPGA 器件信息是否一致,一致请点击 Finish,不一致,请

返回上一步修改。

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

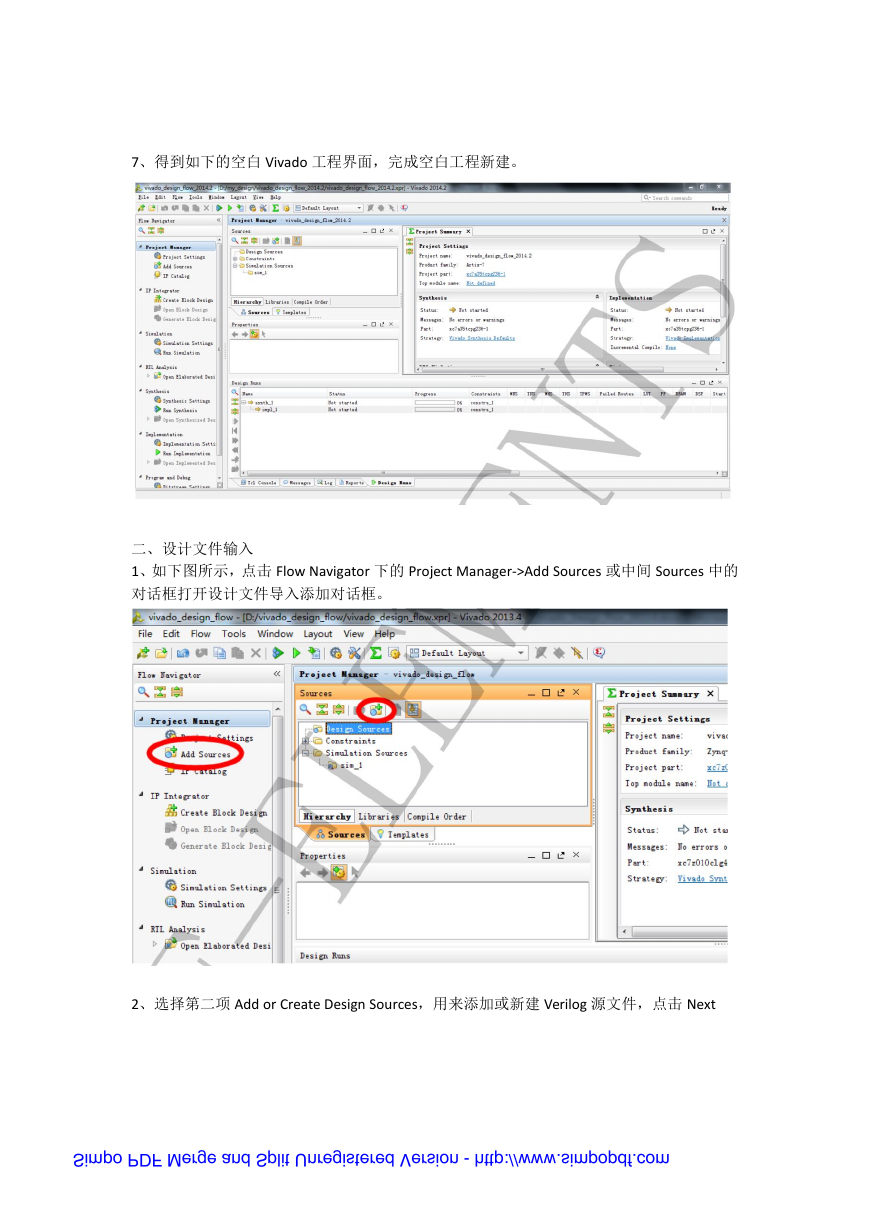

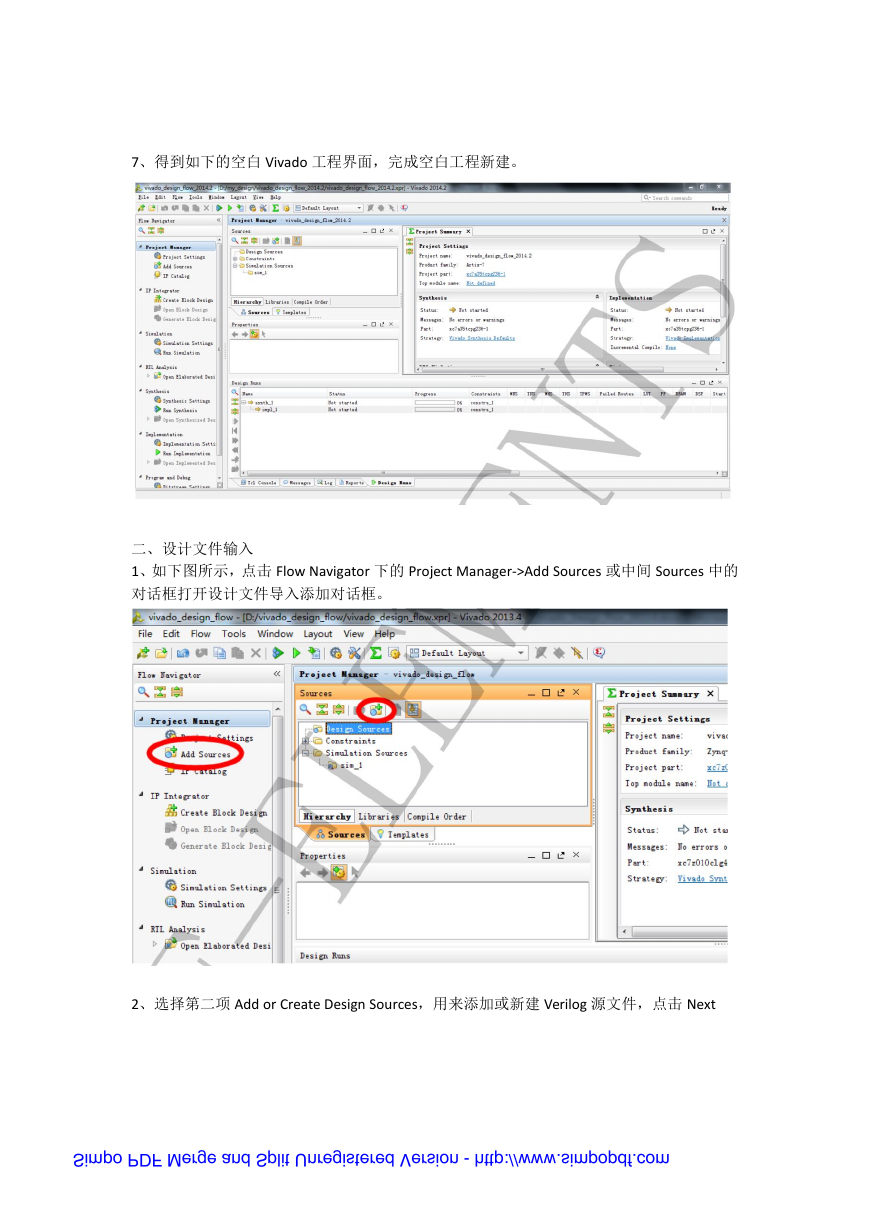

7、得到如下的空白 Vivado 工程界面,完成空白工程新建。

二、设计文件输入

1、如下图所示,点击 Flow Navigator 下的 Project Manager->Add Sources 或中间 Sources 中的

对话框打开设计文件导入添加对话框。

2、选择第二项 Add or Create Design Sources,用来添加或新建 Verilog 源文件,点击 Next

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

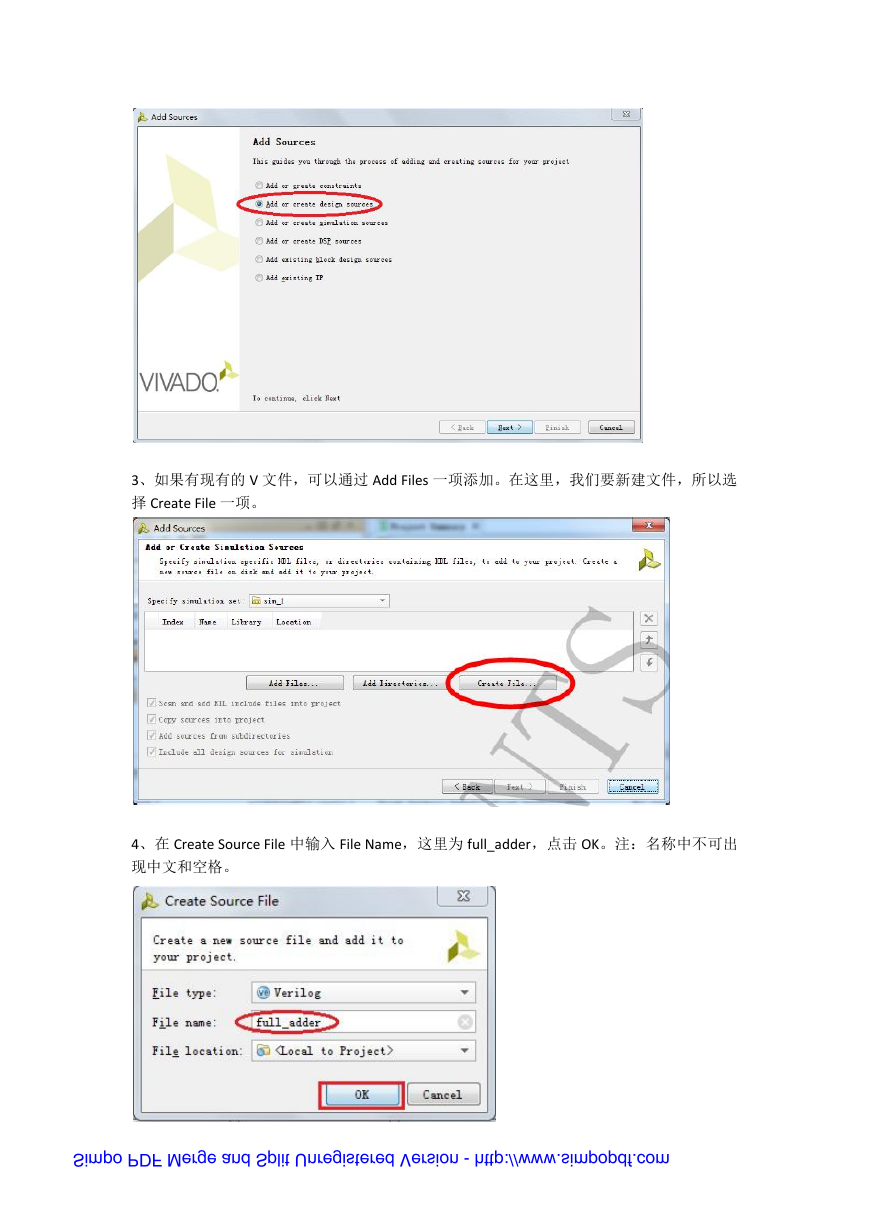

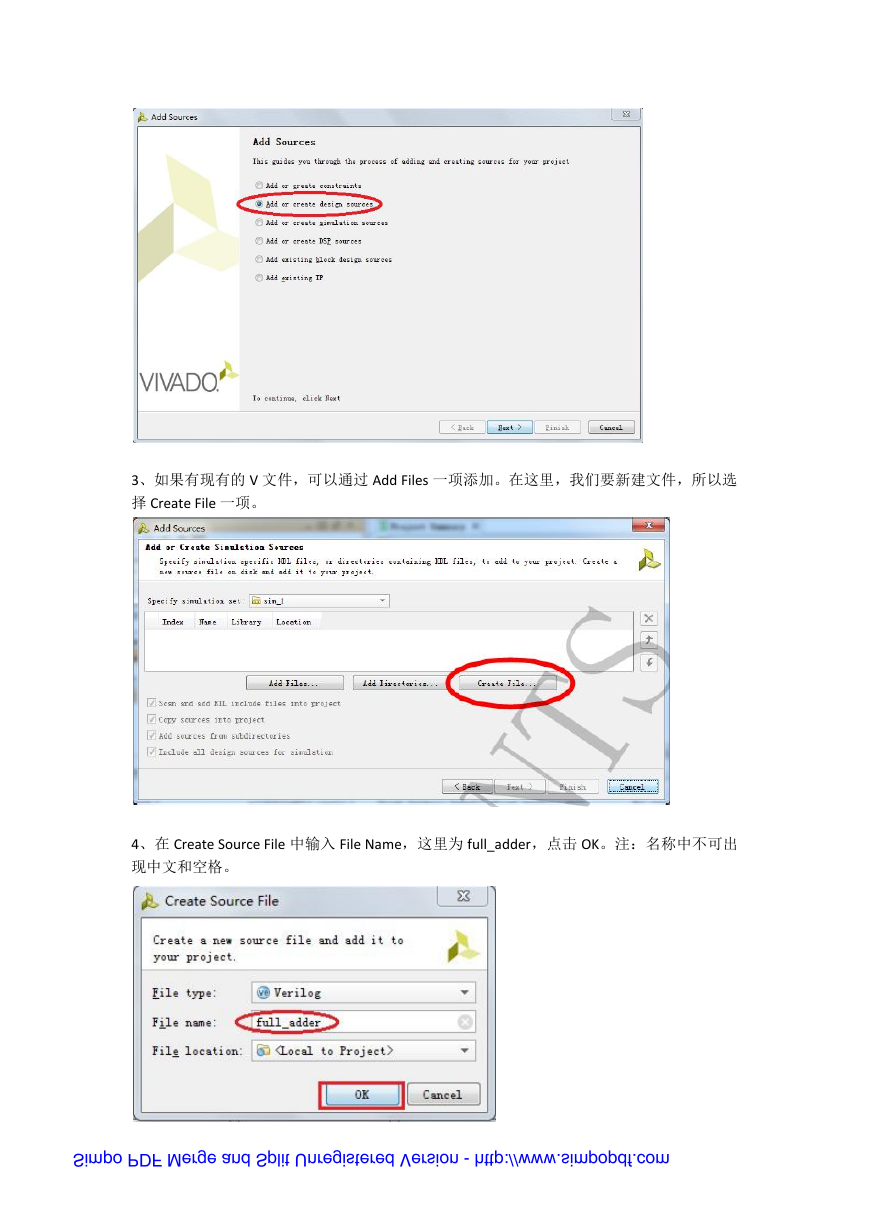

3、如果有现有的 V 文件,可以通过 Add Files 一项添加。在这里,我们要新建文件,所以选

择 Create File 一项。

4、在 Create Source File 中输入 File Name,这里为 full_adder,点击 OK。注:名称中不可出

现中文和空格。

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

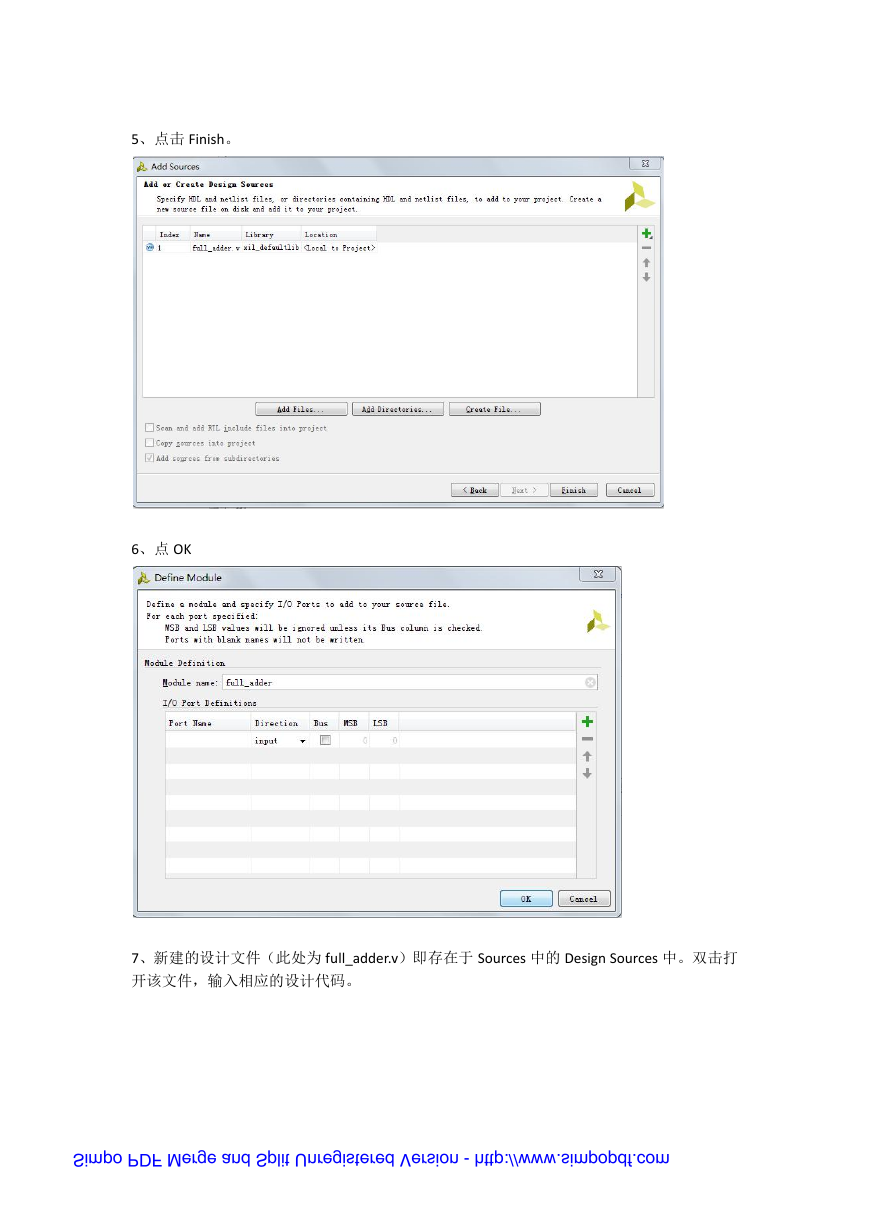

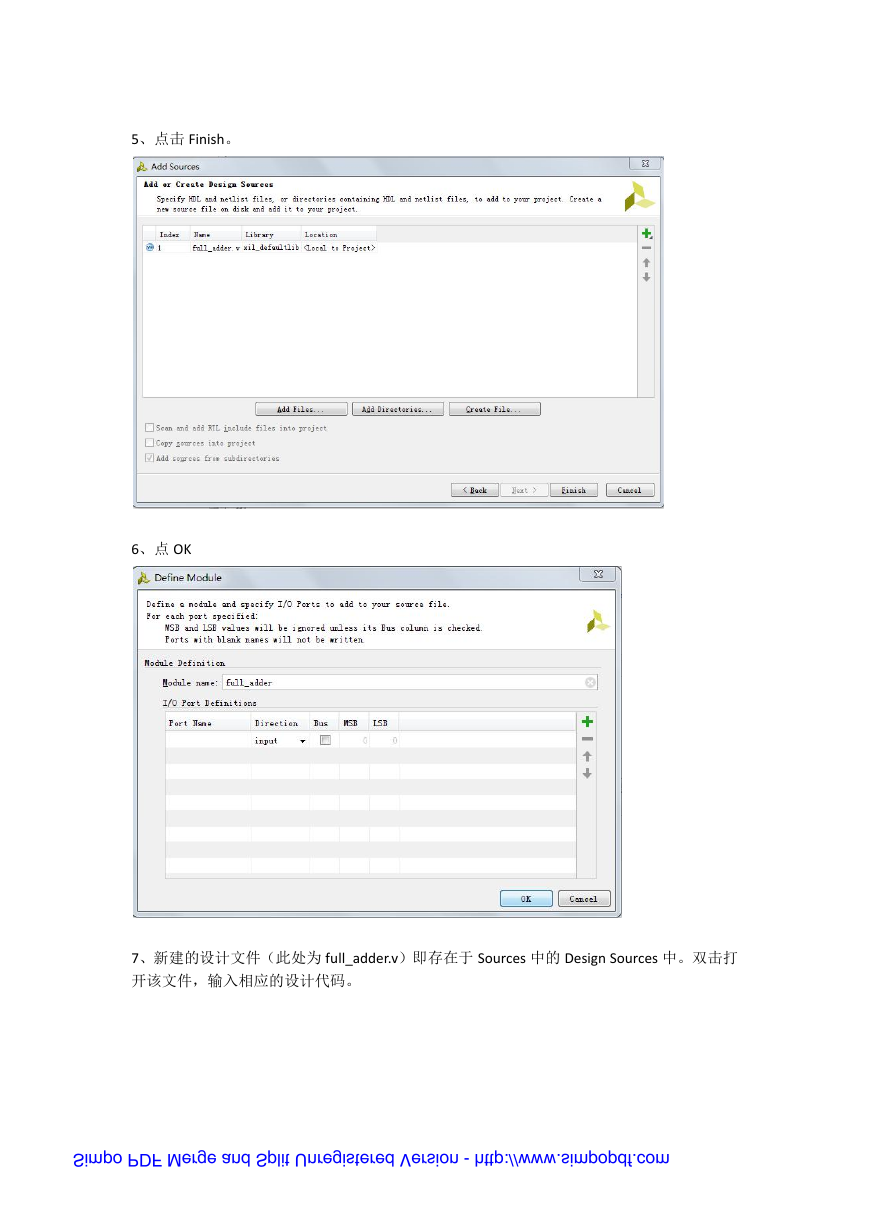

5、点击 Finish。

6、点 OK

7、新建的设计文件(此处为 full_adder.v)即存在于 Sources 中的 Design Sources 中。双击打

开该文件,输入相应的设计代码。

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc