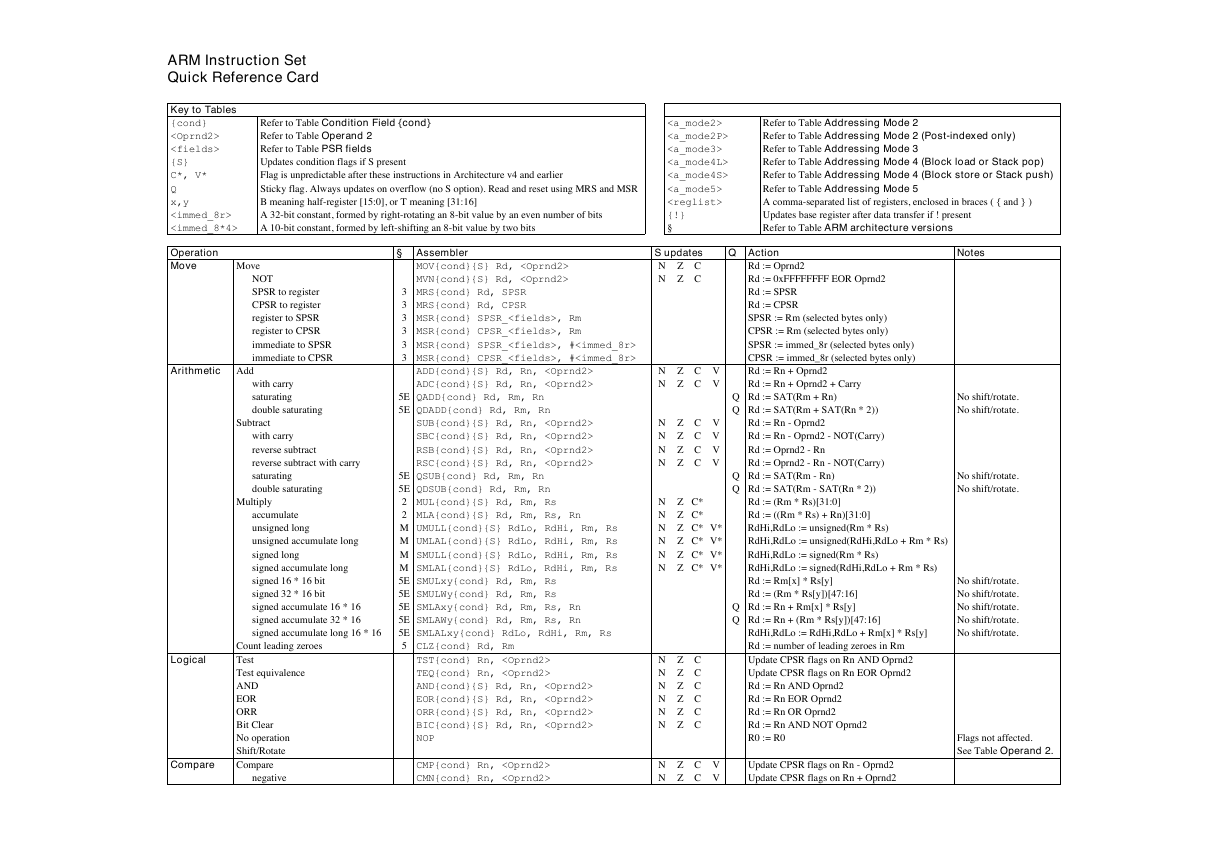

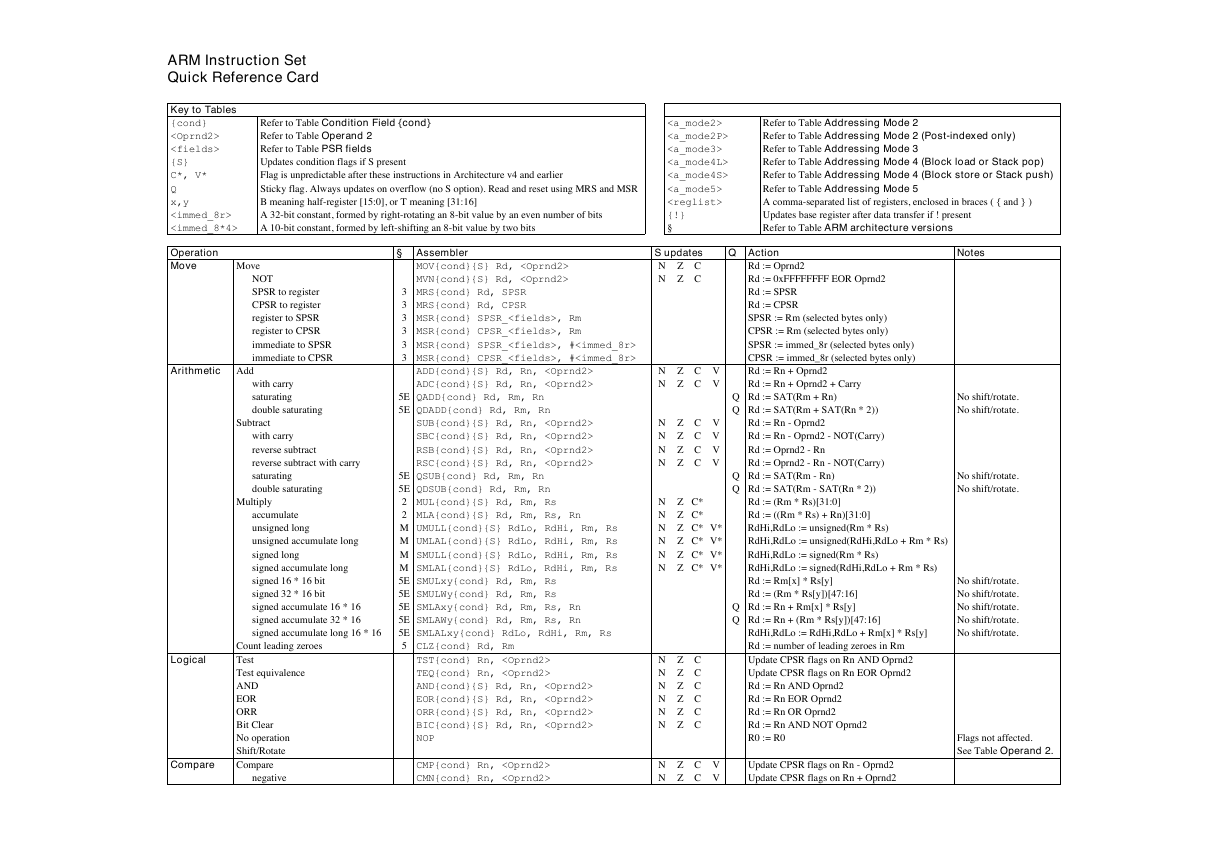

ARM Instruction Set

Quick Reference Card

Key to Tables

{cond}

{S}

C*, V*

Q

x,y

Operation

Move

Move

Refer to Table Condition Field {cond}

Refer to Table Operand 2

Refer to Table PSR fields

Updates condition flags if S present

Flag is unpredictable after these instructions in Architecture v4 and earlier

Sticky flag. Always updates on overflow (no S option). Read and reset using MRS and MSR

B meaning half-register [15:0], or T meaning [31:16]

A 32-bit constant, formed by right-rotating an 8-bit value by an even number of bits

A 10-bit constant, formed by left-shifting an 8-bit value by two bits

{!}

§

Refer to Table Addressing Mode 2

Refer to Table Addressing Mode 2 (Post-indexed only)

Refer to Table Addressing Mode 3

Refer to Table Addressing Mode 4 (Block load or Stack pop)

Refer to Table Addressing Mode 4 (Block store or Stack push)

Refer to Table Addressing Mode 5

A comma-separated list of registers, enclosed in braces ( { and } )

Updates base register after data transfer if ! present

Refer to Table ARM architecture versions

NOT

SPSR to register

CPSR to register

register to SPSR

register to CPSR

immediate to SPSR

immediate to CPSR

Arithmetic

Add

with carry

saturating

double saturating

Subtract

with carry

reverse subtract

reverse subtract with carry

saturating

double saturating

Multiply

accumulate

unsigned long

unsigned accumulate long

signed long

signed accumulate long

signed 16 * 16 bit

signed 32 * 16 bit

signed accumulate 16 * 16

signed accumulate 32 * 16

signed accumulate long 16 * 16

Logical

Compare

Count leading zeroes

Test

Test equivalence

AND

EOR

ORR

Bit Clear

No operation

Shift/Rotate

Compare

negative

§ Assembler

MOV{cond}{S} Rd,

MVN{cond}{S} Rd,

S updates

N Z C

N Z C

3 MRS{cond} Rd, SPSR

3 MRS{cond} Rd, CPSR

3 MSR{cond} SPSR_, Rm

3 MSR{cond} CPSR_, Rm

3 MSR{cond} SPSR_, #

3 MSR{cond} CPSR_, #

ADD{cond}{S} Rd, Rn,

ADC{cond}{S} Rd, Rn,

N Z C V

N Z C V

5E QADD{cond} Rd, Rm, Rn

5E QDADD{cond} Rd, Rm, Rn

SUB{cond}{S} Rd, Rn,

SBC{cond}{S} Rd, Rn,

RSB{cond}{S} Rd, Rn,

RSC{cond}{S} Rd, Rn,

5E QSUB{cond} Rd, Rm, Rn

5E QDSUB{cond} Rd, Rm, Rn

2 MUL{cond}{S} Rd, Rm, Rs

2 MLA{cond}{S} Rd, Rm, Rs, Rn

M UMULL{cond}{S} RdLo, RdHi, Rm, Rs

M UMLAL{cond}{S} RdLo, RdHi, Rm, Rs

M SMULL{cond}{S} RdLo, RdHi, Rm, Rs

M SMLAL{cond}{S} RdLo, RdHi, Rm, Rs

5E SMULxy{cond} Rd, Rm, Rs

5E SMULWy{cond} Rd, Rm, Rs

5E SMLAxy{cond} Rd, Rm, Rs, Rn

5E SMLAWy{cond} Rd, Rm, Rs, Rn

5E SMLALxy{cond} RdLo, RdHi, Rm, Rs

5 CLZ{cond} Rd, Rm

TST{cond} Rn,

TEQ{cond} Rn,

AND{cond}{S} Rd, Rn,

EOR{cond}{S} Rd, Rn,

ORR{cond}{S} Rd, Rn,

BIC{cond}{S} Rd, Rn,

NOP

N Z C V

N Z C V

N Z C V

N Z C V

N Z C*

N Z C*

N Z C* V*

N Z C* V*

N Z C* V*

N Z C* V*

N Z C

N Z C

N Z C

N Z C

N Z C

N Z C

Q Action

Notes

Rd := Oprnd2

Rd := 0xFFFFFFFF EOR Oprnd2

Rd := SPSR

Rd := CPSR

SPSR := Rm (selected bytes only)

CPSR := Rm (selected bytes only)

SPSR := immed_8r (selected bytes only)

CPSR := immed_8r (selected bytes only)

Rd := Rn + Oprnd2

Rd := Rn + Oprnd2 + Carry

Q Rd := SAT(Rm + Rn)

Q Rd := SAT(Rm + SAT(Rn * 2))

Rd := Rn - Oprnd2

Rd := Rn - Oprnd2 - NOT(Carry)

Rd := Oprnd2 - Rn

Rd := Oprnd2 - Rn - NOT(Carry)

Q Rd := SAT(Rm - Rn)

Q Rd := SAT(Rm - SAT(Rn * 2))

Rd := (Rm * Rs)[31:0]

Rd := ((Rm * Rs) + Rn)[31:0]

RdHi,RdLo := unsigned(Rm * Rs)

RdHi,RdLo := unsigned(RdHi,RdLo + Rm * Rs)

RdHi,RdLo := signed(Rm * Rs)

RdHi,RdLo := signed(RdHi,RdLo + Rm * Rs)

Rd := Rm[x] * Rs[y]

Rd := (Rm * Rs[y])[47:16]

Q Rd := Rn + Rm[x] * Rs[y]

Q Rd := Rn + (Rm * Rs[y])[47:16]

RdHi,RdLo := RdHi,RdLo + Rm[x] * Rs[y]

Rd := number of leading zeroes in Rm

Update CPSR flags on Rn AND Oprnd2

Update CPSR flags on Rn EOR Oprnd2

Rd := Rn AND Oprnd2

Rd := Rn EOR Oprnd2

Rd := Rn OR Oprnd2

Rd := Rn AND NOT Oprnd2

R0 := R0

No shift/rotate.

No shift/rotate.

No shift/rotate.

No shift/rotate.

No shift/rotate.

No shift/rotate.

No shift/rotate.

No shift/rotate.

No shift/rotate.

Flags not affected.

See Table Operand 2.

CMP{cond} Rn,

CMN{cond} Rn,

N Z C V

N Z C V

Update CPSR flags on Rn - Oprnd2

Update CPSR flags on Rn + Oprnd2

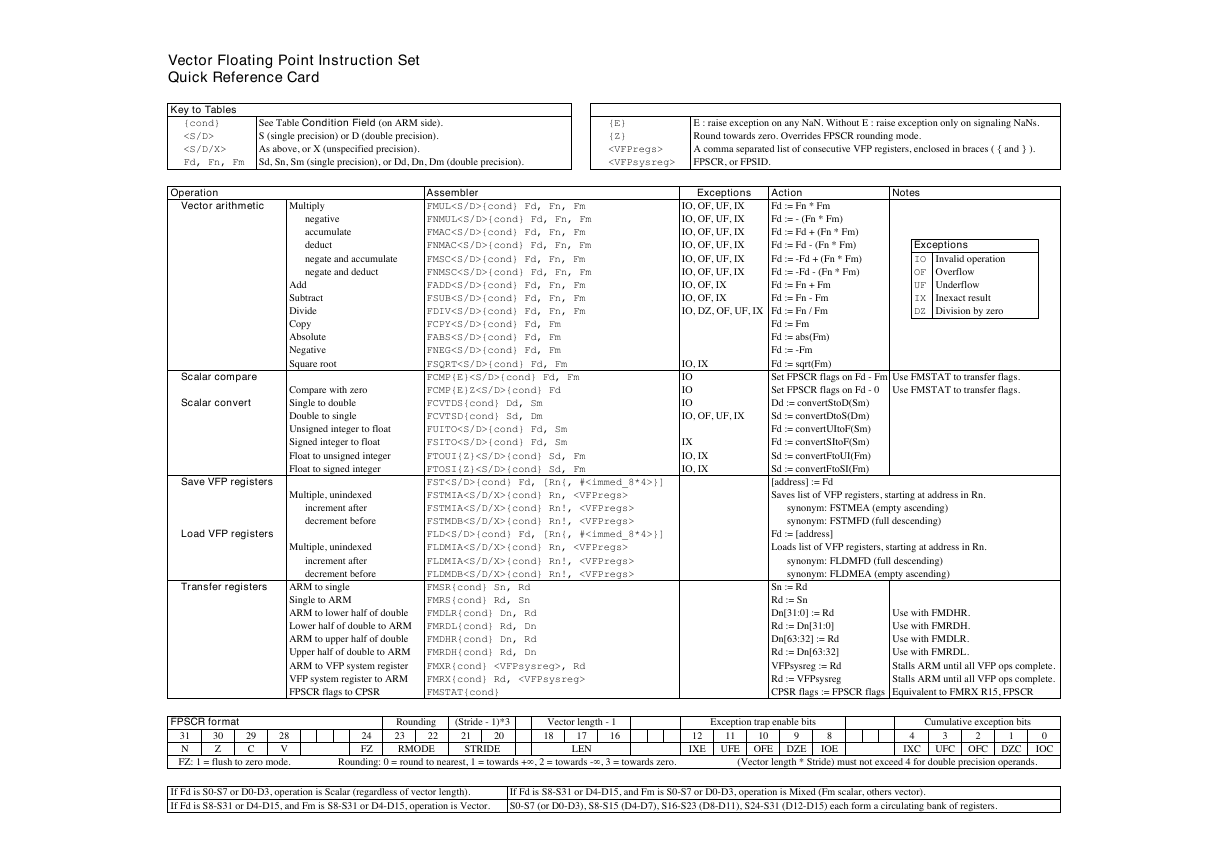

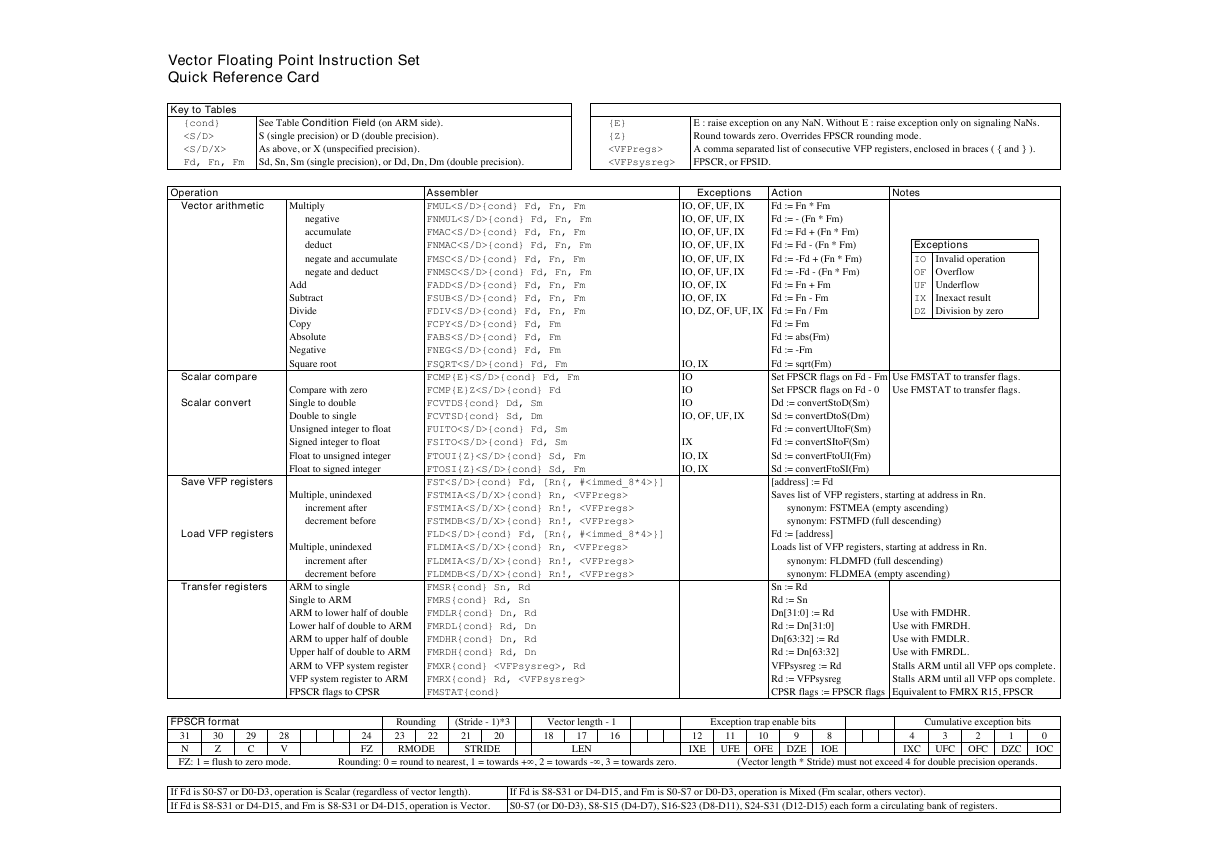

�Vector Floating Point Instruction Set

Quick Reference Card

Key to Tables

{cond}

Fd, Fn, Fm

See Table Condition Field (on ARM side).

S (single precision) or D (double precision).

As above, or X (unspecified precision).

Sd, Sn, Sm (single precision), or Dd, Dn, Dm (double precision).

{E}

{Z}

E : raise exception on any NaN. Without E : raise exception only on signaling NaNs.

Round towards zero. Overrides FPSCR rounding mode.

A comma separated list of consecutive VFP registers, enclosed in braces ( { and } ).

FPSCR, or FPSID.

Operation

Vector arithmetic

Scalar compare

Scalar convert

Save VFP registers

Load VFP registers

Transfer registers

FPSCR format

30

Z

28

31

N

V

FZ: 1 = flush to zero mode.

29

C

Exceptions

Action

Fd := Fn * Fm

IO, OF, UF, IX

Fd := - (Fn * Fm)

IO, OF, UF, IX

Fd := Fd + (Fn * Fm)

IO, OF, UF, IX

Fd := Fd - (Fn * Fm)

IO, OF, UF, IX

Fd := -Fd + (Fn * Fm)

IO, OF, UF, IX

Fd := -Fd - (Fn * Fm)

IO, OF, UF, IX

Fd := Fn + Fm

IO, OF, IX

IO, OF, IX

Fd := Fn - Fm

IO, DZ, OF, UF, IX Fd := Fn / Fm

Notes

Exceptions

IO Invalid operation

OF Overflow

UF Underflow

IX Inexact result

DZ Division by zero

IO, IX

IO

IO

IO

IO, OF, UF, IX

IX

IO, IX

IO, IX

Fd := Fm

Fd := abs(Fm)

Fd := -Fm

Fd := sqrt(Fm)

Set FPSCR flags on Fd - Fm Use FMSTAT to transfer flags.

Set FPSCR flags on Fd - 0 Use FMSTAT to transfer flags.

Dd := convertStoD(Sm)

Sd := convertDtoS(Dm)

Fd := convertUItoF(Sm)

Fd := convertSItoF(Sm)

Sd := convertFtoUI(Fm)

Sd := convertFtoSI(Fm)

[address] := Fd

Saves list of VFP registers, starting at address in Rn.

synonym: FSTMEA (empty ascending)

synonym: FSTMFD (full descending)

Fd := [address]

Loads list of VFP registers, starting at address in Rn.

synonym: FLDMFD (full descending)

synonym: FLDMEA (empty ascending)

Sn := Rd

Rd := Sn

Dn[31:0] := Rd

Rd := Dn[31:0]

Dn[63:32] := Rd

Rd := Dn[63:32]

VFPsysreg := Rd

Rd := VFPsysreg

CPSR flags := FPSCR flags Equivalent to FMRX R15, FPSCR

Use with FMDHR.

Use with FMRDH.

Use with FMDLR.

Use with FMRDL.

Stalls ARM until all VFP ops complete.

Stalls ARM until all VFP ops complete.

Exception trap enable bits

12

IXE

10

11

UFE OFE DZE

9

8

IOE

Cumulative exception bits

4

3

2

1

0

IXC UFC OFC DZC

IOC

Multiply

Add

Subtract

Divide

Copy

Absolute

Negative

Square root

negative

accumulate

deduct

negate and accumulate

negate and deduct

Compare with zero

Single to double

Double to single

Unsigned integer to float

Signed integer to float

Float to unsigned integer

Float to signed integer

Assembler

FMUL{cond} Fd, Fn, Fm

FNMUL{cond} Fd, Fn, Fm

FMAC{cond} Fd, Fn, Fm

FNMAC{cond} Fd, Fn, Fm

FMSC{cond} Fd, Fn, Fm

FNMSC{cond} Fd, Fn, Fm

FADD{cond} Fd, Fn, Fm

FSUB{cond} Fd, Fn, Fm

FDIV{cond} Fd, Fn, Fm

FCPY{cond} Fd, Fm

FABS{cond} Fd, Fm

FNEG{cond} Fd, Fm

FSQRT{cond} Fd, Fm

FCMP{E}{cond} Fd, Fm

FCMP{E}Z{cond} Fd

FCVTDS{cond} Dd, Sm

FCVTSD{cond} Sd, Dm

FUITO{cond} Fd, Sm

FSITO{cond} Fd, Sm

FTOUI{Z}{cond} Sd, Fm

FTOSI{Z}{cond} Sd, Fm

FST{cond} Fd, [Rn{, #}]

FSTMIA{cond} Rn,

FSTMIA{cond} Rn!,

FSTMDB{cond} Rn!,

FLD{cond} Fd, [Rn{, #}]

FLDMIA{cond} Rn,

FLDMIA{cond} Rn!,

FLDMDB{cond} Rn!,

ARM to single

FMSR{cond} Sn, Rd

Single to ARM

FMRS{cond} Rd, Sn

ARM to lower half of double

FMDLR{cond} Dn, Rd

Lower half of double to ARM FMRDL{cond} Rd, Dn

ARM to upper half of double

FMDHR{cond} Dn, Rd

Upper half of double to ARM FMRDH{cond} Rd, Dn

ARM to VFP system register

VFP system register to ARM

FPSCR flags to CPSR

FMXR{cond} , Rd

FMRX{cond} Rd,

FMSTAT{cond}

Multiple, unindexed

increment after

decrement before

Multiple, unindexed

increment after

decrement before

Rounding

23

22

RMODE

(Stride - 1)*3

21

20

STRIDE

24

FZ

Rounding: 0 = round to nearest, 1 = towards +¥

Vector length - 1

18

16

17

LEN

, 2 = towards -¥

If Fd is S0-S7 or D0-D3, operation is Scalar (regardless of vector length).

If Fd is S8-S31 or D4-D15, and Fm is S8-S31 or D4-D15, operation is Vector.

If Fd is S8-S31 or D4-D15, and Fm is S0-S7 or D0-D3, operation is Mixed (Fm scalar, others vector).

S0-S7 (or D0-D3), S8-S15 (D4-D7), S16-S23 (D8-D11), S24-S31 (D12-D15) each form a circulating bank of registers.

, 3 = towards zero.

(Vector length * Stride) must not exceed 4 for double precision operands.

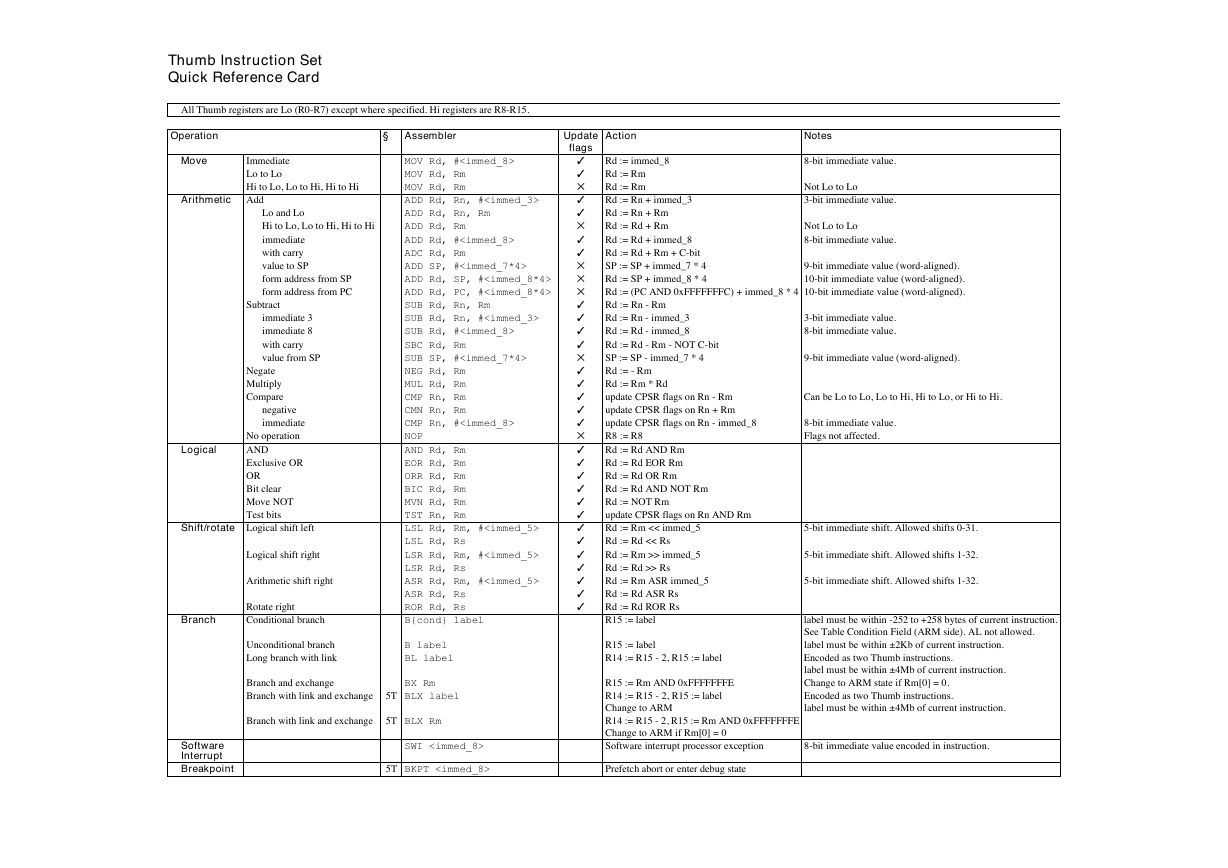

�

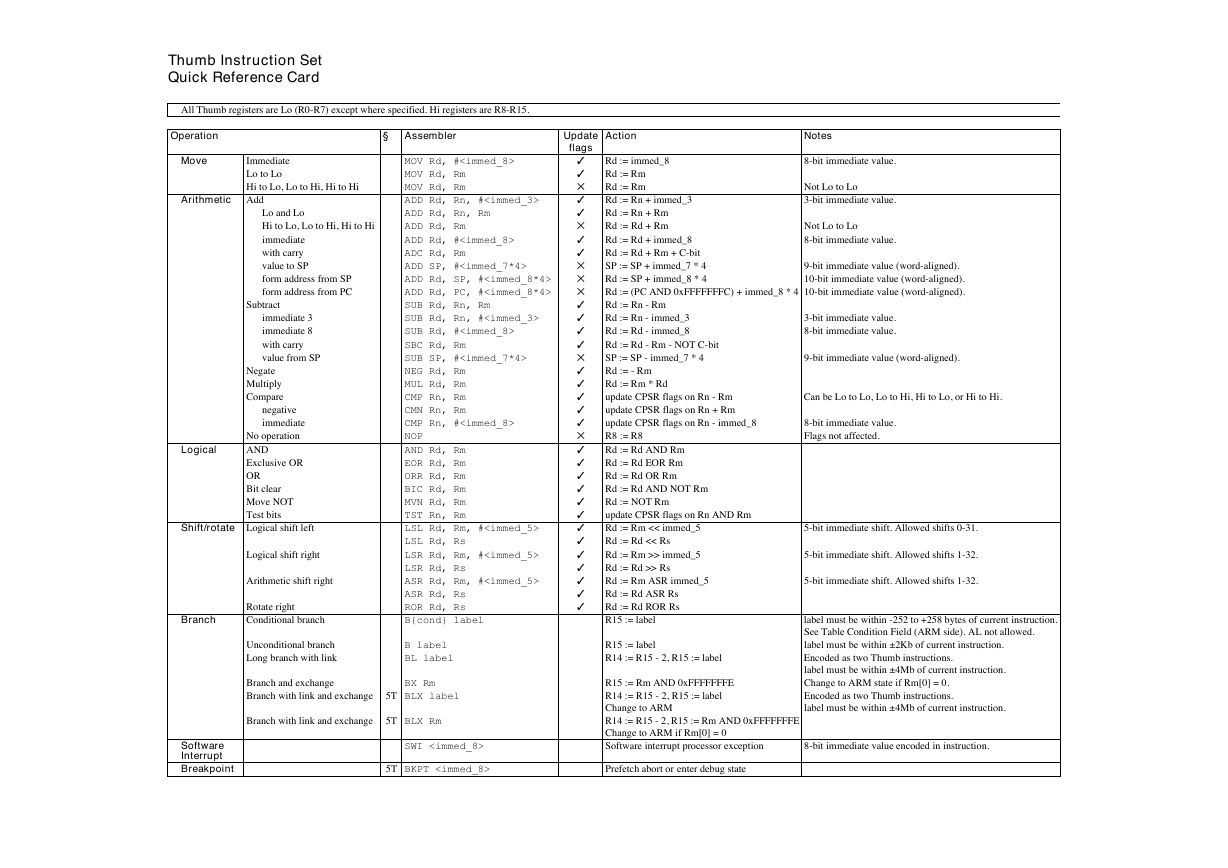

Thumb Instruction Set

Quick Reference Card

All Thumb registers are Lo (R0-R7) except where specified. Hi registers are R8-R15.

Operation

Move

Arithmetic

Immediate

Lo to Lo

Hi to Lo, Lo to Hi, Hi to Hi

Add

Lo and Lo

Hi to Lo, Lo to Hi, Hi to Hi

immediate

with carry

value to SP

form address from SP

form address from PC

Subtract

immediate 3

immediate 8

with carry

value from SP

Negate

Multiply

Compare

negative

immediate

No operation

AND

Exclusive OR

OR

Bit clear

Move NOT

Test bits

Logical

Shift/rotate Logical shift left

Logical shift right

Arithmetic shift right

Branch

Rotate right

Conditional branch

MOV Rd, #

MOV Rd, Rm

MOV Rd, Rm

ADD Rd, Rn, #

ADD Rd, Rn, Rm

ADD Rd, Rm

ADD Rd, #

ADC Rd, Rm

ADD SP, #

ADD Rd, SP, #

ADD Rd, PC, #

SUB Rd, Rn, Rm

SUB Rd, Rn, #

SUB Rd, #

SBC Rd, Rm

SUB SP, #

NEG Rd, Rm

MUL Rd, Rm

CMP Rn, Rm

CMN Rn, Rm

CMP Rn, #

NOP

AND Rd, Rm

EOR Rd, Rm

ORR Rd, Rm

BIC Rd, Rm

MVN Rd, Rm

TST Rn, Rm

LSL Rd, Rm, #

LSL Rd, Rs

LSR Rd, Rm, #

LSR Rd, Rs

ASR Rd, Rm, #

ASR Rd, Rs

ROR Rd, Rs

B{cond} label

3

3

5

3

3

5

3

3

5

5

5

3

3

3

3

5

3

3

3

3

3

5

3

3

3

3

3

3

3

3

3

3

3

3

3

Unconditional branch

Long branch with link

B label

BL label

Branch and exchange

Branch with link and exchange

BX Rm

5T BLX label

Branch with link and exchange

5T BLX Rm

SWI

R15 := label

R14 := R15 - 2, R15 := label

R15 := Rm AND 0xFFFFFFFE

R14 := R15 - 2, R15 := label

Change to ARM

R14 := R15 - 2, R15 := Rm AND 0xFFFFFFFE

Change to ARM if Rm[0] = 0

Software interrupt processor exception

5T BKPT

Prefetch abort or enter debug state

Software

Interrupt

Breakpoint

label must be within -252 to +258 bytes of current instruction.

See Table Condition Field (ARM side). AL not allowed.

label must be within ±2Kb of current instruction.

Encoded as two Thumb instructions.

label must be within ±4Mb of current instruction.

Change to ARM state if Rm[0] = 0.

Encoded as two Thumb instructions.

label must be within ±4Mb of current instruction.

8-bit immediate value encoded in instruction.

§

Assembler

Update

flags

Action

Notes

8-bit immediate value.

3-bit immediate value.

8-bit immediate value.

Not Lo to Lo

8-bit immediate value.

Not Lo to Lo

3-bit immediate value.

Rd := immed_8

Rd := Rm

Rd := Rm

Rd := Rn + immed_3

Rd := Rn + Rm

Rd := Rd + Rm

Rd := Rd + immed_8

Rd := Rd + Rm + C-bit

9-bit immediate value (word-aligned).

SP := SP + immed_7 * 4

Rd := SP + immed_8 * 4

10-bit immediate value (word-aligned).

Rd := (PC AND 0xFFFFFFFC) + immed_8 * 4 10-bit immediate value (word-aligned).

Rd := Rn - Rm

Rd := Rn - immed_3

Rd := Rd - immed_8

Rd := Rd - Rm - NOT C-bit

SP := SP - immed_7 * 4

Rd := - Rm

Rd := Rm * Rd

update CPSR flags on Rn - Rm

update CPSR flags on Rn + Rm

update CPSR flags on Rn - immed_8

R8 := R8

Rd := Rd AND Rm

Rd := Rd EOR Rm

Rd := Rd OR Rm

Rd := Rd AND NOT Rm

Rd := NOT Rm

update CPSR flags on Rn AND Rm

Rd := Rm << immed_5

Rd := Rd << Rs

Rd := Rm >> immed_5

Rd := Rd >> Rs

Rd := Rm ASR immed_5

Rd := Rd ASR Rs

Rd := Rd ROR Rs

R15 := label

5-bit immediate shift. Allowed shifts 0-31.

5-bit immediate shift. Allowed shifts 1-32.

5-bit immediate shift. Allowed shifts 1-32.

9-bit immediate value (word-aligned).

Can be Lo to Lo, Lo to Hi, Hi to Lo, or Hi to Hi.

8-bit immediate value.

Flags not affected.

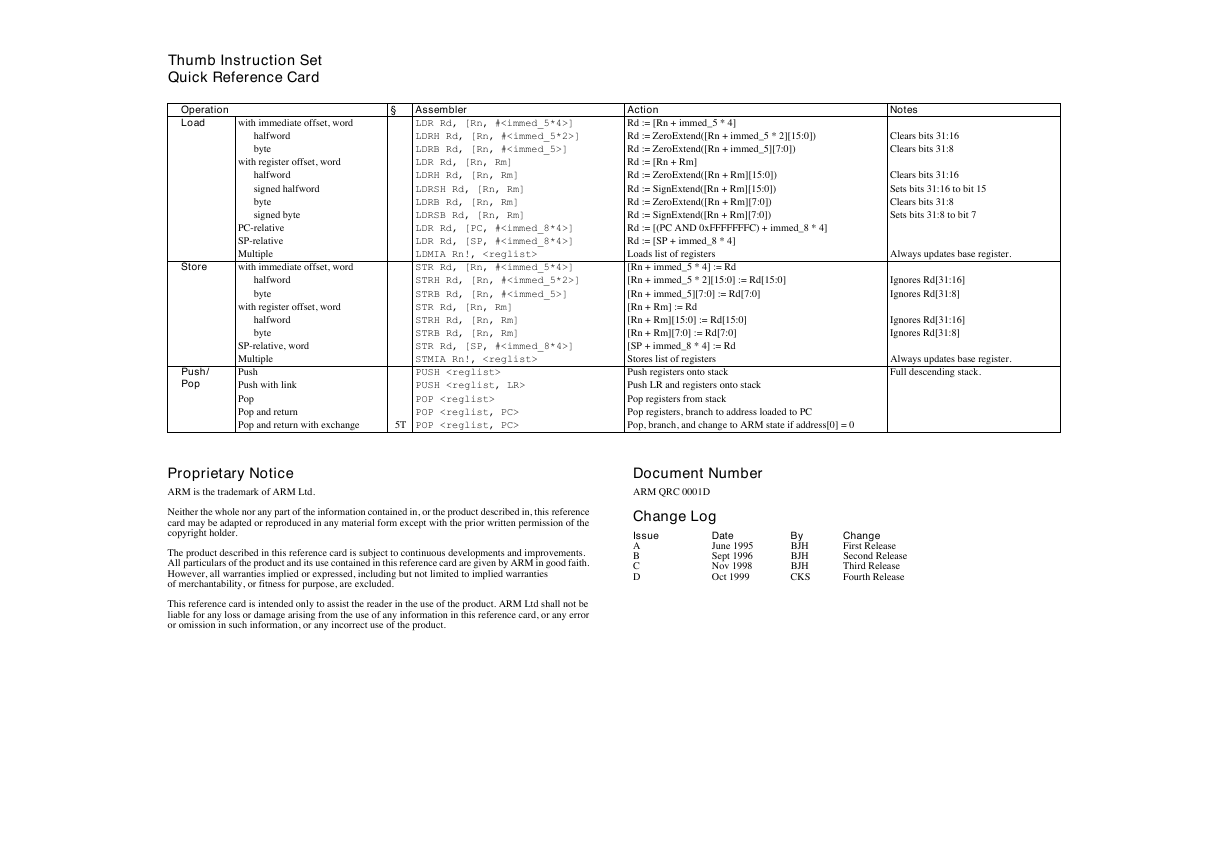

�

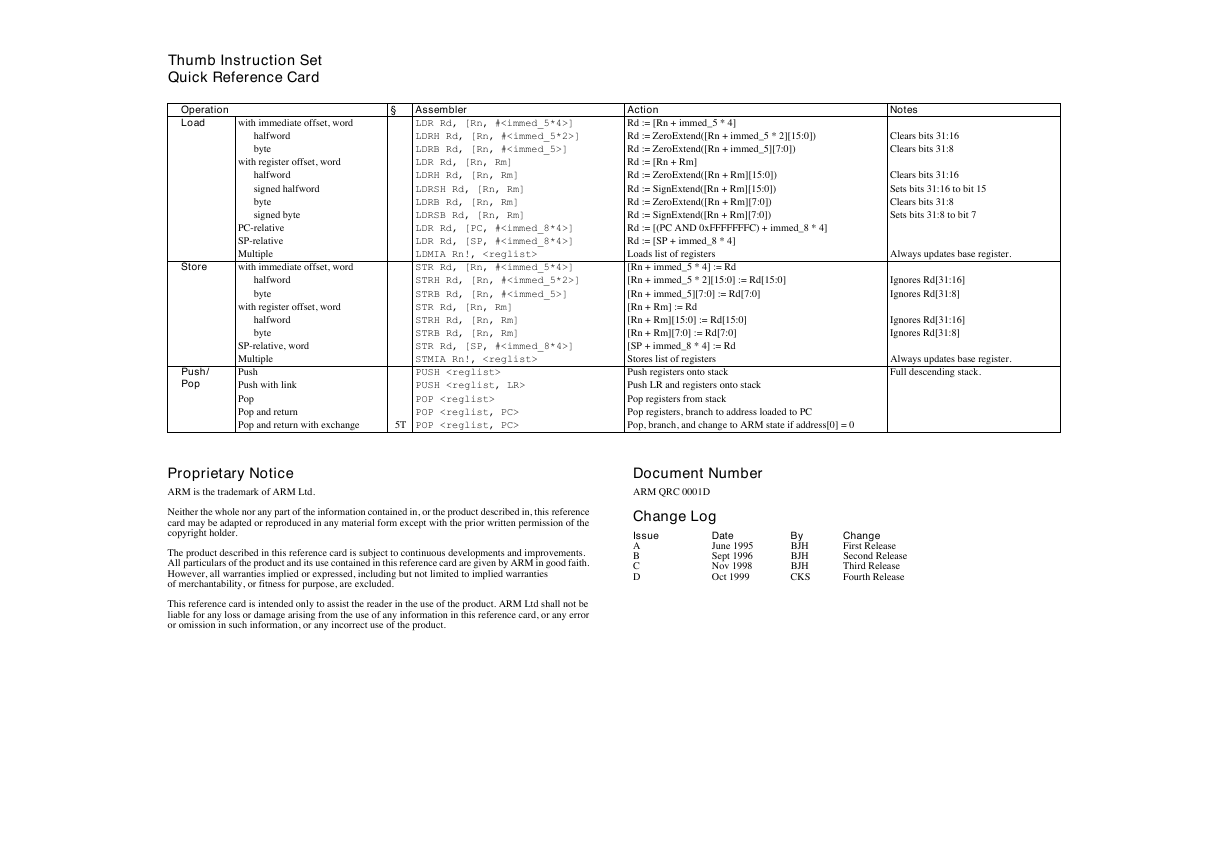

Thumb Instruction Set

Quick Reference Card

Operation

Load

Store

Push/

Pop

with immediate offset, word

halfword

byte

with register offset, word

halfword

signed halfword

byte

signed byte

PC-relative

SP-relative

Multiple

with immediate offset, word

halfword

byte

with register offset, word

halfword

byte

SP-relative, word

Multiple

Push

Push with link

Pop

Pop and return

Pop and return with exchange

Proprietary Notice

ARM is the trademark of ARM Ltd.

§

Assembler

LDR Rd, [Rn, #]

LDRH Rd, [Rn, #]

LDRB Rd, [Rn, #]

LDR Rd, [Rn, Rm]

LDRH Rd, [Rn, Rm]

LDRSH Rd, [Rn, Rm]

LDRB Rd, [Rn, Rm]

LDRSB Rd, [Rn, Rm]

LDR Rd, [PC, #]

LDR Rd, [SP, #]

LDMIA Rn!,

STR Rd, [Rn, #]

STRH Rd, [Rn, #]

STRB Rd, [Rn, #]

STR Rd, [Rn, Rm]

STRH Rd, [Rn, Rm]

STRB Rd, [Rn, Rm]

STR Rd, [SP, #]

STMIA Rn!,

PUSH

PUSH

POP

POP

5T POP

Action

Rd := [Rn + immed_5 * 4]

Rd := ZeroExtend([Rn + immed_5 * 2][15:0])

Rd := ZeroExtend([Rn + immed_5][7:0])

Rd := [Rn + Rm]

Rd := ZeroExtend([Rn + Rm][15:0])

Rd := SignExtend([Rn + Rm][15:0])

Rd := ZeroExtend([Rn + Rm][7:0])

Rd := SignExtend([Rn + Rm][7:0])

Rd := [(PC AND 0xFFFFFFFC) + immed_8 * 4]

Rd := [SP + immed_8 * 4]

Loads list of registers

[Rn + immed_5 * 4] := Rd

[Rn + immed_5 * 2][15:0] := Rd[15:0]

[Rn + immed_5][7:0] := Rd[7:0]

[Rn + Rm] := Rd

[Rn + Rm][15:0] := Rd[15:0]

[Rn + Rm][7:0] := Rd[7:0]

[SP + immed_8 * 4] := Rd

Stores list of registers

Push registers onto stack

Push LR and registers onto stack

Pop registers from stack

Pop registers, branch to address loaded to PC

Pop, branch, and change to ARM state if address[0] = 0

Notes

Clears bits 31:16

Clears bits 31:8

Clears bits 31:16

Sets bits 31:16 to bit 15

Clears bits 31:8

Sets bits 31:8 to bit 7

Always updates base register.

Ignores Rd[31:16]

Ignores Rd[31:8]

Ignores Rd[31:16]

Ignores Rd[31:8]

Always updates base register.

Full descending stack.

Neither the whole nor any part of the information contained in, or the product described in, this reference

card may be adapted or reproduced in any material form except with the prior written permission of the

copyright holder.

The product described in this reference card is subject to continuous developments and improvements.

All particulars of the product and its use contained in this reference card are given by ARM in good faith.

However, all warranties implied or expressed, including but not limited to implied warranties

of merchantability, or fitness for purpose, are excluded.

This reference card is intended only to assist the reader in the use of the product. ARM Ltd shall not be

liable for any loss or damage arising from the use of any information in this reference card, or any error

or omission in such information, or any incorrect use of the product.

Document Number

ARM QRC 0001D

Change Log

Issue

A

B

C

D

Date

June 1995

Sept 1996

Nov 1998

Oct 1999

By

BJH

BJH

BJH

CKS

Change

First Release

Second Release

Third Release

Fourth Release

�

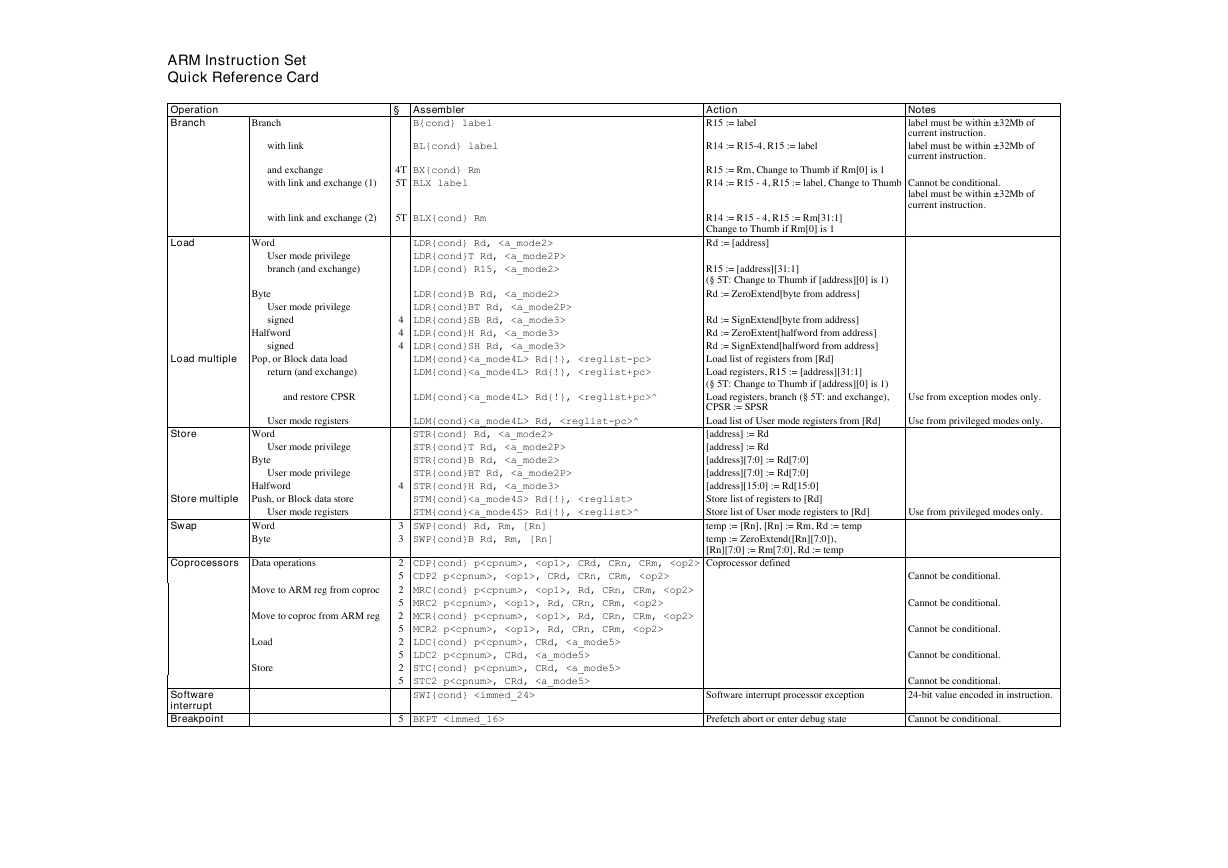

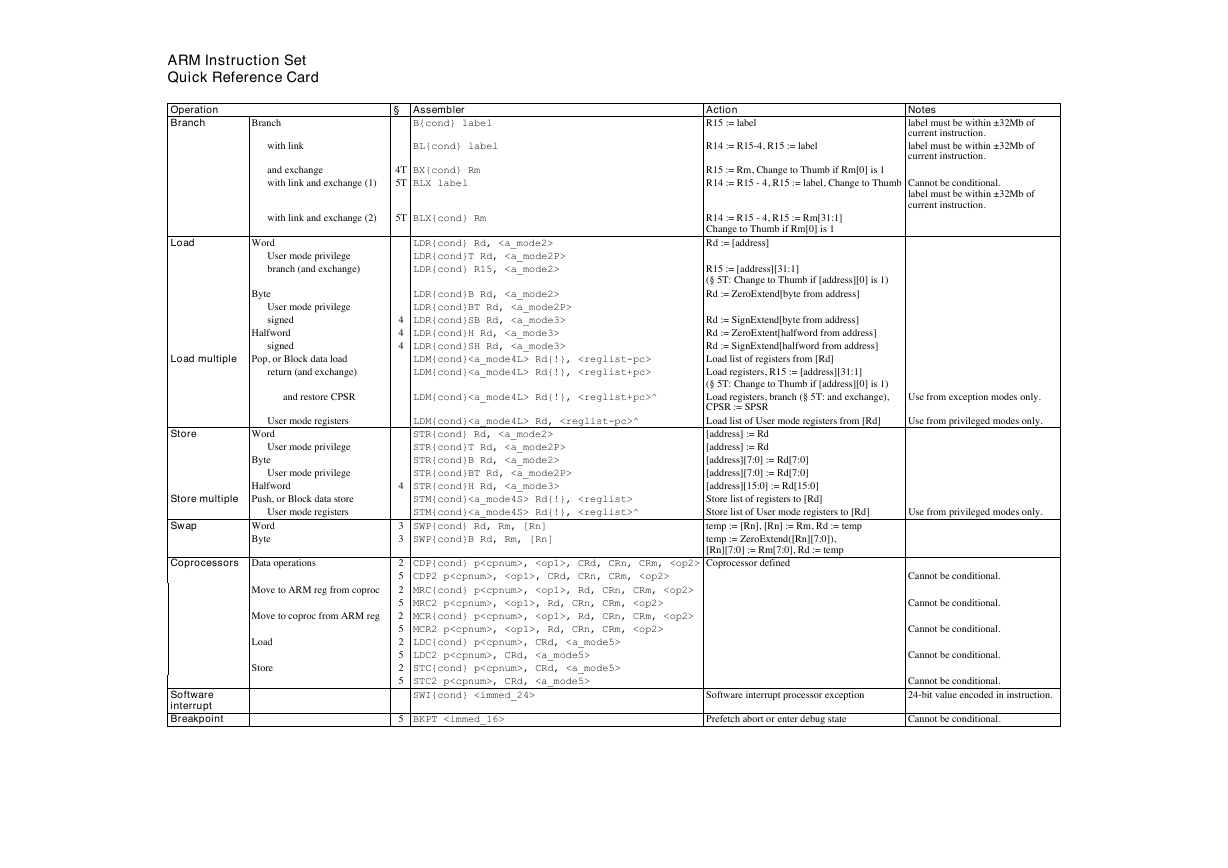

ARM Instruction Set

Quick Reference Card

Operation

Branch

Branch

with link

§ Assembler

B{cond} label

BL{cond} label

and exchange

with link and exchange (1)

4T BX{cond} Rm

5T BLX label

with link and exchange (2)

5T BLX{cond} Rm

Load

Word

User mode privilege

branch (and exchange)

Byte

User mode privilege

signed

Halfword

signed

Pop, or Block data load

return (and exchange)

Load multiple

LDR{cond} Rd,

LDR{cond}T Rd,

LDR{cond} R15,

LDR{cond}B Rd,

LDR{cond}BT Rd,

4 LDR{cond}SB Rd,

4 LDR{cond}H Rd,

4 LDR{cond}SH Rd,

LDM{cond} Rd{!},

LDM{cond} Rd{!},

and restore CPSR

LDM{cond} Rd{!}, ^

LDM{cond} Rd, ^

STR{cond} Rd,

STR{cond}T Rd,

STR{cond}B Rd,

STR{cond}BT Rd,

4 STR{cond}H Rd,

STM{cond} Rd{!},

STM{cond} Rd{!}, ^

3 SWP{cond} Rd, Rm, [Rn]

3 SWP{cond}B Rd, Rm, [Rn]

Store

Word

User mode registers

User mode privilege

Byte

User mode privilege

Halfword

Push, or Block data store

User mode registers

Word

Byte

Store multiple

Swap

Coprocessors Data operations

Move to ARM reg from coproc

Move to coproc from ARM reg

Load

Store

Software

interrupt

Breakpoint

2 CDP{cond} p, , CRd, CRn, CRm, Coprocessor defined

5 CDP2 p, , CRd, CRn, CRm,

2 MRC{cond} p, , Rd, CRn, CRm,

5 MRC2 p, , Rd, CRn, CRm,

2 MCR{cond} p, , Rd, CRn, CRm,

5 MCR2 p, , Rd, CRn, CRm,

2 LDC{cond} p, CRd,

5 LDC2 p, CRd,

2 STC{cond} p, CRd,

5 STC2 p, CRd,

SWI{cond}

Software interrupt processor exception

5 BKPT

Prefetch abort or enter debug state

Cannot be conditional.

Action

R15 := label

R14 := R15-4, R15 := label

Notes

label must be within ±32Mb of

current instruction.

label must be within ±32Mb of

current instruction.

R15 := Rm, Change to Thumb if Rm[0] is 1

R14 := R15 - 4, R15 := label, Change to Thumb Cannot be conditional.

label must be within ±32Mb of

current instruction.

R14 := R15 - 4, R15 := Rm[31:1]

Change to Thumb if Rm[0] is 1

Rd := [address]

R15 := [address][31:1]

(§ 5T: Change to Thumb if [address][0] is 1)

Rd := ZeroExtend[byte from address]

Rd := SignExtend[byte from address]

Rd := ZeroExtent[halfword from address]

Rd := SignExtend[halfword from address]

Load list of registers from [Rd]

Load registers, R15 := [address][31:1]

(§ 5T: Change to Thumb if [address][0] is 1)

Load registers, branch (§ 5T: and exchange),

CPSR := SPSR

Load list of User mode registers from [Rd]

[address] := Rd

[address] := Rd

[address][7:0] := Rd[7:0]

[address][7:0] := Rd[7:0]

[address][15:0] := Rd[15:0]

Store list of registers to [Rd]

Store list of User mode registers to [Rd]

temp := [Rn], [Rn] := Rm, Rd := temp

temp := ZeroExtend([Rn][7:0]),

[Rn][7:0] := Rm[7:0], Rd := temp

Use from exception modes only.

Use from privileged modes only.

Use from privileged modes only.

Cannot be conditional.

Cannot be conditional.

Cannot be conditional.

Cannot be conditional.

Cannot be conditional.

24-bit value encoded in instruction.

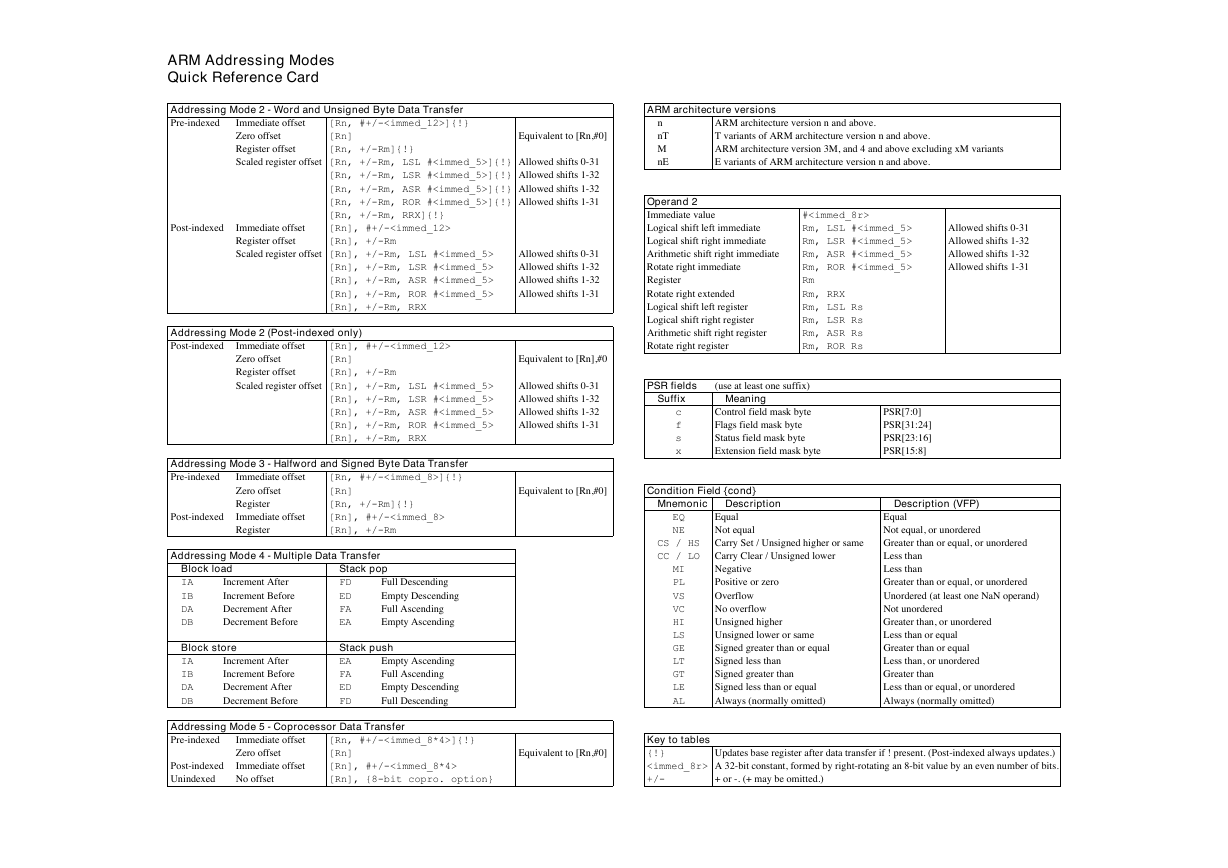

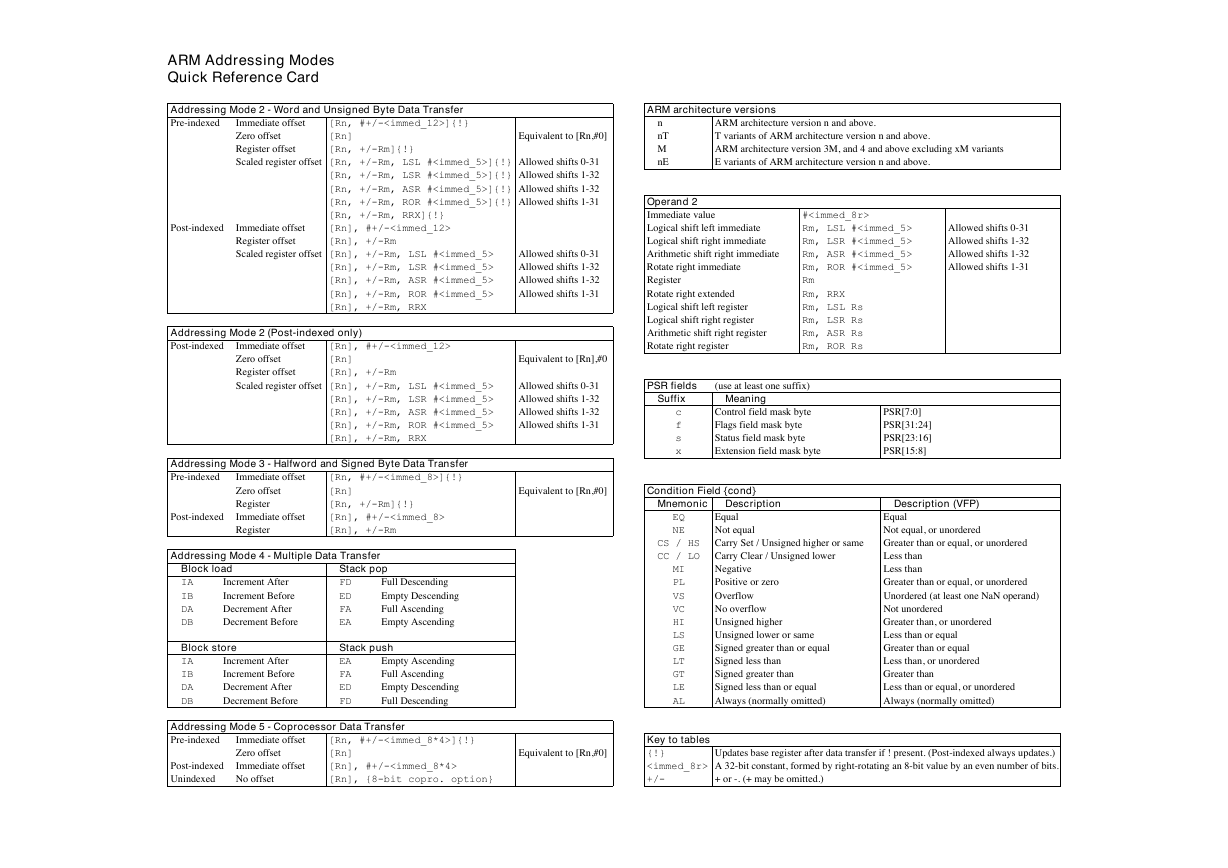

�ARM Addressing Modes

Quick Reference Card

Addressing Mode 2 - Word and Unsigned Byte Data Transfer

Pre-indexed

[Rn, #+/-]{!}

[Rn]

[Rn, +/-Rm]{!}

Immediate offset

Zero offset

Register offset

Scaled register offset [Rn, +/-Rm, LSL #]{!} Allowed shifts 0-31

[Rn, +/-Rm, LSR #]{!} Allowed shifts 1-32

[Rn, +/-Rm, ASR #]{!} Allowed shifts 1-32

[Rn, +/-Rm, ROR #]{!} Allowed shifts 1-31

[Rn, +/-Rm, RRX]{!}

[Rn], #+/-

[Rn], +/-Rm

Post-indexed

Equivalent to [Rn,#0]

Immediate offset

Register offset

Scaled register offset [Rn], +/-Rm, LSL #

[Rn], +/-Rm, LSR #

[Rn], +/-Rm, ASR #

[Rn], +/-Rm, ROR #

[Rn], +/-Rm, RRX

Addressing Mode 2 (Post-indexed only)

Post-indexed

[Rn], #+/-

[Rn]

[Rn], +/-Rm

Immediate offset

Zero offset

Register offset

Scaled register offset [Rn], +/-Rm, LSL #

[Rn], +/-Rm, LSR #

[Rn], +/-Rm, ASR #

[Rn], +/-Rm, ROR #

[Rn], +/-Rm, RRX

Addressing Mode 3 - Halfword and Signed Byte Data Transfer

Pre-indexed

[Rn, #+/-]{!}

[Rn]

[Rn, +/-Rm]{!}

[Rn], #+/-

[Rn], +/-Rm

Immediate offset

Zero offset

Register

Immediate offset

Register

Post-indexed

Addressing Mode 4 - Multiple Data Transfer

Block load

IA

IB

DA

DB

Increment After

Increment Before

Decrement After

Decrement Before

Block store

IA

IB

DA

DB

Increment After

Increment Before

Decrement After

Decrement Before

Stack pop

FD

ED

FA

EA

Full Descending

Empty Descending

Full Ascending

Empty Ascending

Stack push

EA

FA

ED

FD

Empty Ascending

Full Ascending

Empty Descending

Full Descending

Addressing Mode 5 - Coprocessor Data Transfer

Pre-indexed

Immediate offset

Zero offset

Immediate offset

No offset

[Rn, #+/-]{!}

[Rn]

[Rn], #+/-

[Rn], {8-bit copro. option}

Post-indexed

Unindexed

ARM architecture versions

n

nT

M

nE

ARM architecture version n and above.

T variants of ARM architecture version n and above.

ARM architecture version 3M, and 4 and above excluding xM variants

E variants of ARM architecture version n and above.

Allowed shifts 0-31

Allowed shifts 1-32

Allowed shifts 1-32

Allowed shifts 1-31

Operand 2

Immediate value

Logical shift left immediate

Logical shift right immediate

Arithmetic shift right immediate

Rotate right immediate

Register

Rotate right extended

Logical shift left register

Logical shift right register

Arithmetic shift right register

Rotate right register

#

Rm, LSL #

Rm, LSR #

Rm, ASR #

Rm, ROR #

Rm

Rm, RRX

Rm, LSL Rs

Rm, LSR Rs

Rm, ASR Rs

Rm, ROR Rs

PSR fields

(use at least one suffix)

Suffix

c

f

s

x

Meaning

Control field mask byte

Flags field mask byte

Status field mask byte

Extension field mask byte

PSR[7:0]

PSR[31:24]

PSR[23:16]

PSR[15:8]

Allowed shifts 0-31

Allowed shifts 1-32

Allowed shifts 1-32

Allowed shifts 1-31

Equivalent to [Rn],#0

Allowed shifts 0-31

Allowed shifts 1-32

Allowed shifts 1-32

Allowed shifts 1-31

Equivalent to [Rn,#0]

Condition Field {cond}

Mnemonic

Description

EQ

NE

CS / HS

CC / LO

MI

PL

VS

VC

HI

LS

GE

LT

GT

LE

AL

Equal

Not equal

Carry Set / Unsigned higher or same

Carry Clear / Unsigned lower

Negative

Positive or zero

Overflow

No overflow

Unsigned higher

Unsigned lower or same

Signed greater than or equal

Signed less than

Signed greater than

Signed less than or equal

Always (normally omitted)

Description (VFP)

Equal

Not equal, or unordered

Greater than or equal, or unordered

Less than

Less than

Greater than or equal, or unordered

Unordered (at least one NaN operand)

Not unordered

Greater than, or unordered

Less than or equal

Greater than or equal

Less than, or unordered

Greater than

Less than or equal, or unordered

Always (normally omitted)

Equivalent to [Rn,#0]

Key to tables

Updates base register after data transfer if ! present. (Post-indexed always updates.)

{!}

A 32-bit constant, formed by right-rotating an 8-bit value by an even number of bits.

+/-

+ or -. (+ may be omitted.)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc