基于 Buck 同步整流电路中功率 MOSFETS 管参数的优化

华晓辉 1 林维明 2

1 2)福州大学电气工程与自动化学院 福州 350002

1) Email:hxh_1889@126.com 2) Email:weiming @fzu.edu.cn

摘 要 本文是分析 BUCK 同步整流电路中开关管与整流管的损耗模型,以两支管的损耗最小为目标,并以输入电压

=1.8V,开关频率 sf =5MHZ 为例,用 MATLAB 工具对其进行优化计算,得出该条件下器件物

INV =5V,输出电压 OUTV

理参数。

关键词 SR-Buck, MOSFET 损耗模型 , MATLAB 优化

1.引言

MOSFET现已成为高频开关变换器、微处理器与

半导体存储器等先进集成电路(IC)中最主要的器件单

元,它尺寸小、功耗低、并与数字电路的主流工艺兼

容。近年来,使用 MOSFET 的模拟 IC 逐渐已成为主

流,改变了以往主要使用双极型器件的局面。GENFET

MOSFET 器件就采用了 Genera l Semiconductor 公司的

0.35um深槽工艺制造出了每平方英寸含 200M 单元,

集成度提高了 4 倍,更加适合了移动电话机,笔记本

电脑,PDA 以及其它的无线电产品的应用。因此在高

功率密度集成 Buck 同步整流电路中,确定 MOSFET

的损耗模型,优化电路中主开关管与同步整流管的最

小损耗模型显得十分重要。

2.寄生参数

随着器件尺寸的不断减小,电路模拟程序中的器

件模型也越来越复杂,以保证模拟结果的精确度;然

而电路的模拟精确度不仅与器件模型有关,还与给定

的器件模型参数有关。

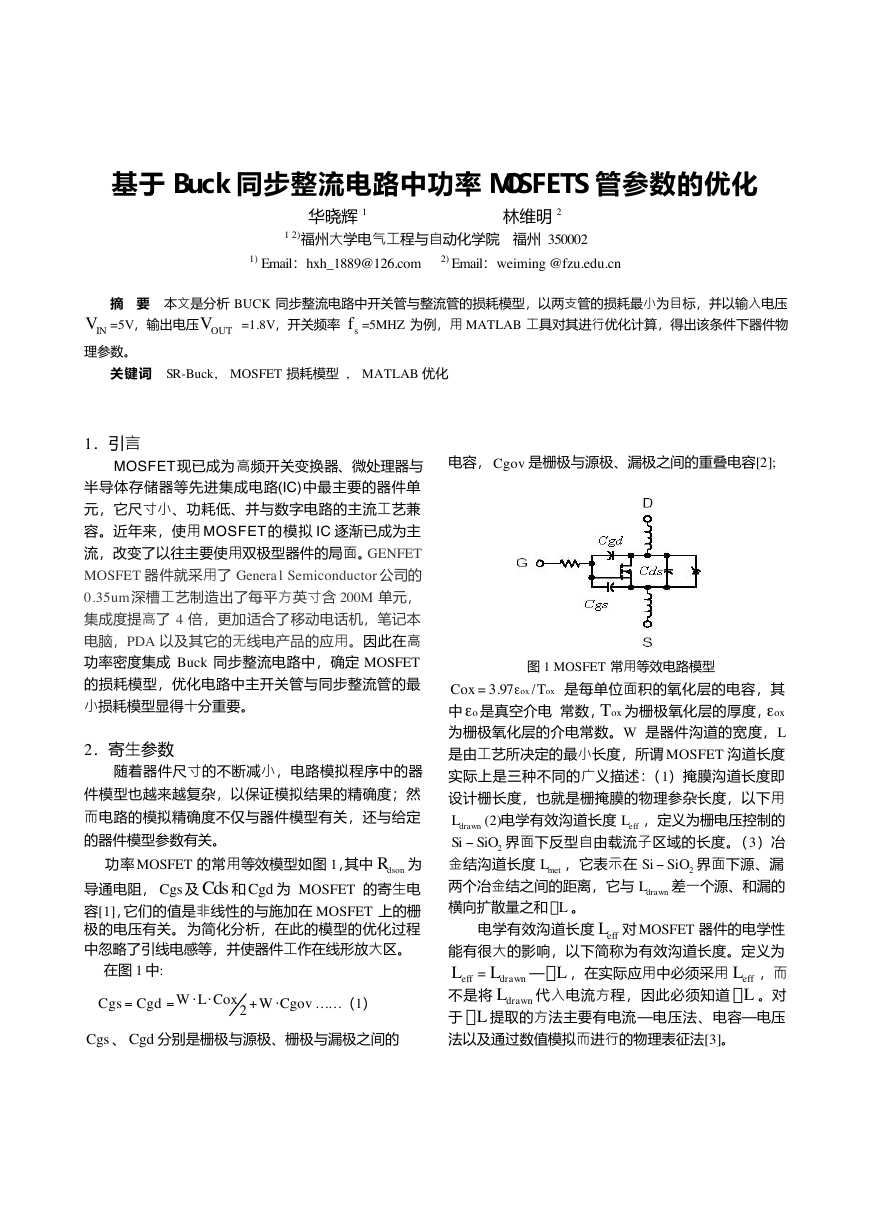

功率 MOSFET 的常用等效模型如图 1,其中 dsonR 为

导通电阻, Cgs 及 Cds 和 Cgd 为 MOSFET 的寄生电

容[1],它们的值是非线性的与施加在MOSFET 上的栅

极的电压有关。为简化分析,在此的模型的优化过程

中忽略了引线电感等,并使器件工作在线形放大区。

在图 1 中:

Cgs

=

Cgd

=

LW

Cox

+

W

2

Cgov

… … (1)

Cgs 、 Cgd 分别是栅极与源极、栅极与漏极之间的

电容, Cgov 是栅极与源极、漏极之间的重叠电容[2];

图 1 MOSFET 常用等效电路模型

ox T/

ox

e

97.3

Cox =

是每单位面积的氧化层的电容,其

中 oe 是真空介电 常数, oxT 为栅极氧化层的厚度, oxe

为栅极氧化层的介电常数。W 是器件沟道的宽度,L

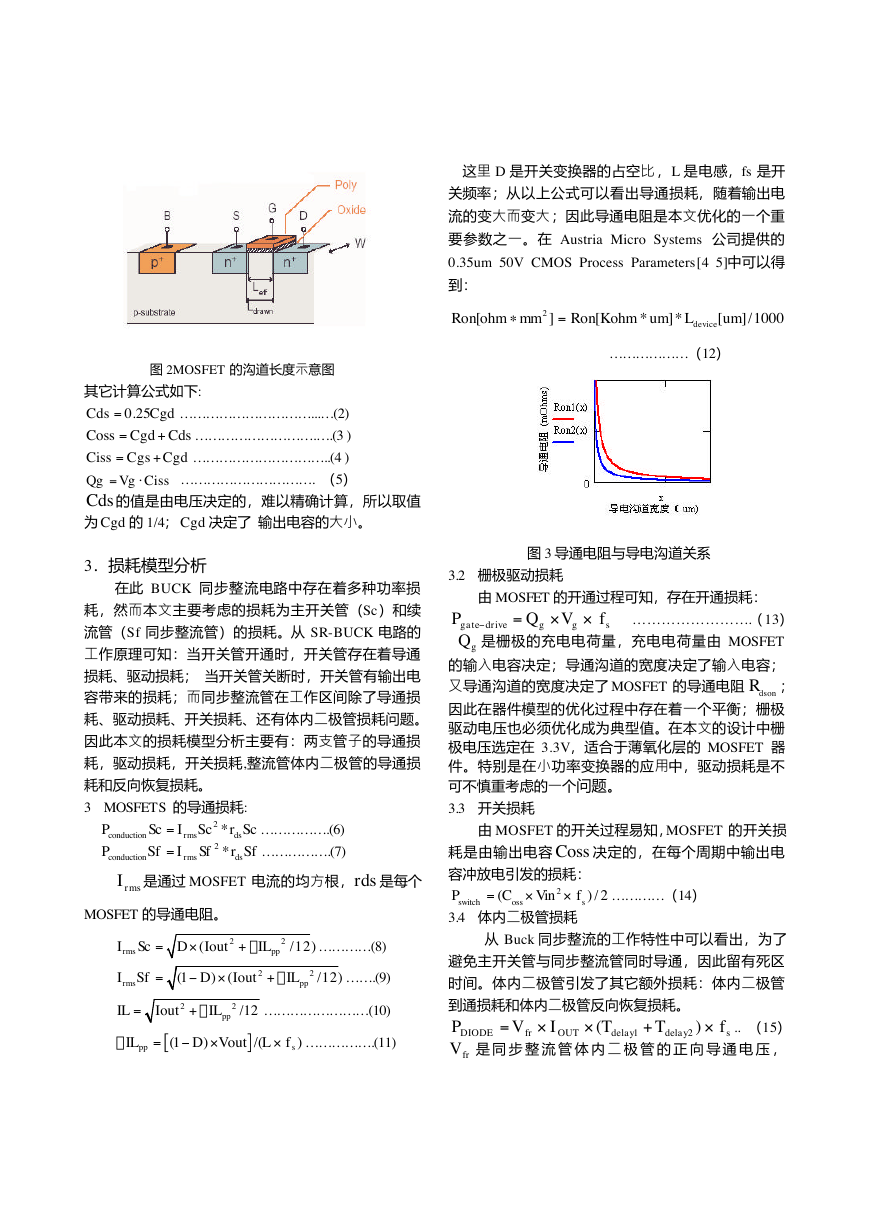

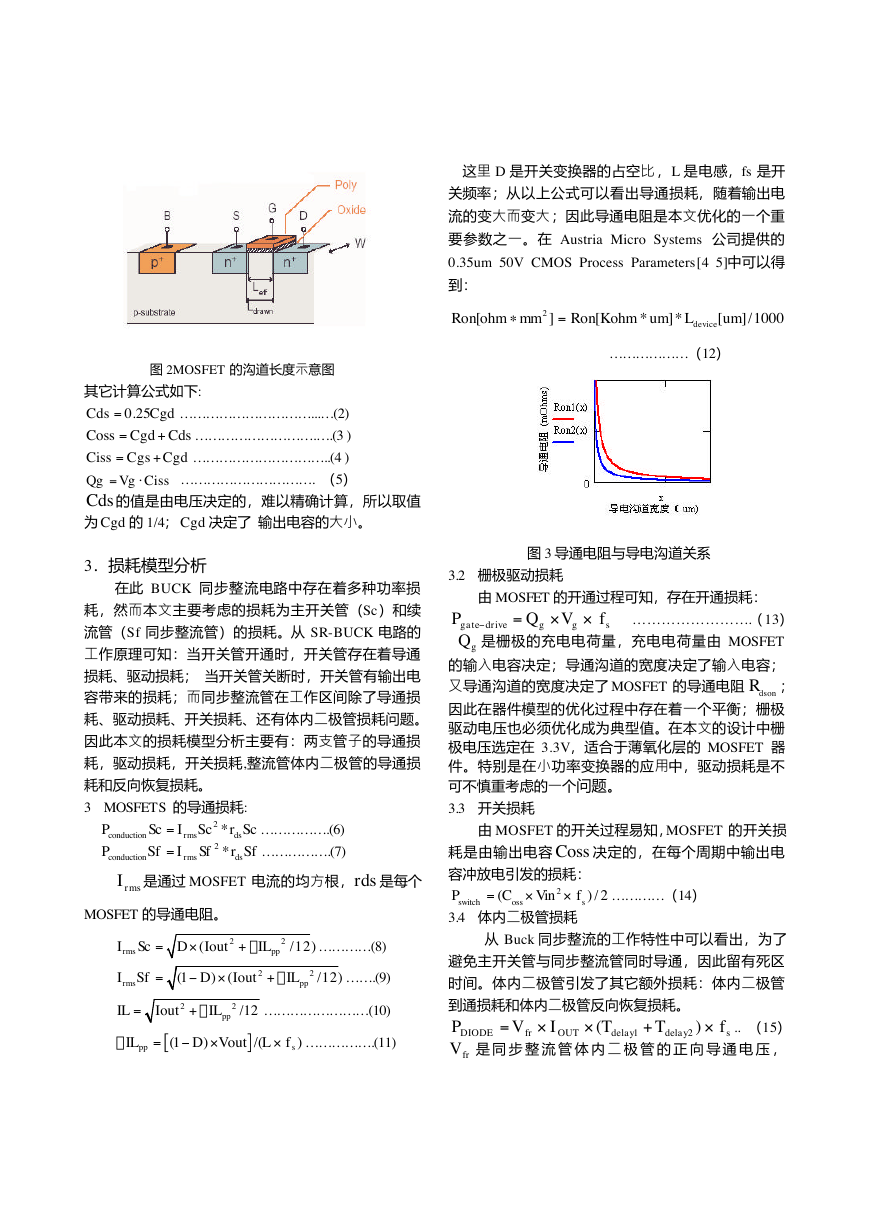

是由工艺所决定的最小长度,所谓 MOSFET 沟道长度

实际上是三种不同的广义描述:(1)掩膜沟道长度即

设计栅长度,也就是栅掩膜的物理参杂长度,以下用

L

(2)电学有效沟道长度 effL ,定义为栅电压控制的

drawn

SiSiO-

界面下反型自由载流子区域的长度。(3)冶

Si -

金结沟道长度 metL ,它表示在

界面下源、漏

L 差一个源、和漏的

两个冶金结之间的距离,它与 drawn

横向扩散量之和 LD 。

SiO

2

2

电学有效沟道长度 effL 对 MOSFET 器件的电学性

能有很大的影响,以下简称为有效沟道长度。定义为

— LD ,在实际应用中必须采用 effL ,而

effL = drawn

代入电流方程,因此必须知道 LD 。对

不是将 drawn

于 LD 提取的方法主要有电流—电压法、电容—电压

法以及通过数值模拟而进行的物理表征法[3]。

L

L

�

2

图 2MOSFET 的沟道长度示意图

其它计算公式如下:

CdsCgd=

0.25

=

+

Cgd

Coss

Cds

+

=

Ciss

Cgs

Cgd

=

Ciss

Vg

Qg

Cds 的值是由电压决定的,难以精确计算,所以取值

为 Cgd 的 1/4; Cgd 决定了 输出电容的大小。

… … … … … … … … … … ...… (2)

… … … … … … … … … .… .(3 )

… … … … … … … … … … ..(4 )

… … … … … … … … … … . (5)

3.损耗模型分析

在此 BUCK 同步整流电路中存在着多种功率损

耗,然而本文主要考虑的损耗为主开关管(Sc)和续

流管(Sf 同步整流管)的损耗。从 SR-BUCK 电路的

工作原理可知:当开关管开通时,开关管存在着导通

损耗、驱动损耗; 当开关管关断时,开关管有输出电

容带来的损耗;而同步整流管在工作区间除了导通损

耗、驱动损耗、开关损耗、还有体内二极管损耗问题。

因此本文的损耗模型分析主要有:两支管子的导通损

耗,驱动损耗,开关损耗,整流管体内二极管的导通损

耗和反向恢复损耗。

3 MOSFETS 的导通损耗:

PSc

conductionrmsds

PSf

conductionrmsds

IScrSc=

ISfrSf=

2 *

2 *

… … … … … .(6)

… … … … … .(7)

I 是通过 MOSFET 电流的均方根,rds 是每个

rms

MOSFET 的导通电阻。

rmspp

IScDIoutIL=·+ D

ISfDIoutIL=-

·+ D

rmspp

=+ D

ILIoutIL

[

D=

2

(/12)

2

… … … … (8)

(1)(/12)

2

2

… … .(9)

2

pp

2 /12

]

)

… … … … … … … … (10)

… … … … … .(11)

s

ILDVout L f

(1)/(

pp

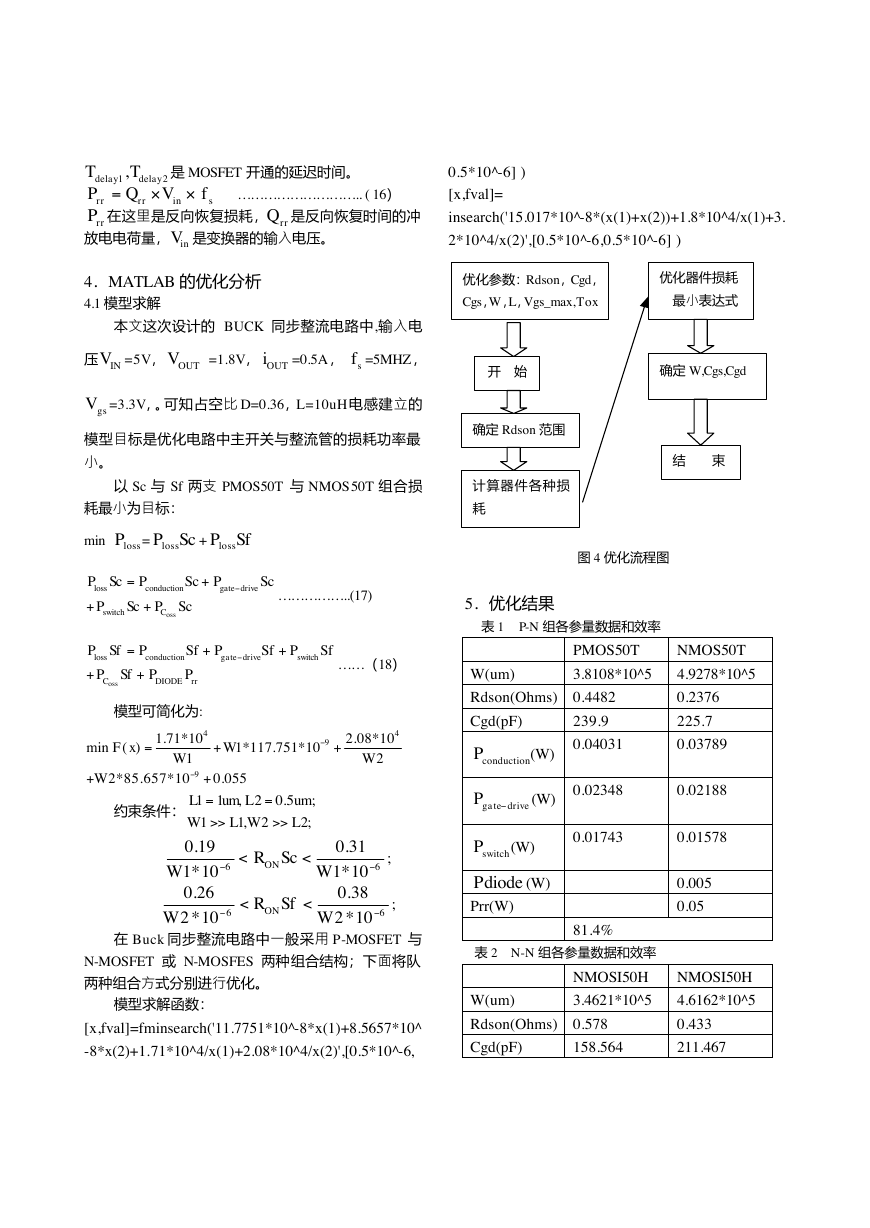

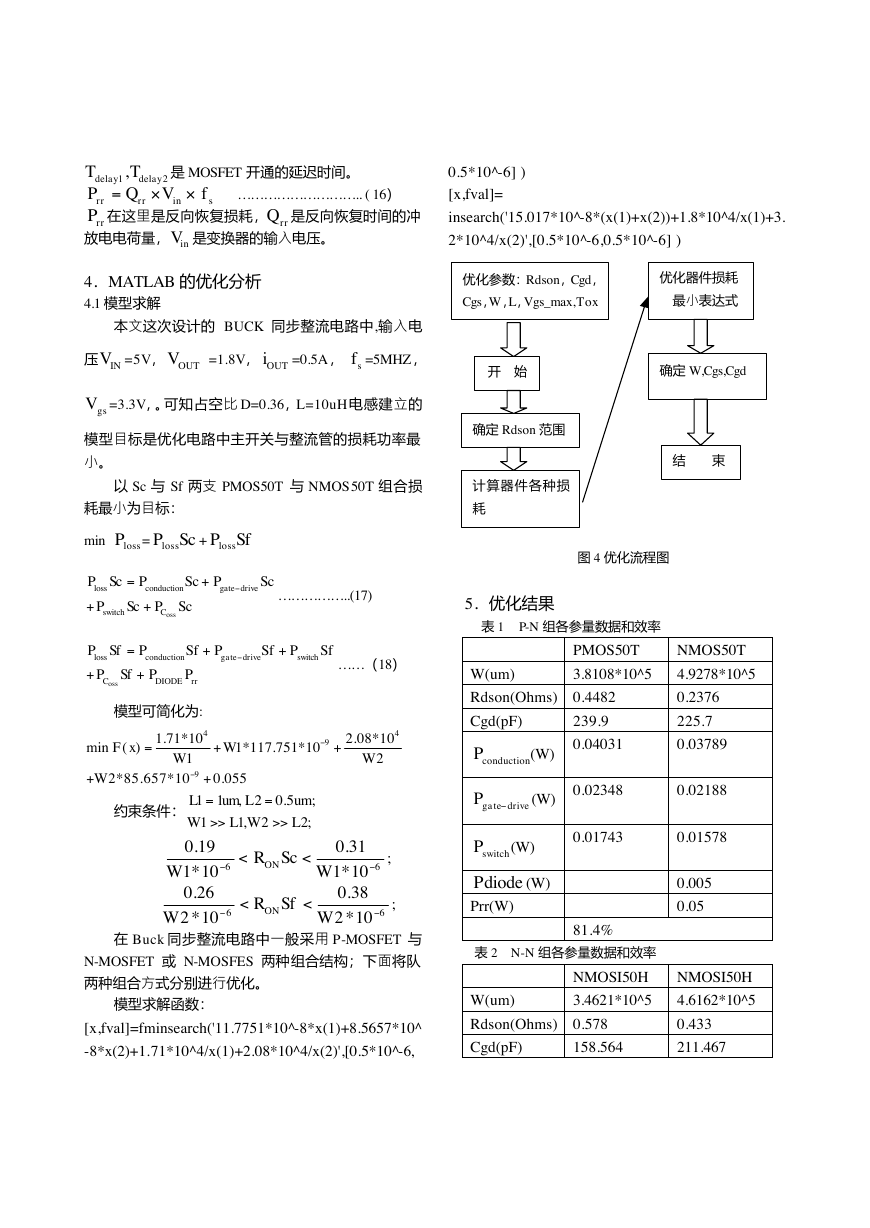

这里 D 是开关变换器的占空比,L 是电感,fs 是开

关频率;从以上公式可以看出导通损耗,随着输出电

流的变大而变大;因此导通电阻是本文优化的一个重

要参数之一。在 Austria Micro Systems 公司提供的

0.35um 50V CMOS Process Parameters[4 5]中可以得

到:

[

ohm

Ron

2

mm

]

=

Ron

[

Kohm

*

um

*]

L

[

um

/]

1000

device

… … … … … … (12)

图 3 导通电阻与导电沟道关系

3.2 栅极驱动损耗

=

由 MOSFET 的开通过程可知,存在开通损耗:

s

g

g

f

drive

VQ

P

… … … … … … … … .(13)

gate

gQ 是栅极的充电电荷量,充电电荷量由 MOSFET

的输入电容决定;导通沟道的宽度决定了输入电容;

又导通沟道的宽度决定了 MOSFET 的导通电阻 dsonR ;

因此在器件模型的优化过程中存在着一个平衡;栅极

驱动电压也必须优化成为典型值。在本文的设计中栅

极电压选定在 3.3V,适合于薄氧化层的 MOSFET 器

件。特别是在小功率变换器的应用中,驱动损耗是不

可不慎重考虑的一个问题。

3.3 开关损耗

由 MOSFET 的开关过程易知,MOSFET 的开关损

耗是由输出电容 Coss 决定的,在每个周期中输出电

容冲放电引发的损耗:

=

PCVin

switchoss

3.4 体内二极管损耗

… … … … (14)

() / 2

f

2

s

从 Buck 同步整流的工作特性中可以看出,为了

避免主开关管与同步整流管同时导通,因此留有死区

时间。体内二极管引发了其它额外损耗:体内二极管

到通损耗和体内二极管反向恢复损耗。

P

.. (15)

DIODE

frV 是 同 步 整 流 管 体 内 二 极 管 的 正 向 导 通 电 压 ,

delay

1

T

(

delay

OUT

V

+

=

T

I

)

fr

f

s

2

-

·

·

*

·

·

-

·

·

·

·

·

�

1, delay

2

=

VQ

是 MOSFET 开通的延迟时间。

delay T

T

P

rr

rr

rrP 在这里是反向恢复损耗, rrQ 是反向恢复时间的冲

放电电荷量, inV 是变换器的输入电压。

… … … … … … … … … .. ( 16)

in

f

s

4.MATLAB 的优化分析

4.1 模型求解

本文这次设计的 BUCK 同步整流电路中,输入电

压 INV =5V, OUTV

=1.8V, OUT

i

=0.5A, sf =5MHZ,

gsV =3.3V,。可知占空比D=0.36,L=10uH电感建立的

模型目标是优化电路中主开关与整流管的损耗功率最

小。

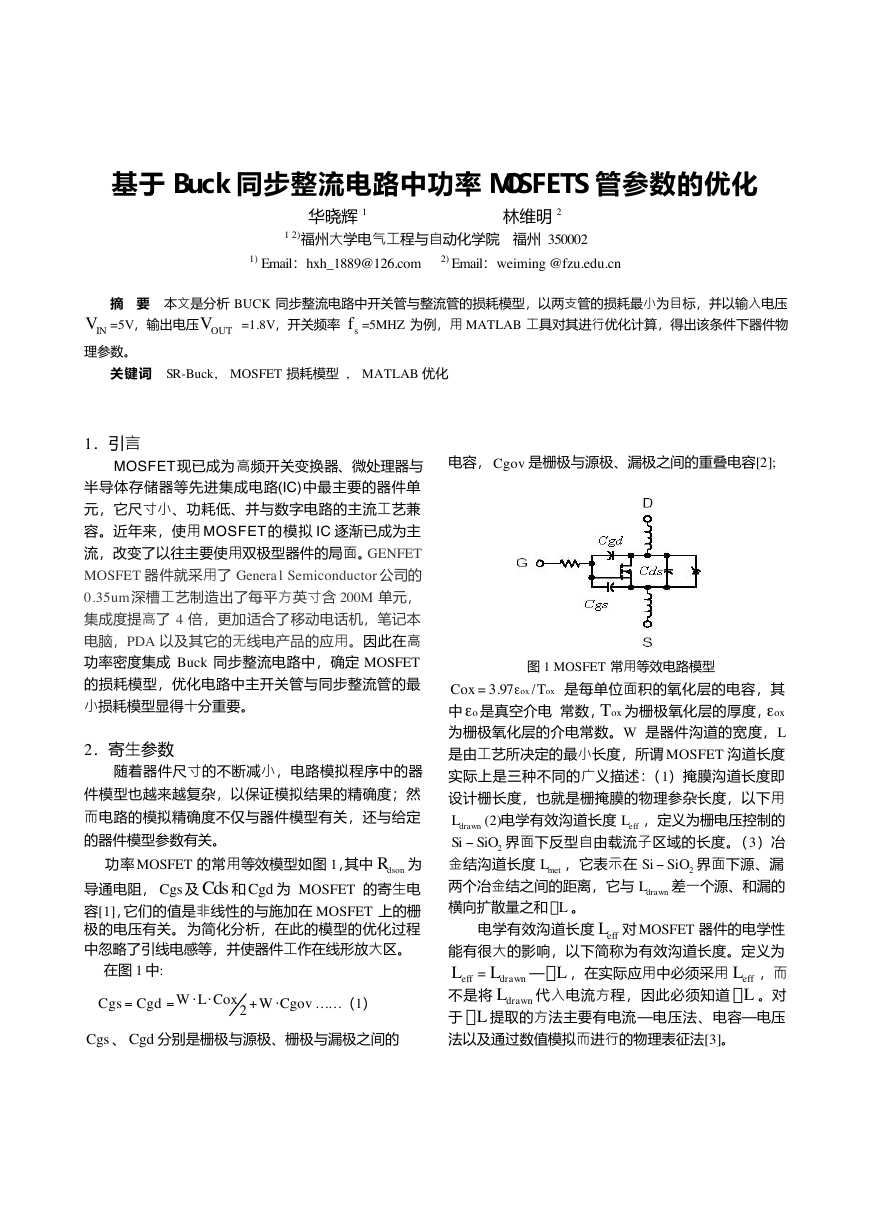

以 Sc 与 Sf 两支 PMOS50T 与 NMOS50T 组合损

耗最小为目标:

Ploss

lossP =

min

Sc

=

PScPScPSc

lossconductiongatedrive

+

+

PSc PSc

switch

C

oss

+

Ploss

Sf

+

优化器件损耗

最小表达式

优化参数:Rdson,Cgd,

Cgs,W,L,Vgs_max,Tox

0.5*10^-6] )

[x,fval]=

insearch('15.017*10^-8*(x(1)+x(2))+1.8*10^4/x(1)+3.

2*10^4/x(2)',[0.5*10^-6,0.5*10^-6] )

确定 Rdson 范围

计算器件各种损

确定 W,Cgs,Cgd

结 束

开 始

耗

… … … … … ..(17)

5.优化结果

表 1 P-N 组各参量数据和效率

图 4 优化流程图

=

PSfPSfPSfPSf

lossconductiongatedriveswitch

+

+

PSfP

P

CDIODErr

oss

+

+

… … (18)

模型可简化为:

4

min()1*117.751*10

1.71*102.08*10

=+

Fx

W

+

9

4

W

2

+

W

W

1

9

L

约束条件:

+

2*85.657*100.055

=

=

1 1 , 20.5

LumLum

>>>>

11,22;

WLW

19.0

10*1

26.0

10*2

W

W

R

R

<

<

ON

ON

6

6

;

<

Sc

<

Sf

31.0

10*1

38.0

10*2

W

W

;

6

;

6

在 Buck 同步整流电路中一般采用 P-MOSFET 与

N-MOSFET 或 N-MOSFES 两种组合结构;下面将队

两种组合方式分别进行优化。

模型求解函数:

[x,fval]=fminsearch('11.7751*10^-8*x(1)+8.5657*10^

-8*x(2)+1.71*10^4/x(1)+2.08*10^4/x(2)',[0.5*10^-6,

PMOS50T

3.8108*10^5

W(um)

Rdson(Ohms) 0.4482

239.9

Cgd(pF)

0.04031

P

conduction

(W)

NMOS50T

4.9278*10^5

0.2376

225.7

0.03789

gateP -

drive

(W) 0.02348

0.02188

(W)

switchP

Pdiode (W)

Prr(W)

0.01743

0.01578

81.4%

0.005

0.05

表 2 N-N 组各参量数据和效率

NMOSI50H

3.4621*10^5

W(um)

Rdson(Ohms) 0.578

Cgd(pF)

158.564

NMOSI50H

4.6162*10^5

0.433

211.467

·

·

-

-

-

-

-

-

-

-

�

P

conduction

(W)

0.052

0.04

(W)

switchP

Pdiode (W) 0.012

75.2%

0.069

0.053

0.016

0.005

0.05

图 4 中 MOSFET 的优化模型[6 7 8]所需参数可参

照 AMS H35 CMOS 工艺的参数和其它模型(如SPICE

模型)的器件参数。从表 1、2 可以看出在 Buck 同步

整流电路中,采用 P-N 形式的 MOSFETS 组合比 N-N

形式组合效率高,并且在Buck 同步整流电路中主开关

管采用 P-MOSFET 较容易驱动,但是 P-N 形式组合下

器件的宽度比 N-N 组合大,这就以增加器件结构的体

积为代价,它们的总宽度是有上千个 50um MOSFETS

来完成的,如图 5 是以前的 MOSFET 结构与新型

MOSFET 结构的区别。以上的两组数据 P-N 组合的是

在 0.35um CMOS 工艺下的 MOS HV Thin-Oxide 的

MOSFET,因此 gV =3.3V;而 N-N 组合选择的参数来

自与 MOS HV Middle-Oxide MOSFET,

gV =5V。

图 5 新旧工艺下 MOSFET 结构的比较

6.结论

本文在 Buck 同步整流电路( INV =5V, OUTV

=1.8V, sf =5MH)中,用 MATLAB 工具建立功率

MOSFETS 的损耗优化模型,通过几种类型的管子组

合,综合考虑性价比,来确定器件沟道的尺寸参数,

同时还可以通过增加氧化层的厚度来提高效率。上述

过程中 MOSFETS 的体内二极管反向恢复损耗始终占

据着不小比例,如何克服这些难题都对高频下的小功

率 DC-DC 变换器的集成化,提高功率密度具有重要

意义。并通过了 P-N 与 N-N 两种组合的效率比较,得

出 P-N 型的两个管子组合效率高于后者。以上模型参

数选取是在 L=10uH 的情况下进行的,以后的优化电

路将包含电感这一参数进行多目标的优化,这将对整

个 Buck 同步整流电路的整机效率的提高有着更为实

际的意义。

参考文献

[1]. Balogh, Laszlo ,Design and Application Guide for High

Speed MOSFET Gate Drive Circuits

SEM-1400,TI,Seminar 2001

[2]. Ritu Shrivastava ,A Simple For the Overlap Capacitance

. Electron Device,IEEE

1982

of a VLSI MOS Device

on

transactions

volume

Page(s):1870-1875

29,Issue12,Dec

[3]. B.Van Zeghbroeck. Princciples of Semiconductor Devices

Colorado University press, 2004

[4]. AMS H35 Process Parameters Document

Eng.-238_rev2. http://asic.austriamicrocystems.com

[5]. 0.35um 50v CMOS Process Parameters

http://www.charteredsemi.com

[6]. Hua Su Christopher Michael Mohammed Ismail .Yield

Integrated Circuits

ISCAS’93

Optimization of Analog MOS

Including Transistor Mismatch

Page(s):1801-1804

IEEE

[7]. C.Cavallro K.Shenm .Analysis modeling and simulation of

in Synchronous-Rectifier

IEEE –IECON’03

Low-Voltage MOSFETS

Buck-Converter Applications.

Page(s):1697-1702 Vol.2

[8]. Richared K.Williams Bijian E.Monhandes .Optimization

of complementary POWER DMOSFETS for low-voltage

high frequency dc-dc conversion IEEE APEC 1995

Page(s): 765-722

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc