1 General Description

1.1 Features

1.2 QCA9531 System Block Diagram

2 Pin Descriptions

3 Functional Description

3.1 Functional Block Diagram

3.2 Bootstrap Options

3.3 Reset

3.4 PLL and Clock Control

3.4.1 Full Chip Clocking Structure

3.4.2 PLL

3.4.3 DDR PLL

3.4.4 Ethernet PLL

3.5 MIPS Processor

3.6 Address Map

3.7 DDR Memory Controller

3.7.1 DDR Configurations

3.7.2 DDR Initialization Sequences

3.7.3 DDR Memory Initialization

3.7.4 CPU DDR Address Mapping

3.7.5 Refresh

3.7.6 Self Refresh

3.8 PCIE RC

3.8.1 Power Management

3.8.2 Interrupts

3.8.3 Error Reporting Capability and Status Checking

3.8.4 Byte-Swap Option

3.8.5 Request Sizes and Payloads

3.9 GPIO

3.9.1 GPIO Output

3.9.2 GPIO Input

3.10 Serial Flash SPI/ROM

3.10.1 SPI Operations

3.10.2 Write Enable

3.10.3 Page Program

3.10.4 Page Read

3.11 Low-Speed UART Interface

3.12 USB 2.0 Interface

4 WLAN Medium Access Control (MAC)

4.1 Overview

4.2 Descriptor

4.3 Descriptor Format

4.4 Queue Control Unit (QCU)

4.5 DCF Control Unit (DCU)

4.6 Protocol Control Unit (PCU)

4.7 Register Programming Details for Observing WMAC Interrupts

5 Digital PHY Block

5.1 Overview

5.2 802.11n (MIMO) Mode

5.2.1 Transmitter (Tx)

5.2.2 Receiver (Rx)

5.3 802.11 b/g Legacy Mode

5.3.1 Transmitter

5.3.2 Receiver

6 Radio Block

6.1 Receiver (Rx) Block

6.2 Transmitter (Tx) Block

6.3 Synthesizer (SYNTH) Block

6.4 Bias/Control (BIAS) Block

7 Register Descriptions

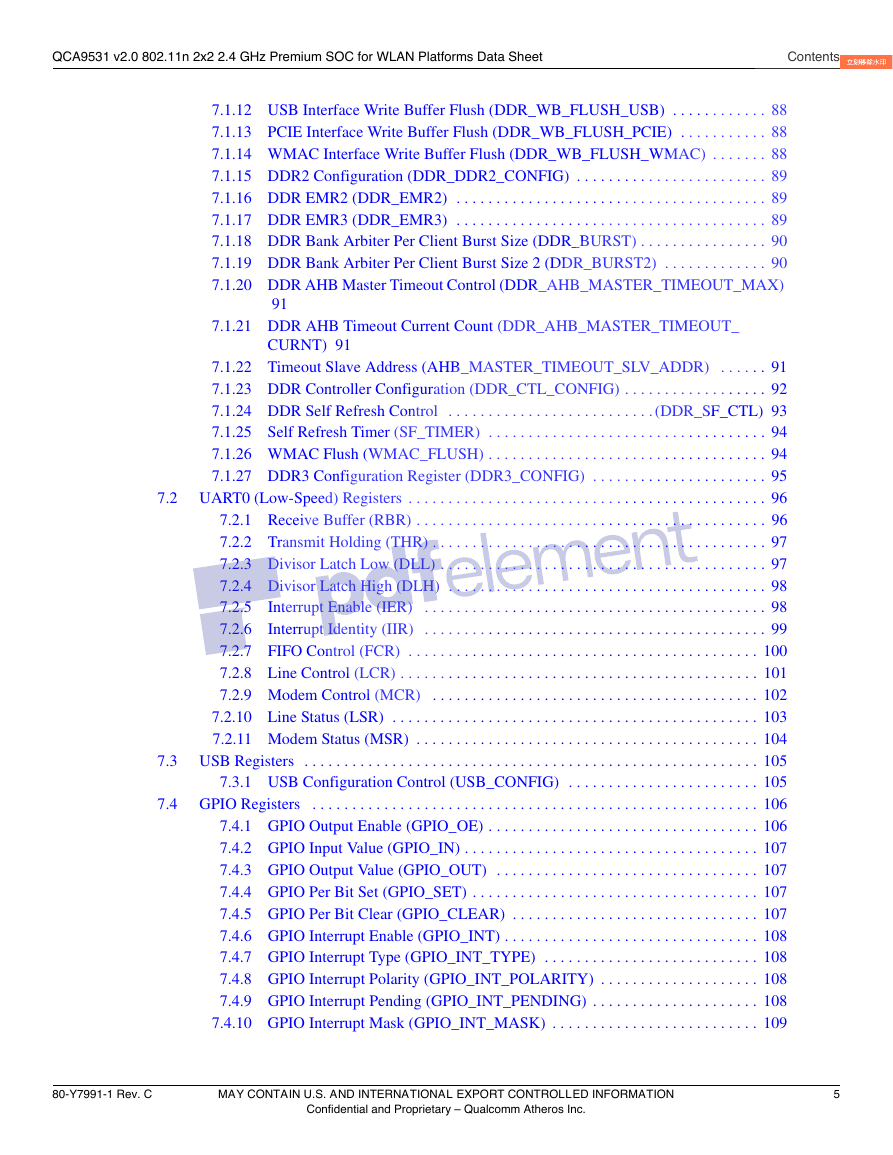

7.1 DDR Registers

7.1.1 DDR DRAM Configuration (DDR_CONFIG)

7.1.2 DDR DRAM Configuration 2 (DDR_CONFIG2)

7.1.3 DDR Mode Value (DDR_MODE_REGISTER)

7.1.4 DDR Extended Mode (DDR_EXTENDED_MODE_REGISTER)

7.1.5 DDR Control (DDR_CONTROL)

7.1.6 DDR Refresh Control and Configuration (DDR_REFRESH)

7.1.7 DDR Read Data Capture Bit Mask (DDR_RD_DATA_THIS_ CYCLE)

7.1.8 DQS Delay Tap Control for Byte 0 (TAP_CONTROL_0)

7.1.9 DQS Delay Tap Control for Byte 1 (TAP_CONTROL_1)

7.1.10 GE0 Interface Write Buffer Flush (DDR_WB_FLUSH_GE0)

7.1.11 GE1 Interface Write Buffer Flush (DDR_WB_FLUSH_GE1)

7.1.12 USB Interface Write Buffer Flush (DDR_WB_FLUSH_USB)

7.1.13 PCIE Interface Write Buffer Flush (DDR_WB_FLUSH_PCIE)

7.1.14 WMAC Interface Write Buffer Flush (DDR_WB_FLUSH_WMAC)

7.1.15 DDR2 Configuration (DDR_DDR2_CONFIG)

7.1.16 DDR EMR2 (DDR_EMR2)

7.1.17 DDR EMR3 (DDR_EMR3)

7.1.18 DDR Bank Arbiter Per Client Burst Size (DDR_BURST)

7.1.19 DDR Bank Arbiter Per Client Burst Size 2 (DDR_BURST2)

7.1.20 DDR AHB Master Timeout Control (DDR_AHB_MASTER_ TIMEOUT_MAX)

7.1.21 DDR AHB Timeout Current Count (DDR_AHB_MASTER_ TIMEOUT_CURNT)

7.1.22 Timeout Slave Address (AHB_MASTER_TIMEOUT_SLV_ ADDR)

7.1.23 DDR Controller Configuration (DDR_CTL_CONFIG)

7.1.24 DDR Self Refresh Control (DDR_SF_CTL)

7.1.25 Self Refresh Timer (SF_TIMER)

7.1.26 WMAC Flush (WMAC_FLUSH)

7.1.27 DDR3 Configuration Register (DDR3_CONFIG)

7.2 UART0 (Low-Speed) Registers

7.2.1 Receive Buffer (RBR)

7.2.2 Transmit Holding (THR)

7.2.3 Divisor Latch Low (DLL)

7.2.4 Divisor Latch High (DLH)

7.2.5 Interrupt Enable (IER)

7.2.6 Interrupt Identity (IIR)

7.2.7 FIFO Control (FCR)

7.2.8 Line Control (LCR)

7.2.9 Modem Control (MCR)

7.2.10 Line Status (LSR)

7.2.11 Modem Status (MSR)

7.3 USB Registers

7.3.1 USB Configuration Control (USB_CONFIG)

7.4 GPIO Registers

7.4.1 GPIO Output Enable (GPIO_OE)

7.4.2 GPIO Input Value (GPIO_IN)

7.4.3 GPIO Output Value (GPIO_OUT)

7.4.4 GPIO Per Bit Set (GPIO_SET)

7.4.5 GPIO Per Bit Clear (GPIO_CLEAR)

7.4.6 GPIO Interrupt Enable (GPIO_INT)

7.4.7 GPIO Interrupt Type (GPIO_INT_TYPE)

7.4.8 GPIO Interrupt Polarity (GPIO_INT_POLARITY)

7.4.9 GPIO Interrupt Pending (GPIO_INT_PENDING)

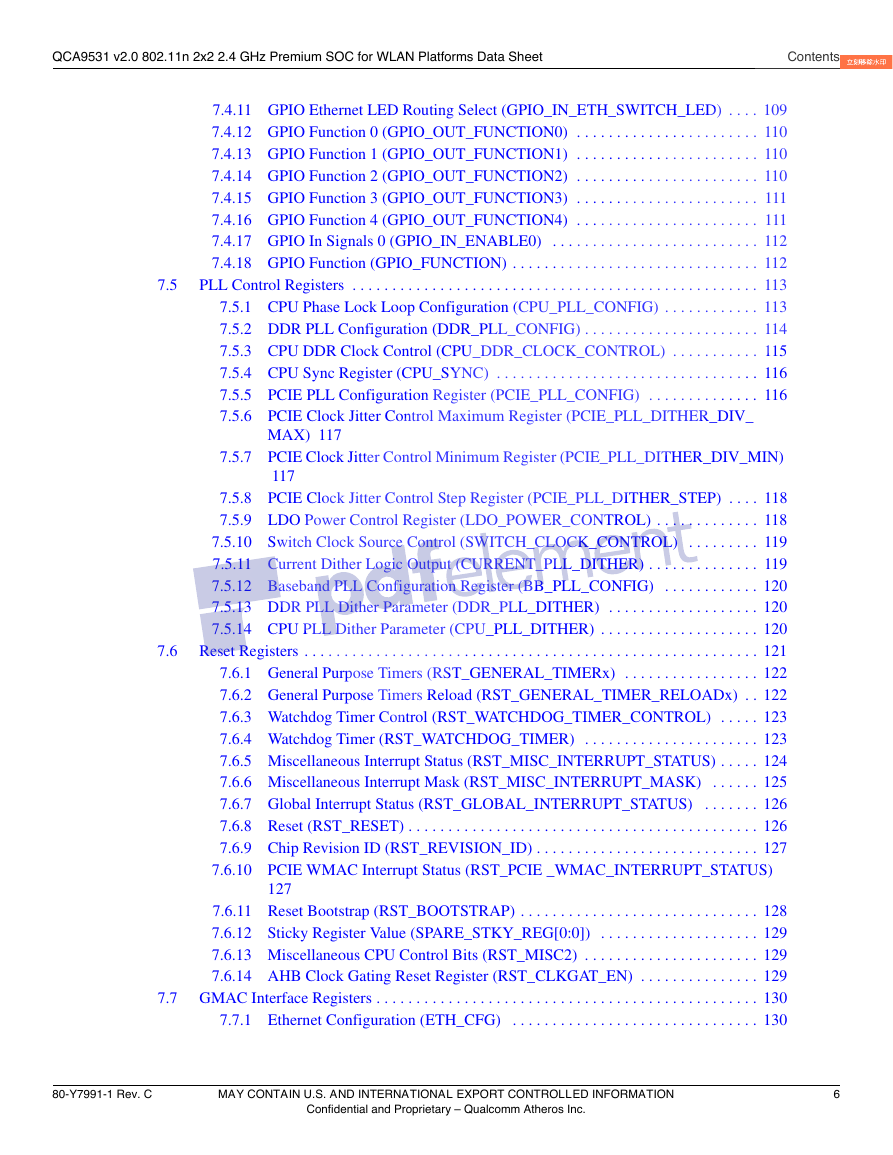

7.4.10 GPIO Interrupt Mask (GPIO_INT_MASK)

7.4.11 GPIO Ethernet LED Routing Select (GPIO_IN_ETH_SWITCH_ LED)

7.4.12 GPIO Function 0 (GPIO_OUT_FUNCTION0)

7.4.13 GPIO Function 1 (GPIO_OUT_FUNCTION1)

7.4.14 GPIO Function 2 (GPIO_OUT_FUNCTION2)

7.4.15 GPIO Function 3 (GPIO_OUT_FUNCTION3)

7.4.16 GPIO Function 4 (GPIO_OUT_FUNCTION4)

7.4.17 GPIO In Signals 0 (GPIO_IN_ENABLE0)

7.4.18 GPIO Function (GPIO_FUNCTION)

7.5 PLL Control Registers

7.5.1 CPU Phase Lock Loop Configuration (CPU_PLL_CONFIG)

7.5.2 DDR PLL Configuration (DDR_PLL_CONFIG)

7.5.3 CPU DDR Clock Control (CPU_DDR_CLOCK_CONTROL)

7.5.4 CPU Sync Register (CPU_SYNC)

7.5.5 PCIE PLL Configuration Register (PCIE_PLL_CONFIG)

7.5.6 PCIE Clock Jitter Control Maximum Register (PCIE_PLL_ DITHER_DIV_MAX)

7.5.7 PCIE Clock Jitter Control Minimum Register (PCIE_PLL_ DITHER_DIV_MIN)

7.5.8 PCIE Clock Jitter Control Step Register (PCIE_PLL_DITHER_ STEP)

7.5.9 LDO Power Control Register (LDO_POWER_CONTROL)

7.5.10 Switch Clock Source Control (SWITCH_CLOCK_CONTROL)

7.5.11 Current Dither Logic Output (CURRENT_PLL_DITHER)

7.5.12 Baseband PLL Configuration Register (BB_PLL_CONFIG)

7.5.13 DDR PLL Dither Parameter (DDR_PLL_DITHER)

7.5.14 CPU PLL Dither Parameter (CPU_PLL_DITHER)

7.6 Reset Registers

7.6.1 General Purpose Timers (RST_GENERAL_TIMERx)

7.6.2 General Purpose Timers Reload (RST_GENERAL_TIMER_ RELOADx)

7.6.3 Watchdog Timer Control (RST_WATCHDOG_TIMER_CONTROL)

7.6.4 Watchdog Timer (RST_WATCHDOG_TIMER)

7.6.5 Miscellaneous Interrupt Status (RST_MISC_INTERRUPT_ STATUS)

7.6.6 Miscellaneous Interrupt Mask (RST_MISC_INTERRUPT_MASK)

7.6.7 Global Interrupt Status (RST_GLOBAL_INTERRUPT_STATUS)

7.6.8 Reset (RST_RESET)

7.6.9 Chip Revision ID (RST_REVISION_ID)

7.6.10 PCIE WMAC Interrupt Status (RST_PCIE _WMAC_ INTERRUPT_STATUS)

7.6.11 Reset Bootstrap (RST_BOOTSTRAP)

7.6.12 Sticky Register Value (SPARE_STKY_REG[0:0])

7.6.13 Miscellaneous CPU Control Bits (RST_MISC2)

7.6.14 AHB Clock Gating Reset Register (RST_CLKGAT_EN)

7.7 GMAC Interface Registers

7.7.1 Ethernet Configuration (ETH_CFG)

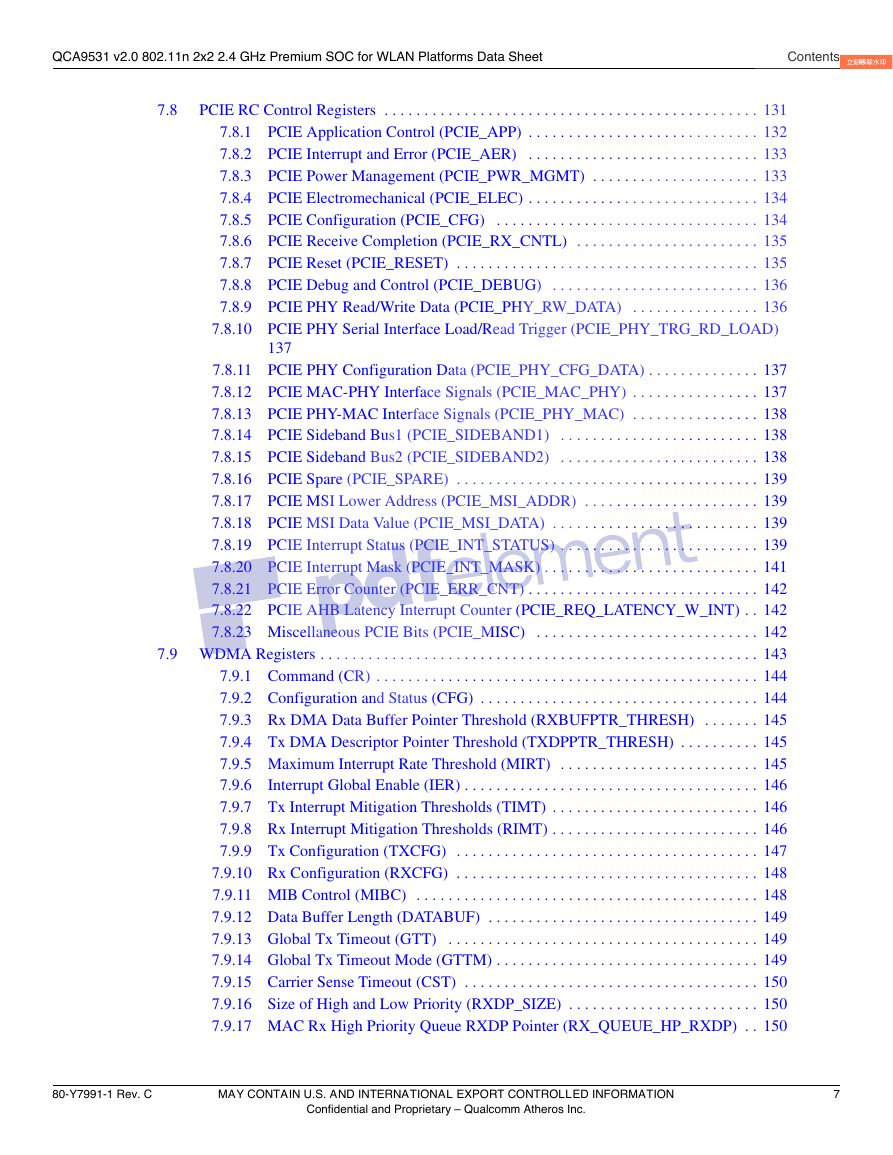

7.8 PCIE RC Control Registers

7.8.1 PCIE Application Control (PCIE_APP)

7.8.2 PCIE Interrupt and Error (PCIE_AER)

7.8.3 PCIE Power Management (PCIE_PWR_MGMT)

7.8.4 PCIE Electromechanical (PCIE_ELEC)

7.8.5 PCIE Configuration (PCIE_CFG)

7.8.6 PCIE Receive Completion (PCIE_RX_CNTL)

7.8.7 PCIE Reset (PCIE_RESET)

7.8.8 PCIE Debug and Control (PCIE_DEBUG)

7.8.9 PCIE PHY Read/Write Data (PCIE_PHY_RW_DATA)

7.8.10 PCIE PHY Serial Interface Load/Read Trigger (PCIE_PHY_ TRG_RD_LOAD)

7.8.11 PCIE PHY Configuration Data (PCIE_PHY_CFG_DATA)

7.8.12 PCIE MAC-PHY Interface Signals (PCIE_MAC_PHY)

7.8.13 PCIE PHY-MAC Interface Signals (PCIE_PHY_MAC)

7.8.14 PCIE Sideband Bus1 (PCIE_SIDEBAND1)

7.8.15 PCIE Sideband Bus2 (PCIE_SIDEBAND2)

7.8.16 PCIE Spare (PCIE_SPARE)

7.8.17 PCIE MSI Lower Address (PCIE_MSI_ADDR)

7.8.18 PCIE MSI Data Value (PCIE_MSI_DATA)

7.8.19 PCIE Interrupt Status (PCIE_INT_STATUS)

7.8.20 PCIE Interrupt Mask (PCIE_INT_MASK)

7.8.21 PCIE Error Counter (PCIE_ERR_CNT)

7.8.22 PCIE AHB Latency Interrupt Counter (PCIE_REQ_LATENCY_ W_INT)

7.8.23 Miscellaneous PCIE Bits (PCIE_MISC)

7.9 WDMA Registers

7.9.1 Command (CR)

7.9.2 Configuration and Status (CFG)

7.9.3 Rx DMA Data Buffer Pointer Threshold (RXBUFPTR_THRESH)

7.9.4 Tx DMA Descriptor Pointer Threshold (TXDPPTR_THRESH)

7.9.5 Maximum Interrupt Rate Threshold (MIRT)

7.9.6 Interrupt Global Enable (IER)

7.9.7 Tx Interrupt Mitigation Thresholds (TIMT)

7.9.8 Rx Interrupt Mitigation Thresholds (RIMT)

7.9.9 Tx Configuration (TXCFG)

7.9.10 Rx Configuration (RXCFG)

7.9.11 MIB Control (MIBC)

7.9.12 Data Buffer Length (DATABUF)

7.9.13 Global Tx Timeout (GTT)

7.9.14 Global Tx Timeout Mode (GTTM)

7.9.15 Carrier Sense Timeout (CST)

7.9.16 Size of High and Low Priority (RXDP_SIZE)

7.9.17 MAC Rx High Priority Queue RXDP Pointer (RX_QUEUE_HP_ RXDP)

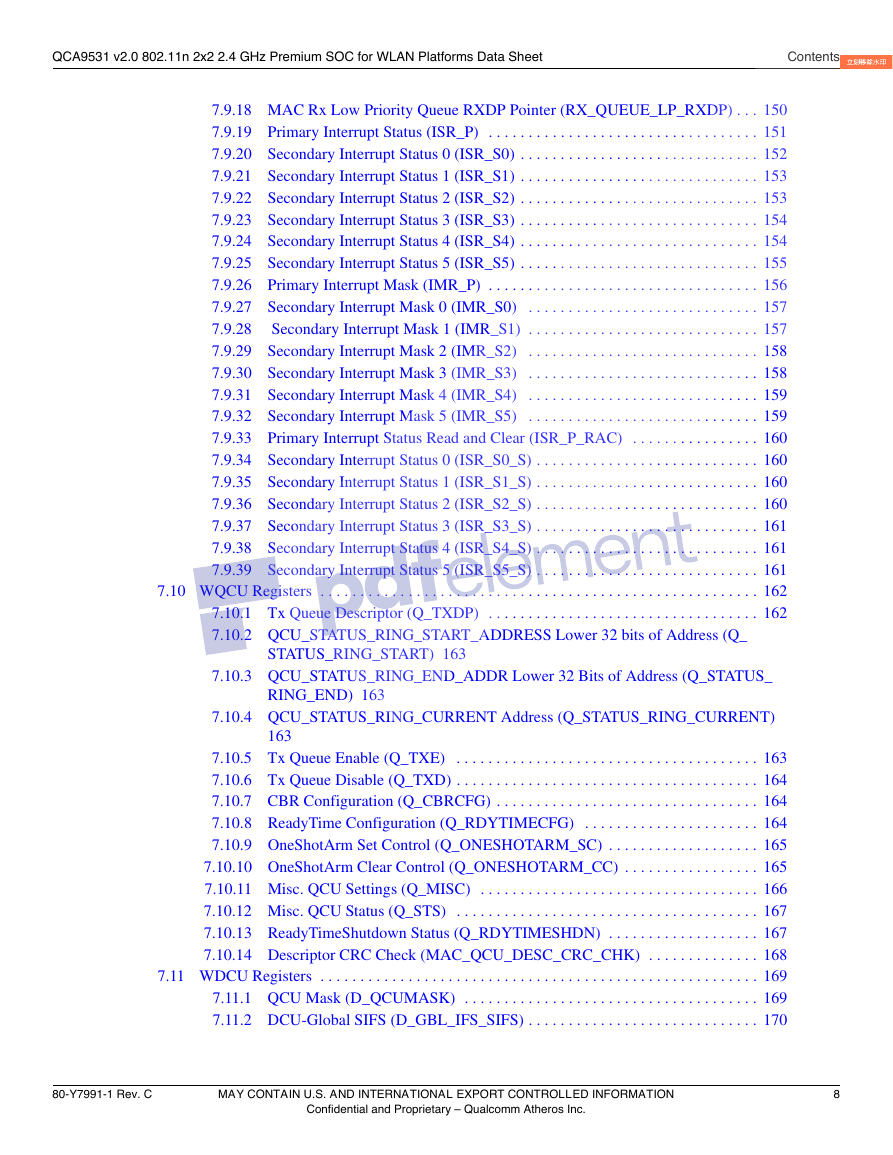

7.9.18 MAC Rx Low Priority Queue RXDP Pointer (RX_QUEUE_LP_ RXDP)

7.9.19 Primary Interrupt Status (ISR_P)

7.9.20 Secondary Interrupt Status 0 (ISR_S0)

7.9.21 Secondary Interrupt Status 1 (ISR_S1)

7.9.22 Secondary Interrupt Status 2 (ISR_S2)

7.9.23 Secondary Interrupt Status 3 (ISR_S3)

7.9.24 Secondary Interrupt Status 4 (ISR_S4)

7.9.25 Secondary Interrupt Status 5 (ISR_S5)

7.9.26 Primary Interrupt Mask (IMR_P)

7.9.27 Secondary Interrupt Mask 0 (IMR_S0)

7.9.28 Secondary Interrupt Mask 1 (IMR_S1)

7.9.29 Secondary Interrupt Mask 2 (IMR_S2)

7.9.30 Secondary Interrupt Mask 3 (IMR_S3)

7.9.31 Secondary Interrupt Mask 4 (IMR_S4)

7.9.32 Secondary Interrupt Mask 5 (IMR_S5)

7.9.33 Primary Interrupt Status Read and Clear (ISR_P_RAC)

7.9.34 Secondary Interrupt Status 0 (ISR_S0_S)

7.9.35 Secondary Interrupt Status 1 (ISR_S1_S)

7.9.36 Secondary Interrupt Status 2 (ISR_S2_S)

7.9.37 Secondary Interrupt Status 3 (ISR_S3_S)

7.9.38 Secondary Interrupt Status 4 (ISR_S4_S)

7.9.39 Secondary Interrupt Status 5 (ISR_S5_S)

7.10 WQCU Registers

7.10.1 Tx Queue Descriptor (Q_TXDP)

7.10.2 QCU_STATUS_RING_START_ADDRESS Lower 32 bits of Address (Q_STATUS_RING_START)

7.10.3 QCU_STATUS_RING_END_ADDR Lower 32 Bits of Address (Q_STATUS_RING_END)

7.10.4 QCU_STATUS_RING_CURRENT Address (Q_STATUS_RING_ CURRENT)

7.10.5 Tx Queue Enable (Q_TXE)

7.10.6 Tx Queue Disable (Q_TXD)

7.10.7 CBR Configuration (Q_CBRCFG)

7.10.8 ReadyTime Configuration (Q_RDYTIMECFG)

7.10.9 OneShotArm Set Control (Q_ONESHOTARM_SC)

7.10.10 OneShotArm Clear Control (Q_ONESHOTARM_CC)

7.10.11 Misc. QCU Settings (Q_MISC)

7.10.12 Misc. QCU Status (Q_STS)

7.10.13 ReadyTimeShutdown Status (Q_RDYTIMESHDN)

7.10.14 Descriptor CRC Check (MAC_QCU_DESC_CRC_CHK)

7.11 WDCU Registers

7.11.1 QCU Mask (D_QCUMASK)

7.11.2 DCU-Global SIFS (D_GBL_IFS_SIFS)

7.11.3 DCU-Specific IFS Settings (D_LCL_IFS)

7.11.4 QCU Global IFS Slots (D_GBL_IFS_SLOT)

7.11.5 Retry Limits (D_RETRY_LIMIT)

7.11.6 QCU Global IFS EIFS (D_GBL_IFS_EIFS)

7.11.7 ChannelTime Settings (D_CHNTIME)

7.11.8 QCU Global IFS Miscellaneous (D_GBL_IFS_MISC)

7.11.9 Misc. DCU-Specific Settings (D_MISC)

7.11.10 DCU Sequence (D_SEQ)

7.11.11 DCU Pause (D_PAUSE)

7.11.12 DCU Transmission Slot Mask (D_TXSLOTMASK)

7.11.13 MAC Sleep Status (SLEEP_STATUS)

7.11.14 MAC LED Configuration (LED_CONFIG)

7.12 WMAC Glue Registers

7.12.1 Interface Reset Control (WMAC_GLUE_INTF_RESET_ CONTROL)

7.12.2 Synchronous Interrupt Enable (WMAC_GLUE_INTF_INTR_ SYNC_ENABLE)

7.12.3 Interface Timeout (WMAC_GLUE_INTF_TIMEOUT)

7.12.4 Synchronous Interrupt Cause (WMAC_GLUE_INTF_INTR_ SYNC_CAUSE)

7.12.5 Synchronous Interrupt Enable (WMAC_GLUE_INTF_INTR_ SYNC_ENABLE)

7.12.6 Asynchronous Interrupt Mask (WMAC_GLUE_INTF_INTR_ ASYNC_MASK)

7.12.7 Synchronous Interrupt Mask (WMAC_GLUE_INTF_INTR_ SYNC_MASK)

7.12.8 Asynchronous Interrupt Cause (WMAC_GLUE_INTF_INTR_ ASYNC_CAUSE)

7.12.9 Asynchronous Interrupt Enable (WMAC_GLUE_INTF_INTR_ ASYNC_ENABLE)

7.12.10 GPIO Output (WMAC_GLUE_INTF_GPIO_OUT)

7.12.11 GPIO Input (WMAC_GLUE_INTF_GPIO_IN)

7.12.12 GPIO SWCOM Enable Function (WMAC_GLUE_INTF_ SWCOM_GPIO_FUNC_ENABLE)

7.12.13 WMAC Glue GPIO Input Value (WMAC_GLUE_INTF_GPIO_ INPUT_VALUE)

7.12.14 Output Values from MAC to GPIO Pins (WMAC_GLUE_INTF_ GPIO_INPUT_STATE)

7.12.15 WMAC Glue Miscellaneous (WMAC_GLUE_INTF_MISC)

7.12.16 Synchronous AP Transmit (WMAC_GLUE_INTF_MAC_ TXAPSYNC)

7.12.17 Synchronous Initial Timer (WMAC_GLUE_INTF_MAC_ TXSYNC_INITIAL_SYNC_TMR)

7.12.18 Synchronous Priority Interrupt Cause (WMAC_GLUE_INTF_ INTR_PRIORITY_SYNC_CAUSE)

7.12.19 Synchronous Priority Interrupt Enable (WMAC_GLUE_INTF_ INTR_PRIORITY_SYNC_ENABLE)

7.12.20 Asynchronous Priority Interrupt Mask (WMAC_GLUE_INTF_ INTR_PRIORITY_ASYNC_MASK)

7.12.21 Synchronous Priority Interrupt Mask (WMAC_GLUE_INTF_ INTR_PRIORITY_SYNC_MASK)

7.12.22 Asynchronous Priority Interrupt Cause (WMAC_GLUE_INTF_ INTR_PRIORITY_ASYNC_CAUSE)

7.12.23 Asynchronous Priority Interrupt Enable (WMAC_GLUE_ INTF_INTR_PRIORITY_ASYNC_ENABLE)

7.12.24 AXI to MAC and MAC to AXI Byte Swap Enable (WMAC_ GLUE_INTF_AXI_BYTE_SWAP)

7.13 RTC Registers

7.13.1 Reset Control (RESET_CONTROL)

7.13.2 XTAL Control (XTAL_CONTROL)

7.13.3 Switching Regulator Control Bits 0 (REG_CONTROL0)

7.13.4 WLAN PLL Control Settings (WLAN_PLL_CONTROL)

7.13.5 PLL Settling Time (PLL_SETTLE)

7.13.6 Crystal Settling Time (XTAL_SETTLE)

7.13.7 Pin Clock Speed Control (CLOCK_OUT)

7.13.8 Reset Cause (RESET_CAUSE)

7.13.9 System Sleep Status (SYSTEM_SLEEP)

7.13.10 Keep Awake Timer (KEEP_AWAKE)

7.13.11 Derived RTC Clock (DERIVED_RTC_CLK)

7.13.12 PLL Control (PLL_CONTROL2)

7.13.13 RTC Sync Reset (RTC_SYNC_RESET)

7.13.14 RTC Sync Status (RTC_SYNC_STATUS)

7.13.15 RTC Derived (RTC_SYNC_DERIVED)

7.13.16 RTC Force Wake (RTC_SYNC_FORCE_WAKE)

7.13.17 RTC Interrupt Cause (RTC_SYNC_INTR_CAUSE)

7.13.18 RTC Interrupt Enable (RTC_SYNC_INTR_ENABLE)

7.13.19 RTC Interrupt Mask (RTC_SYNC_INTR_MASK)

7.14 WPCU Registers

7.14.1 STA Address Lower 32 Bits (WMAC_PCU_STA_ADDR_L32)

7.14.2 STA Address Upper 16 Bits (WMAC_PCU_STA_ADDR_U16)

7.14.3 BSSID Lower 32 Bits (WMAC_PCU_BSSID_L32)

7.14.4 BSSID Upper 16 Bits (WMAC_PCU_BSSID_U16)

7.14.5 Beacon RSSI Average (WMAC_PCU_BCN_RSSI_AVE)

7.14.6 ACK and CTS Timeout (WMAC_PCU_ACK_CTS_TIMEOUT)

7.14.7 Beacon RSSI Control (WMAC_PCU_BCN_RSSI_CTL)

7.14.8 Ms Counter and Rx/Tx Latency (WMAC_PCU_USEC_ LATENCY)

7.14.9 Reset TSF (WMAC_PCU_RESET_TSF)

7.14.10 Maximum CFP Duration (WMAC_PCU_MAX_CFP_DUR)

7.14.11 Rx Filter (WMAC_PCU_RX_FILTER)

7.14.12 Multicast Filter Mask Lower 32 Bits (WMAC_PCU_MCAST_ FILTER_L32)

7.14.13 Multicast Filter Mask Upper 32 Bits (WMAC_PCU_MCAST_ FILTER_U32)

7.14.14 Diagnostic Switches (WMAC_PCU_DIAG_SW)

7.14.15 TSF Lower 32 Bits (WMAC_PCU_TSF_L32)

7.14.16 TSF Upper 32 Bits (WMAC_PCU_TSF_U32)

7.14.17 AES Mute Mask 0 (WMAC_PCU_AES_MUTE_MASK_0)

7.14.18 AES Mute Mask 1 (WMAC_PCU_AES_MUTE_MASK_1)

7.14.19 Dynamic MIMO Power Save (DYM_MIMO_PWR_SAVE)

7.14.20 Last Receive Beacon TSF (MAC_PCU_LAST_BEACON_TSF)

7.14.21 Current NAV (WMAC_PCU_NAV)

7.14.22 Successful RTS Count (WMAC_PCU_RTS_SUCCESS_CNT)

7.14.23 Failed RTS Count (WMAC_PCU_RTS_FAIL_CNT)

7.14.24 FAIL ACK Count (WMAC_PCU_ACK_FAIL_CNT)

7.14.25 Failed FCS Count (WMAC_PCU_FCS_FAIL_CNT)

7.14.26 Beacon Count (WMAC_PCU_BEACON_CNT)

7.14.27 MAC PCU Sleep 1 (SLP1)

7.14.28 Sleep 2 (WMAC_PCU_SLP2)

7.14.29 Address 1 Mask Lower 32 Bits (WMAC_PCU_ADDR1_MASK_ L32)

7.14.30 Address 1 Mask Upper 16 Bits (WMAC_PCU_ADDR1_MASK_ U16)

7.14.31 Tx Power Control (WMAC_PCU_TPC)

7.14.32 Tx Frame Counter (WMAC_PCU_TX_FRAME_CNT)

7.14.33 Rx Frame Counter (WMAC_PCU_RX_FRAME_CNT)

7.14.34 Rx Clear Counter (WMAC_PCU_RX_CLEAR_CNT)

7.14.35 Cycle Counter (WMAC_PCU_CYCLE_CNT)

7.14.36 Quiet Time 1 (WMAC_PCU_QUIET_TIME_1)

7.14.37 Quiet Time 2 (WMAC_PCU_QUIET_TIME_2)

7.14.38 QoS NoACK (WMAC_PCU_QOS_NO_ACK)

7.14.39 PHY Error Mask (WMAC_PCU_PHY_ERROR_MASK)

7.14.40 Rx Buffer (WMAC_PCU_RXBUF)

7.14.41 QoS Control (WMAC_PCU_MIC_QOS_CONTROL)

7.14.42 Michael QoS Select (WMAC_PCU_MIC_QOS_SELECT)

7.14.43 Miscellaneous Mode (WMAC_PCU_MISC_MODE)

7.14.44 Filtered OFDM Counter (WMAC_PCU_FILTER_OFDM_CNT)

7.14.45 Filtered CCK Counter (WMAC_PCU_FILTER_CCK_CNT)

7.14.46 PHY Error Counter 1 (WMAC_PCU_PHY_ERR_CNT_1)

7.14.47 PHY Error Counter 1 Mask (WMAC_PCU_PHY_ERR_CNT_1_ MASK)

7.14.48 PHY Error Counter 2 (WMAC_PCU_PHY_ERR_CNT_2)

7.14.49 PHY Error Counter 2 Mask (WMAC_PCU_PHY_ERR_CNT_2_ MASK)

7.14.50 TSF Threshold (WMAC_PCU_TSF_THRESHOLD)

7.14.51 PHY Error EIFS Mask (WMAC_PCU_PHY_ERROR_EIFS_ MASK)

7.14.52 PHY Error Counter 3 (WMAC_PCU_PHY_ERR_CNT_3)

7.14.53 PHY Error Counter 3 Mask (WMAC_PCU_PHY_ERR_CNT_3_ MASK)

7.14.54 MAC PCU Generic Timers 2 (WMAC_PCU_GENERIC_ TIMERS2)

7.14.55 MAC PCU Generic Timers Mode 2 (WMAC_PCU_GENERIC_ TIMERS2_MODE)

7.14.56 SIFS, Tx Latency and ACK Shift (WMAC_PCU_TXSIFS)

7.14.57 TXOP for Non-QoS Frames (WMAC_PCU_TXOP_X)

7.14.58 TXOP for TID 0 to 3 (WMAC_PCU_TXOP_0_3)

7.14.59 TXOP for TID 4 to 7 (WMAC_PCU_TXOP_4_7)

7.14.60 TXOP for TID 8 to 11 (WMAC_PCU_TXOP_8_11)

7.14.61 TXOP for TID 0 to 3 (WMAC_PCU_TXOP_12_15)

7.14.62 Generic Timers (WMAC_PCU_GENERIC_TIMERS[0:15])

7.14.63 Generic Timers Mode (WMAC_PCU_GENERIC_TIMERS_ MODE)

7.14.64 32 KHz Sleep Mode (WMAC_PCU_SLP32_MODE)

7.14.65 32 KHz Sleep Wake (WMAC_PCU_SLP32_WAKE)

7.14.66 32 KHz Sleep Increment (WMAC_PCU_SLP32_INC)

7.14.67 Sleep MIB Sleep Count (WMAC_PCU_SLP_MIB1)

7.14.68 Sleep MIB Cycle Count (WMAC_PCU_SLP_MIB2)

7.14.69 Sleep MIB Control Status (WMAC_PCU_SLP_MIB3)

7.14.70 1 mS Clocks (1mS)

7.14.71 PHY Error Counter Continued (PHY_ERR_CNT_MASK_ CONT)

7.14.72 Global Mode (WMAC_PCU_20_40_MODE)

7.14.73 Difference RX_CLEAR Counter (WMAC_PCU_RX_CLEAR_ DIFF_CNT)

7.14.74 Self Generated Antenna Mask (SELF_GEN_ANTENNA_ MASK)

7.14.75 Control Registers for Block BA Control Fields (WMAC_PCU_ BA_BAR_CONTROL)

7.14.76 Legacy PLCP Spoof (WMAC_PCU_LEGACY_PLCP_SPOOF)

7.14.77 PHY Error Mask and EIFS Mask (WMAC_PCU_PHY_ERROR_ MASK_CONT)

7.14.78 Tx Timer (WMAC_PCU_TX_TIMER)

7.14.79 Alternate AES QoS Mute Mask (ALT_AES_MUTE_MASK)

7.14.80 TSF 2 Lower 32 (TSF2_L32)

7.14.81 TSF 2 Upper 32 (TSF2_U32)

7.14.82 BSSID 2 Upper 16 (BSSID2_U16)

7.14.83 TID Value Access Category (WMAC_PCU_TID_TO_AC)

7.14.84 High Priority Queue Control (WMAC_PCU_HP_QUEUE)

7.14.85 Hardware Beacon Processing 1 (HW_BCN_PROC1)

7.14.86 Hardware Beacon Processing 2 (HW_BCN_PROC2)

7.14.87 Key Cache (WMAC_PCU_KEY_CACHE[0:1023])

7.15 PMU Registers

7.15.1 PMU1

7.15.2 PMU2

7.16 PLL SRIF Registers

7.16.1 DPLL

7.16.2 DPLL2

7.16.3 DPLL3

7.17 PCIE Configuration Space Registers

7.17.1 Vendor ID

7.17.2 Device ID

7.17.3 Command

7.17.4 Status

7.17.5 Revision ID

7.17.6 Class Code

7.17.7 Class Line Size

7.17.8 Master Latency Timer

7.17.9 Header Type

7.17.10 Base Address 0 (BAR0)

7.17.11 BAR0 Mask

7.17.12 Bus Number

7.17.13 Secondary Status

7.17.14 Memory Base

7.17.15 Memory Limit

7.17.16 Prefetchable Memory Base

7.17.17 Prefetchable Memory Limit

7.17.18 Capability Pointer

7.17.19 Interrupt Line

7.17.20 Interrupt Pin

7.17.21 Bridge Control

7.18 PCIE RC PHY Registers

7.18.1 PLL Division (DPLL)

7.18.2 PLL Division 2 (DPLL2)

7.18.3 PLL Division 3 (DPLL3)

7.19 PCIE RC0 PHY Registers

7.19.1 PCIE PHY 1 (PCIE_PHY_REG_1)

7.19.2 PCIE PHY 2 (PCIE_PHY_REG_2)

7.19.3 PCIE PHY 3 (PCIE_PHY_REG_3)

7.20 GMAC0/GMAC1 Registers

7.20.1 MAC Configuration 1

7.20.2 MAC Configuration 2

7.20.3 IPG/IFG

7.20.4 Half-Duplex

7.20.5 Maximum Frame Length

7.20.6 MII Configuration

7.20.7 MII Command

7.20.8 MII Address

7.20.9 MII Control

7.20.10 MII Status

7.20.11 MII Indicators

7.20.12 Interface Control

7.20.13 Interface Status

7.20.14 STA Address 1

7.20.15 STA Address 2

7.20.16 ETH_FIFO RAM Configuration 0

7.20.17 ETH Configuration 1

7.20.18 ETH Configuration 2

7.20.19 ETH Configuration 3

7.20.20 ETH Configuration 4

7.20.21 ETH Configuration 5

7.20.22 Tx/Rx 64 Byte Frame Counter (TR64)

7.20.23 Tx/Rx 65-127 Byte Frame Counter (TR127)

7.20.24 Tx/Rx 128-255 Byte Frame Counter (TR255)

7.20.25 Tx/Rx 256-511 Byte Frame Counter (TR511)

7.20.26 Tx/Rx 512-1023 Byte Frame Counter (TR1K)

7.20.27 Tx/Rx 1024-1518 Byte Frame Counter (TRMAX)

7.20.28 Tx/Rx 1519-1522 Byte VLAN Frame Counter (TRMGV)

7.20.29 Receive Byte Counter (RXBT)

7.20.30 Receive Packet Counter (RPKT)

7.20.31 Receive FCS Error Counter (RFCS)

7.20.32 Receive Multicast Packet Counter (RMCA)

7.20.33 Receive Broadcast Packet Counter (RBCA)

7.20.34 Receive Control Frame Packet Counter (RXCF)

7.20.35 Receive Pause Frame Packet Counter (RXPF)

7.20.36 Receive Unknown OPCode Packet Counter (RXUO)

7.20.37 Receive Alignment Error Counter (RALN)

7.20.38 Receive Frame Length Error Counter (RFLR)

7.20.39 Receive Code Error Counter (RCDE)

7.20.40 Receive Carrier Sense Error Counter (RCSE)

7.20.41 Receive Undersize Packet Counter (RUND)

7.20.42 Receive Oversize Packet Counter (ROVR)

7.20.43 Receive Fragments Counter (RFRG)

7.20.44 Receive Jabber Counter (RJBR)

7.20.45 Receive Dropped Packet Counter (RDRP)

7.20.46 Transmit Byte Counter (TXBT)

7.20.47 Transmit Packet Counter (TPKT)

7.20.48 Transmit Multicast Packet Counter (TMCA)

7.20.49 Transmit Broadcast Packet Counter (TBCA)

7.20.50 Transmit Pause Control Frame Counter (TXPF)

7.20.51 Transmit Deferral Packet Counter (TDFR)

7.20.52 Transmit Excessive Deferral Packet Counter (TEDF)

7.20.53 Transmit Single Collision Packet Counter (TSCL)

7.20.54 Transmit Multiple Collision Packet (TMCL)

7.20.55 Transmit Late Collision Packet Counter (TLCL)

7.20.56 Transmit Excessive Collision Packet Counter (TXCL)

7.20.57 Transmit Total Collision Counter (TNCL)

7.20.58 Transmit Pause Frames Honored Counter (TPFH)

7.20.59 Transmit Drop Frame Counter (TDRP)

7.20.60 Transmit Jabber Frame Counter (TJBR)

7.20.61 Transmit FCS Error Counter (TFCS)

7.20.62 Transmit Control Frame Counter (TXCF)

7.20.63 Transmit Oversize Frame Counter (TOVR)

7.20.64 Transmit Undersize Frame Counter (TUND)

7.20.65 Transmit Fragment Counter (TFRG)

7.20.66 Carry Register 1 (CAR1)

7.20.67 Carry Register 2 (CAR2)

7.20.68 Carry Mask Register 1 (CAM1)

7.20.69 Carry Mask Register 2 (CAM2)

7.20.70 DMA Transfer Control for Queue 0 (DMATXCNTRL_Q0)

7.20.71 Descriptor Address for Queue 0 Tx (DMATXDESCR_Q0)

7.20.72 Transmit Status (DMATXSTATUS)

7.20.73 Receive Control (DMARXCTRL)

7.20.74 Pointer to Receive Descriptor (DMARXDESCR)

7.20.75 Receive Status (DMARXSTATUS)

7.20.76 Interrupt Mask (DMAINTRMASK)

7.20.77 Interrupts (DMAINTERRUPT)

7.20.78 Ethernet TX Burst (ETH_ARB_TX_BURST)

7.20.79 Current Tx and Rx FIFO Depth (ETH_XFIFO_DEPTH)

7.20.80 Ethernet Transmit FIFO Throughput (ETH_TXFIFO_TH)

7.20.81 Ethernet Receive FIFO Threshold (ETH_RXFIFO_TH)

7.20.82 Ethernet Free Timer (ETH_FREE_TIMER)

7.20.83 DMA Transfer Control for Queue 1 (DMATXCNTRL_Q1)

7.20.84 Descriptor Address for Queue 1 Tx (DMATXDESCR_Q1)

7.20.85 DMA Transfer Control for Queue 2 (DMATXCNTRL_Q2)

7.20.86 Descriptor Address for Queue 2 Tx (DMATXDESCR_Q2)

7.20.87 DMA Transfer Control for Queue 3 (DMATXCNTRL_Q3)

7.20.88 Descriptor Address for Queue 3 Tx (DMATXDESCR_Q3)

7.20.89 DMA Transfer Arbitration Configuration (DMATXARBCFG)

7.20.90 Tx Status and Packet Count for Queues 1 to 3 (DMATXSTATUS_123)

7.20.91 Local MAC Address Dword0 (LCL_MAC_ADDR_DW0)

7.20.92 Local MAC Address Dword1 (LCL_MAC_ADDR_DW1)

7.20.93 Next Hop Router MAC Address Dword0 (NXT_HOP_DST_ ADDR_DW0)

7.20.94 Next Hop Router MAC Destination Address Dword1 (NXT_ HOP_DST_ADDR_DW1)

7.20.95 Local Global IP Address 0 (GLOBAL_IP_ADDR0)

7.20.96 Local Global IP Address 1 (GLOBAL_IP_ADDR1)

7.20.97 Local Global IP Address 2 (GLOBAL_IP_ADDR2)

7.20.98 Local Global IP Address 3 (GLOBAL_IP_ADDR3)

7.21 Serial Flash SPI Controller Registers

7.21.1 SPI Controller GPIO Mode Select (FUNCTION_SELECT_ADDR)

7.21.2 SPI Address Control (SPI_CONTROL_ADDR)

7.21.3 SPI I/O Address Control (SPI_IO_CONTROL_ADDR)

7.21.4 SPI Read Data Address (SPI_READ_DATA_ADDR)

7.21.5 SPI Data to Shift Out (SPI_SHIFT_DATAOUT_ADDR)

7.21.6 SPI Content to Shift Out or In (SPI_SHIFT_CNT_ADDR)

7.21.7 SPI Data to Shift In (SPI_SHIFT_DATAIN_ADDR)

7.22 Ethernet Switch Registers

7.23 Global Control Registers

7.23.1 Mask Control

7.23.2 Operational Mode 0

7.23.3 Operational Mode 1

7.23.4 Global Interrupt

7.23.5 Global Interrupt Mask

7.23.6 Global MAC Address

7.23.7 Loop Check Result

7.23.8 Flood Mask

7.23.9 Global Control

7.23.10 Flow Control 0

7.23.11 Flow Control 1

7.23.12 QM Control

7.23.13 VLAN Table Function 0

7.23.14 VLAN Table Function 1

7.23.15 Address Table Function 0

7.23.16 Address Table Function 1

7.23.17 Address Table Function 2

7.23.18 Address Table Control

7.23.19 IP Priority Mapping 2

7.23.20 Tag Priority Mapping

7.23.21 Service Tag

7.23.22 CPU Port

7.23.23 LPI

7.23.24 MIB Function 0

7.23.25 MDIO Control

7.23.26 LED Control

7.24 Port Control Registers

7.24.1 Port Status

7.24.2 Port Control

7.24.3 Port-Based VLAN

7.24.4 Port-Based VLAN 2

7.24.5 Rate Limit

7.24.6 Priority Control

7.24.7 Storm Control

7.24.8 Queue Control

7.24.9 Rate Limit 1

7.24.10 Rate Limit 2

7.24.11 Rate Limit 3

7.24.12 Robin

7.24.13 LPI Control

7.25 PHY Control Registers

7.25.1 Control

7.25.2 Status

7.25.3 PHY Identifier

7.25.4 PHY Identifier 2

7.25.5 Auto-Negotiation Advertisement

7.25.6 Link Partner Ability

7.25.7 Auto-negotiation Expansion

7.25.8 MMD Access Control

7.25.9 MMD Access Address Data

7.25.10 Function Control

7.25.11 PHY Specific Status

7.25.12 Interrupt Enable

7.25.13 Interrupt Status

7.25.14 Smart Speed

7.25.15 Receive Error Counter

7.25.16 Virtual Cable Tester Control

7.25.17 Virtual Cable Tester Status

7.25.18 Debug Port (Address Offset)

7.25.19 Debug Port 2 (RW Port)

7.26 Debug Port Registers

7.26.1 Analog Test Control

7.26.2 System Mode Control

7.26.3 Hibernate Control

7.26.4 100 Base-Tx Test Mode Select

7.26.5 10 Base-Tx Test Mode Select

7.26.6 Power Saving Control

7.26.7 PHY Control

7.26.8 CABLE_LTH_DETECT_DEBUG1

7.27 MMD3 PCS Registers

7.27.1 PCS Control 1

7.27.2 PCS Status 1

7.27.3 EEE Capability

7.27.4 EEE Wake Error Counter

7.28 MMD7 Auto-Negotiation Registers

7.28.1 Auto-Negotiation

7.28.2 Auto-Negotiation Status

7.28.3 EEE Advertisement

7.28.4 EEE LP Advertisement

7.28.5 EEE Ability Auto-Negotiation Result

8 Ethernet Subsystem

8.1 GMAC0 and GMAC1

8.2 Ethernet Switch

8.3 Five-Port Ethernet Switch

8.3.1 Overview

8.3.2 Basic Switch Operation

8.3.3 Media Access Controllers (MAC)

8.3.4 ACL

8.3.5 Register Access

8.3.6 LED Control

8.3.7 VLANs

8.3.8 IEEE Port Security

8.3.9 Mirroring

8.3.10 Broadcast/Multicast/Unknown Unicast

8.3.11 IGMP/MLD Snooping

8.3.12 Spanning Tree

8.3.13 MIB/Statistics Counters

8.3.14 Qualcomm Atheros Header Configuration

8.3.15 IEEE 802.3 Reserved Group Addresses Filtering Control

8.3.16 PPPoE Header Removal

8.4 Ethernet Core Reset

9 Electrical Characteristics

9.1 Absolute Maximum Ratings

9.2 Recommended Operating Conditions

9.3 Radio Characteristics

9.3.1 Radio Receiver Characteristics

9.3.2 Transmitter Characteristics

9.3.3 Synthesizer Characteristics

9.4 Power Consumption

9.5 AC Specifications

9.5.1 SPI Timing

9.5.2 DDR Timing

9.5.3 DDR Timing Input

9.5.4 Reset Timing

10 Part Reliability

10.1 Reliability Qualifications Summary

10.2 Qualification Sample Description

11 Package Dimensions

12 Ordering Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc