PCIe Solutions on Xilinx FPGAs 初学者指南

初学者指南

初学者指南

初学者指南

V1.0

hanson@comtech.com.cn

PCIe on Xilinx 初学者指南 ............................................................................................................... 1

前言........................................................................................................................................... 1

步步为营 ................................................................................................................................... 3

一,PCIe 层次结构 .......................................................................................................... 3

事物协议 ........................................................................................................................... 3

头标 ................................................................................................................................... 4

BAR 空间 ........................................................................................................................... 6

中断 ................................................................................................................................... 7

二,器件选型 ................................................................................................................... 9

三,仿真环境搭建 ........................................................................................................... 9

四,调试 ......................................................................................................................... 14

五,驱动编写 ................................................................................................................. 15

六,总结 ......................................................................................................................... 16

进阶......................................................................................................................................... 22

DMA 模式 ....................................................................................................................... 22

DDR 缓冲......................................................................................................................... 23

经验、教训总结 ............................................................................................................. 24

前言前言前言前言

北京奥运会那年接手了一个项目,需要将远程的 80MBps 的数据量传输到服务器,同时

不能占用太多的处理器时间,因为服务器上同时运行着一套大型数据库软件。最后排除了

USB 方案、以太网方案,选用 Xilinx 的 PCIe 解决方案。经过漫长的摸索、学习过程,最后项

目做成功的做完了,各种指标参数也都达到了。再后来做 FAE,见识了更多的 PCIe 应用,也

有幸结识了更多的开发工程师。有的对 PCIe 的理解非常深入了,无论在性能和功能上都达

到相当的深度;有的也和我原来一样,刚开始学习理解 PCIe 的应用,看书、看文档,有时

候迷茫的找不到如何下手。对于前一种高手,这篇应用笔记可以略过了;对于后一种正在做

产品、项目的工程师,希望能对您有所帮助。

什么时候需要用到

什么时候需要用到 PCIe????

什么时候需要用到

什么时候需要用到

首先需要定位的是什么时候需要用到 PCIe 的问题。(PCIe 是什么这里就不做介绍了,不

�

然冗长的像写论文了。)

翻开电脑(台式机),主板上可以清晰的看到常用的接口,能和外面连接的插槽主要有:

USB、Ethernet、PCIe、PCI、SATA/PATA、Audio、VGA/DVI/HDMI,UART/并口。其中 Audio、

VGA/DVI/HDMI 制作专用数据输出,UART/并口的速率摆在那里,不适合高速数据传输,剩

下的接口最大吞吐率

最大吞吐率如下:

最大吞吐率

最大吞吐率

接口

USB

Ethernet

PCIe

PCI

最大速率

USB2.0 480Mbps, USB3.0 5Gbps(USB2.0 速率的 10 倍)

1Gbps

X8 Gen1 双向各 16Gbps,X8 Gen2 双向各 32Gbps

2.112Gbps@66Mhz*32 位

SATA/PATA SATA II 3.0Gbps, SATA III 6.0Gbps

排除协议开销,OS 开销,平常使用中 USB 能达到的速度 USB2.0 一般在 30-40MB;Ethenet

如果用硬件实现较低层次的协议在 70-80MBps;PCI 有 64 位的,但是普通 PC 或服务器一般

是 32 位的,见过效率发挥的较好的能达到 120MB,但是 PCI 是共享总线的,如果总线有多

个设备开销,这个速度就难保证了;SATA/PATA 在 PC 中一般用于存储,用于自定义设备的

很少见。因此,如果数据量超过 100M,那 PCIe 最合适了。

速度是一方面考虑的原因,能否快速实现(有无成熟的设计方案),并且产品稳定、可

靠是另外一个需要考虑的原因。

USB 有 Cypress 的 USB2.0 芯片,然后将总线接到 FPGA 上。网上有很多 USB 芯片的程

序、驱动程序,甚至有公开的 GUI 程序,可以方便的完成 FPGA 到 PC 的通讯。

Ethernet 以太网也是比较成熟的接口。FPGA 外接 PHY 就可以和 PC 通讯了。以太网的

协议非常复杂,FPGA 如果内部运行 CPU 加以太网协议栈,那可以支持高层的以太网协议,

但是这样速度就打折扣了,并且 FPGA 的开发难度也增加很多。如果只实现 MAC 层数据收

发,难度相对简单一些。

开发难度

开发难度:

开发难度开发难度

PCI PCI 卡的方案也比较成熟了,既可以用 PLX 公司的桥片+FPGA 的方案,也可以直接

用 FPGA 接 PCI IP 核的方式。PCI 经过长时间的积累,已经有相当多的上层和底层设计、调试

软件,如果是购买的桥片,还有配套的开发工具简化设计流程。

SATA/PATA 通过 SATA/PATA 接口和 PC 进行数据通讯的方案比较少见,有 Intelliprop 一

些列的 SATA Device IP Core,同时提供一些底层的软件支持。

PCIe PCIe 的方案种类延续了 PCI 的多样性。1,完全采用 FPGA 方案。Xilinx 早在 10 年

前就把 PCIe 作为重要的支持方向,在高、中、低端 FPGA 内都集成有免费的 PCIe 硬核,同

时提供了数种源码(包括驱动、软件)开放的参考设计,还有丰富的文档。无论是学习、还

是产品设计,都能在众多的资料中找到相关的信息,减少设计、调试的时间(例如,Xilinx 的

PCIe 用户手册,xapp1052 DMA 参考设计,PIO 参考设计)。2,采用桥片方案,例如 PLX,IDT

等芯片,然后将转换的局部总线接入 FPGA。

研发产品需从多方面考虑,成本、可靠性、兼容性、性能等。单片 FPGA 方案越来越多

的应用在各种产品的研发中。如果确定需要使用 FPGA 的 PCIe 方案,而此时对这一流程比较

迷茫,那希望这篇指南能对您有所帮助。

�

步步为营

步步为营

步步为营

步步为营

PCIe 相关知识

引用 Wiki http://zh.wikipedia.org/zh-cn/PCI-E,简单介绍 PCIe 的基本特性,其他不理解的

没关系,要么等一个流程下来自然而然明白了,要么…就不需要知道(Xilinx 封装好了)。

Wiki 上列出各版本 PCIe 的链路速度,通道数。说白了,链路速度高,单位时间内传输

的有效数据多;通道数多,同时传递的数据多。此外,还有很给力的一点就是兼容,板卡和

主板自适应的匹配到最大的链路速度和通道数。也就是说,如果这个板卡只支持 PCIe1.1 x8,

放在支持 PCIe2.0 x16 的槽上,那两端会是应在 PCIe1.1 x8 的速率上;如果有一天板卡升级了,

到 PCIe2.0 x8,那主板会适应成 PCIe2.0 x8 上,并且 PC 上的驱动和软件都不用变化。

接下来有点晦涩了,但是建议耐着性子看完吧。

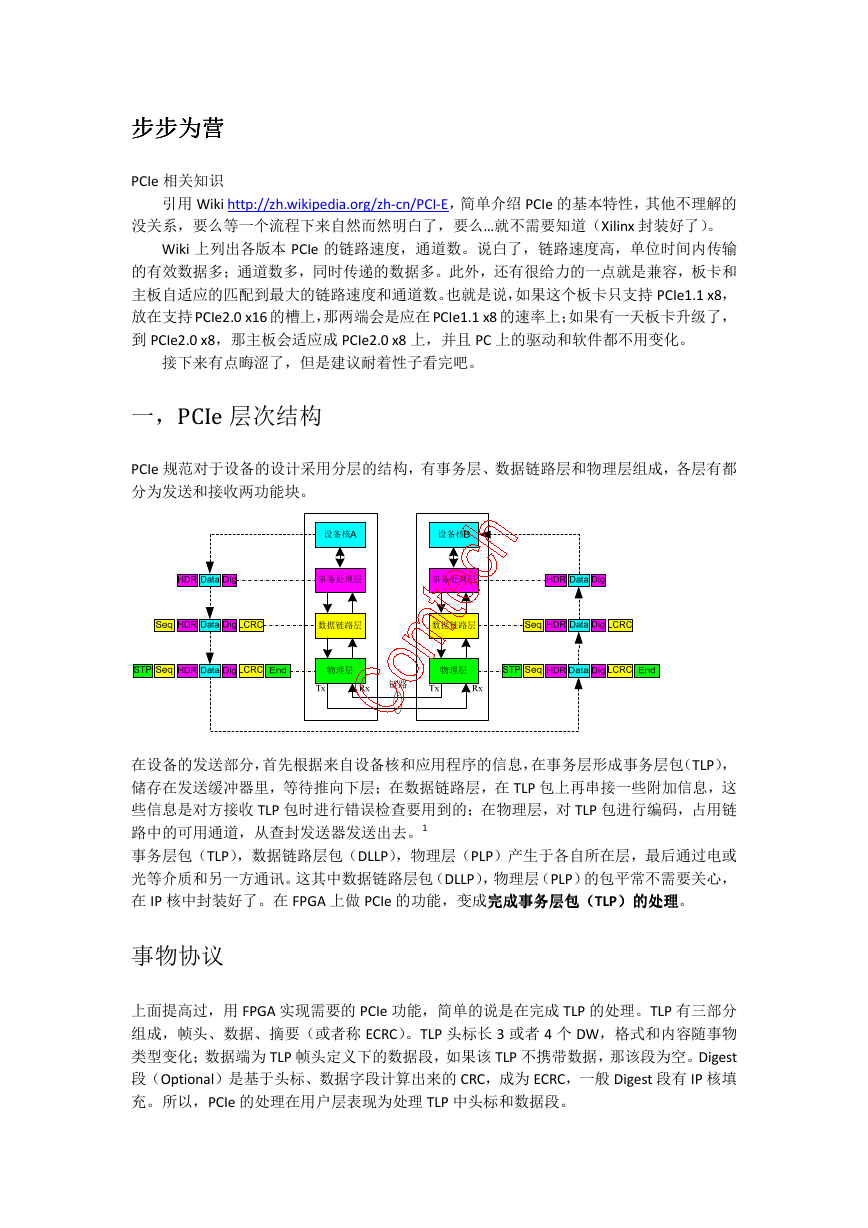

一,PCIe 层次结构

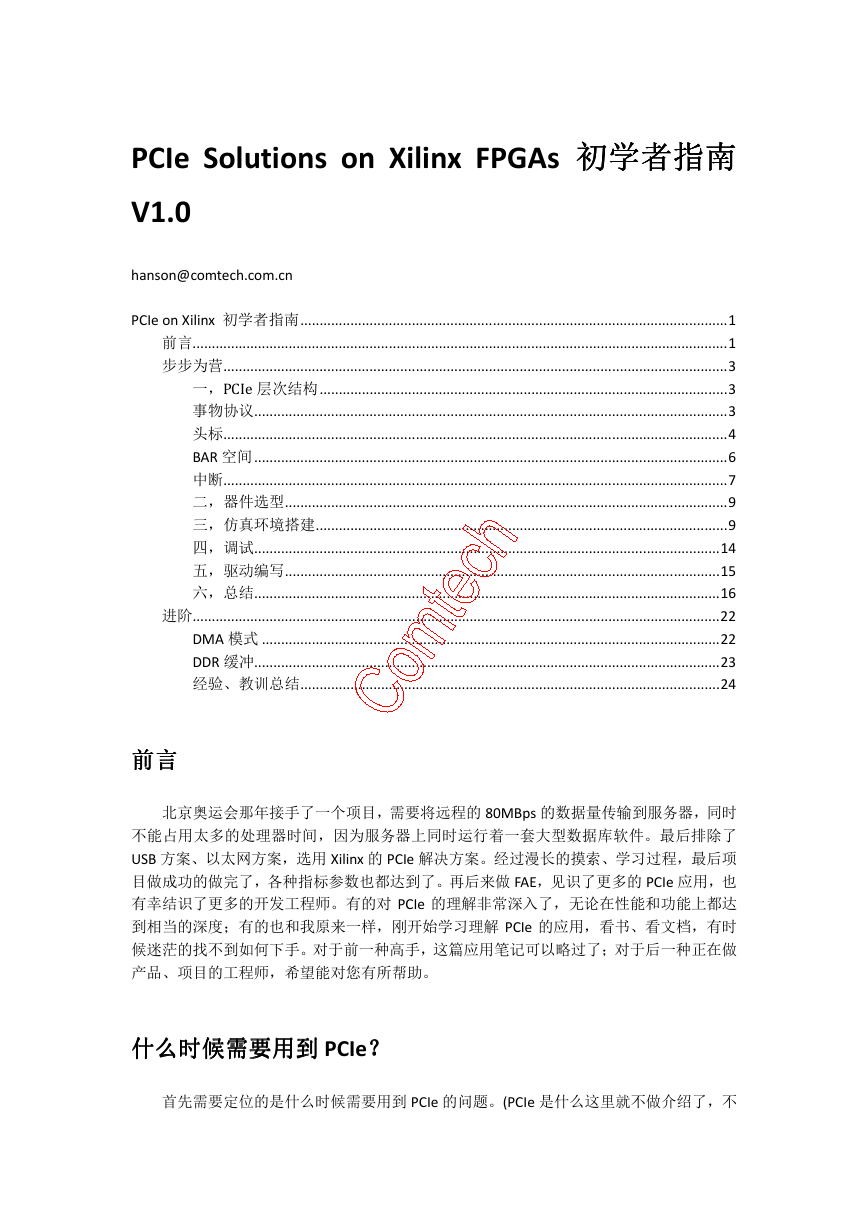

PCIe 规范对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都

分为发送和接收两功能块。

在设备的发送部分,首先根据来自设备核和应用程序的信息,在事务层形成事务层包(TLP),

储存在发送缓冲器里,等待推向下层;在数据链路层,在 TLP 包上再串接一些附加信息,这

些信息是对方接收 TLP 包时进行错误检查要用到的;在物理层,对 TLP 包进行编码,占用链

路中的可用通道,从查封发送器发送出去。1

事务层包(TLP),数据链路层包(DLLP),物理层(PLP)产生于各自所在层,最后通过电或

光等介质和另一方通讯。这其中数据链路层包(DLLP),物理层(PLP)的包平常不需要关心,

在 IP 核中封装好了。在 FPGA 上做 PCIe 的功能,变成完成事务层包

完成事务层包((((TLP))))的处理的处理的处理的处理。

完成事务层包

完成事务层包

事物协议

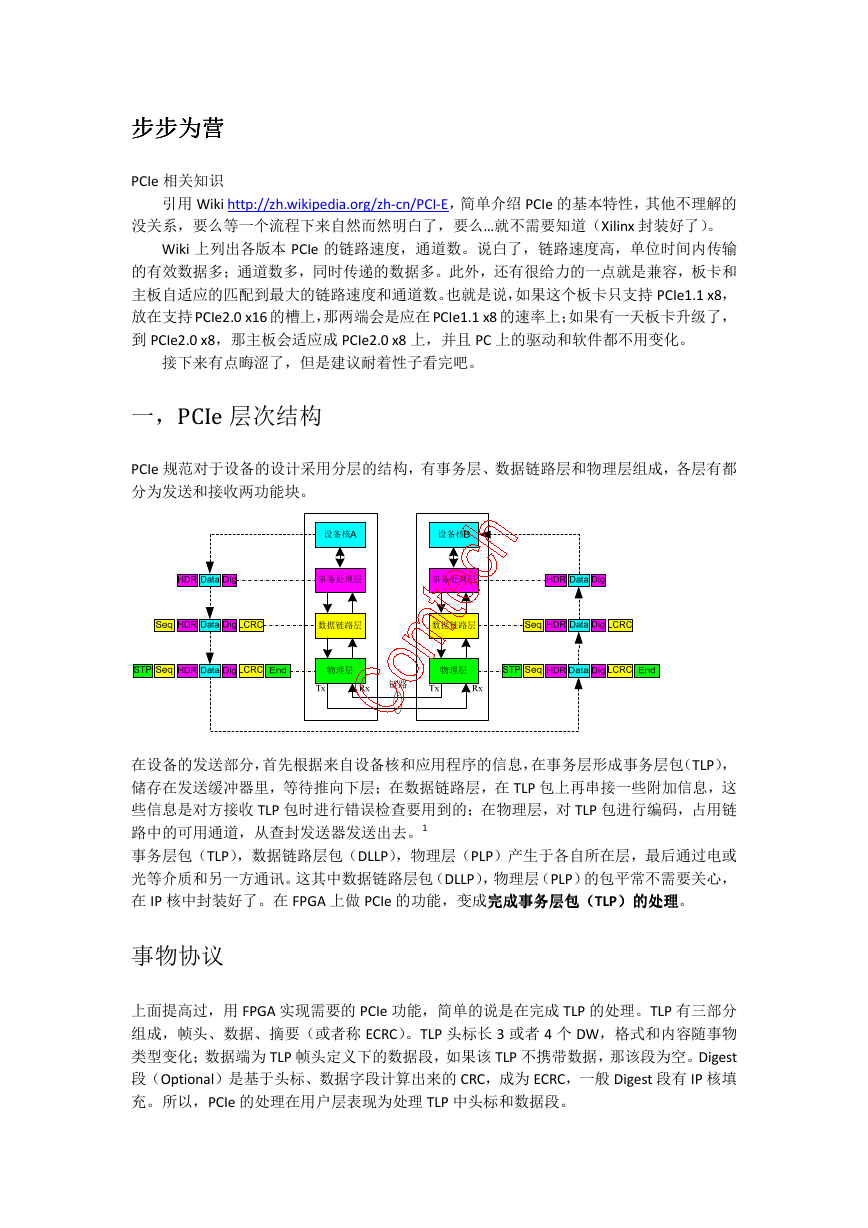

上面提高过,用 FPGA 实现需要的 PCIe 功能,简单的说是在完成 TLP 的处理。TLP 有三部分

组成,帧头、数据、摘要(或者称 ECRC)。TLP 头标长 3 或者 4 个 DW,格式和内容随事物

类型变化;数据端为 TLP 帧头定义下的数据段,如果该 TLP 不携带数据,那该段为空。Digest

段(Optional)是基于头标、数据字段计算出来的 CRC,成为 ECRC,一般 Digest 段有 IP 核填

充。所以,PCIe 的处理在用户层表现为处理 TLP 中头标和数据段。

�

图 1 TLP 结构

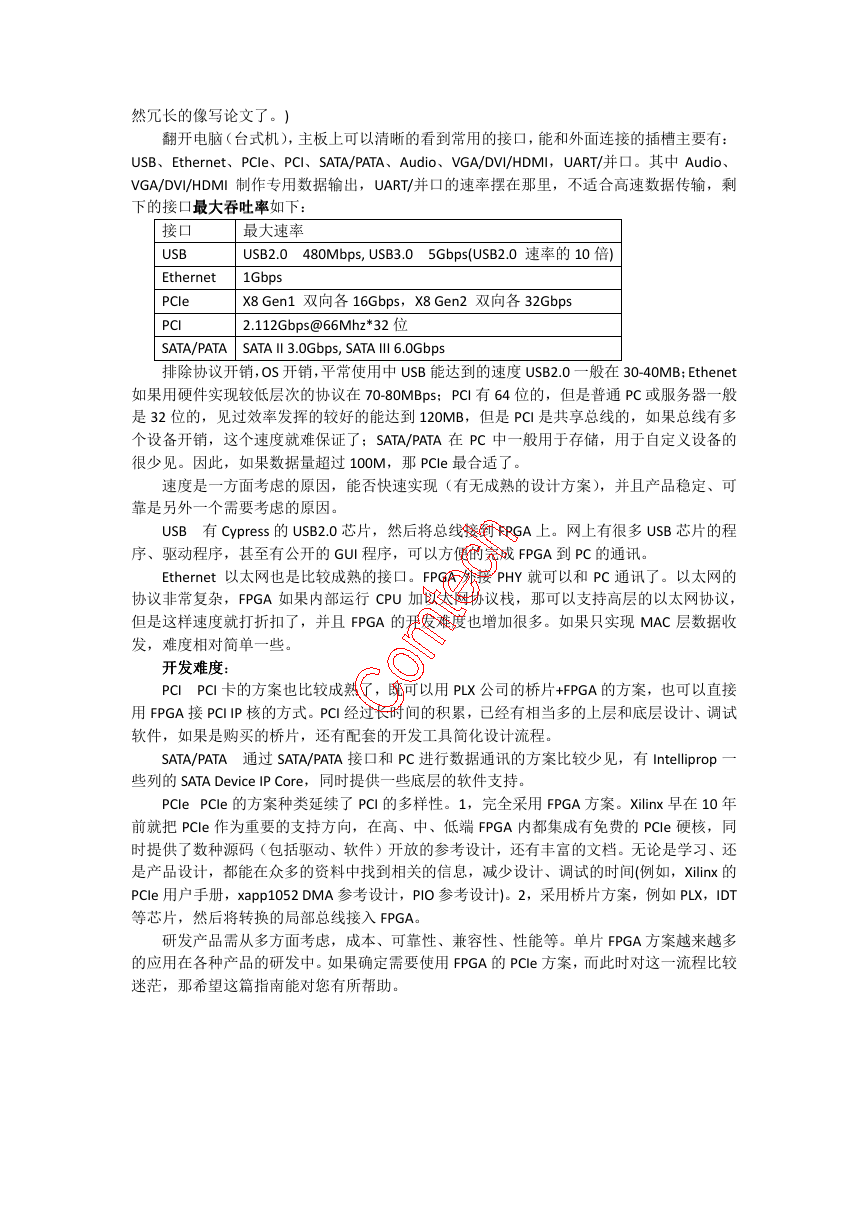

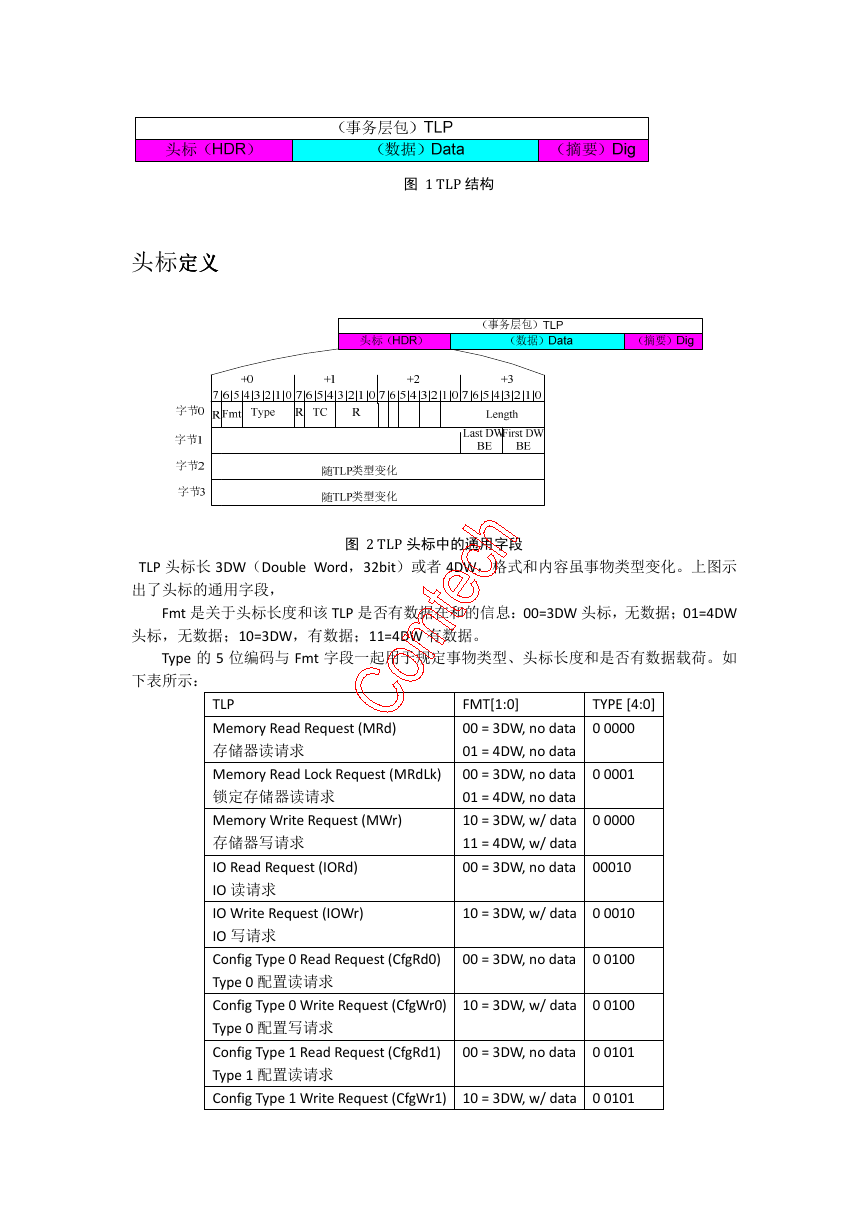

头标定义定义定义定义

图 2 TLP 头标中的通用字段

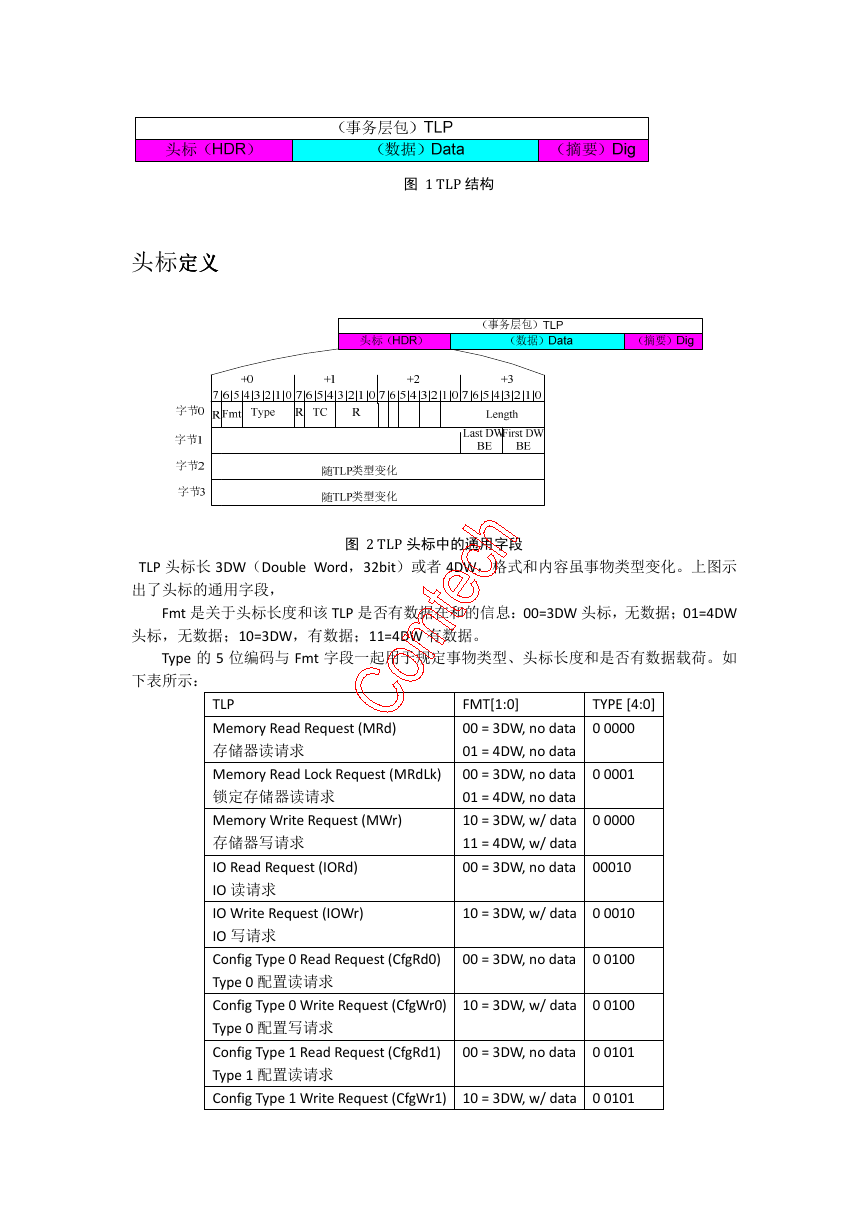

TLP 头标长 3DW(Double Word,32bit)或者 4DW,格式和内容虽事物类型变化。上图示

出了头标的通用字段,

Fmt 是关于头标长度和该 TLP 是否有数据在和的信息:00=3DW 头标,无数据;01=4DW

头标,无数据;10=3DW,有数据;11=4DW 有数据。

Type 的 5 位编码与 Fmt 字段一起用于规定事物类型、头标长度和是否有数据载荷。如

下表所示:

TLP

Memory Read Request (MRd)

存储器读请求

FMT[1:0]

TYPE [4:0]

00 = 3DW, no data

0 0000

01 = 4DW, no data

Memory Read Lock Request (MRdLk)

锁定存储器读请求

00 = 3DW, no data

0 0001

01 = 4DW, no data

Memory Write Request (MWr)

存储器写请求

IO Read Request (IORd)

IO 读请求

IO Write Request (IOWr)

IO 写请求

10 = 3DW, w/ data

0 0000

11 = 4DW, w/ data

00 = 3DW, no data 00010

10 = 3DW, w/ data 0 0010

Config Type 0 Read Request (CfgRd0)

Type 0 配置读请求

Config Type 0 Write Request (CfgWr0)

Type 0 配置写请求

Config Type 1 Read Request (CfgRd1)

Type 1 配置读请求

00 = 3DW, no data 0 0100

10 = 3DW, w/ data 0 0100

00 = 3DW, no data 0 0101

Config Type 1 Write Request (CfgWr1) 10 = 3DW, w/ data 0 0101

�

Type10 配置写请求

Message Request (Msg)

消息请求

01 = 4DW, no data 1 0 rrr*

Message Request W/Data (MsgD)

带数据的消息请求

11 = 4DW, w/ data 1 0rrr*

Completion (Cpl)

完成

Completion W/Data (CplD)

带数据的完成

Completion-Locked (CplLk)

锁定完成

Completion W/Data (CplDLk)

带数据的锁定完成

00 = 3DW, no data 0 1010

10 = 3DW, w/ data 0 1010

00 = 3DW, no data 0 1011

10 = 3DW, w/ data 0 1011

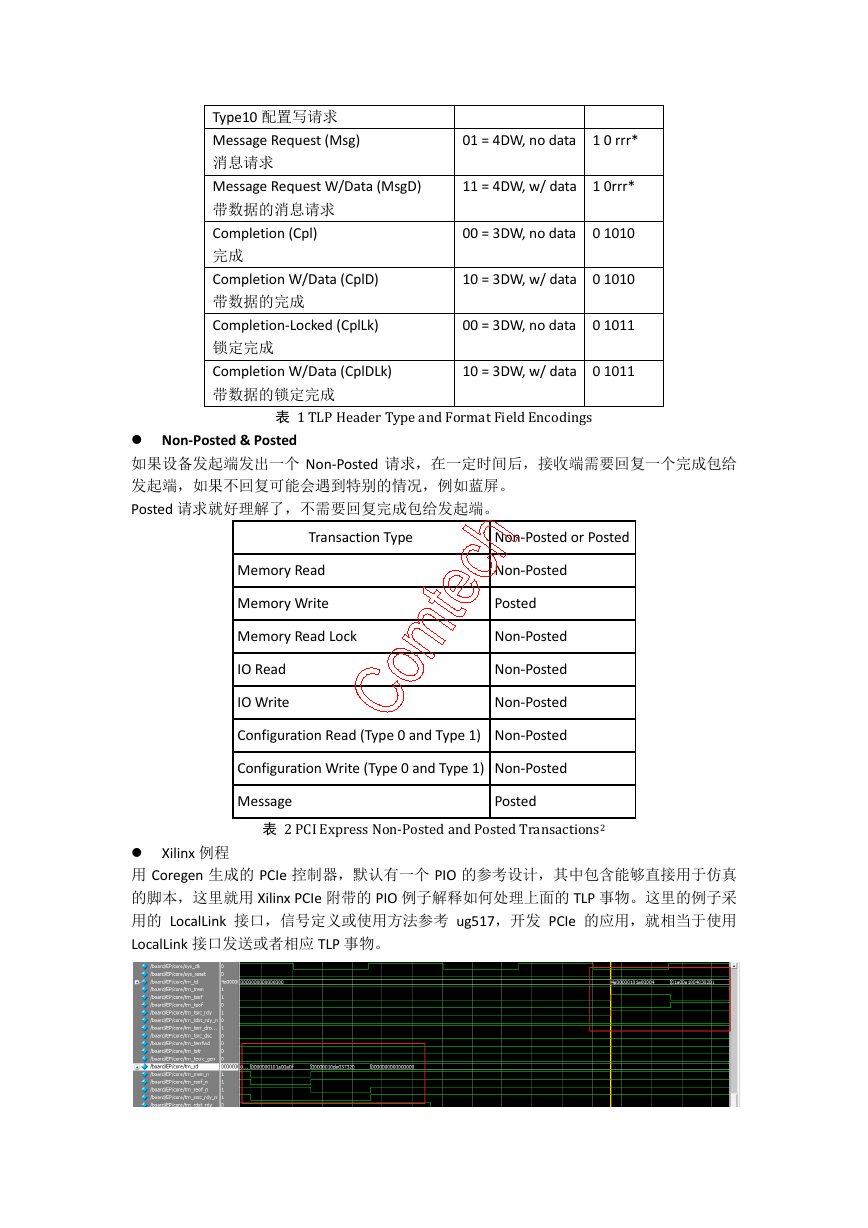

表 1 TLP Header Type and Format Field Encodings

� Non-Posted & Posted

如果设备发起端发出一个 Non-Posted 请求,在一定时间后,接收端需要回复一个完成包给

发起端,如果不回复可能会遇到特别的情况,例如蓝屏。

Posted 请求就好理解了,不需要回复完成包给发起端。

Transaction Type

Non-Posted or Posted

Memory Read

Memory Write

Memory Read Lock

IO Read

IO Write

Non-Posted

Posted

Non-Posted

Non-Posted

Non-Posted

Configuration Read (Type 0 and Type 1) Non-Posted

Configuration Write (Type 0 and Type 1) Non-Posted

Message

Posted

表 2 PCI Express Non-Posted and Posted Transactions2

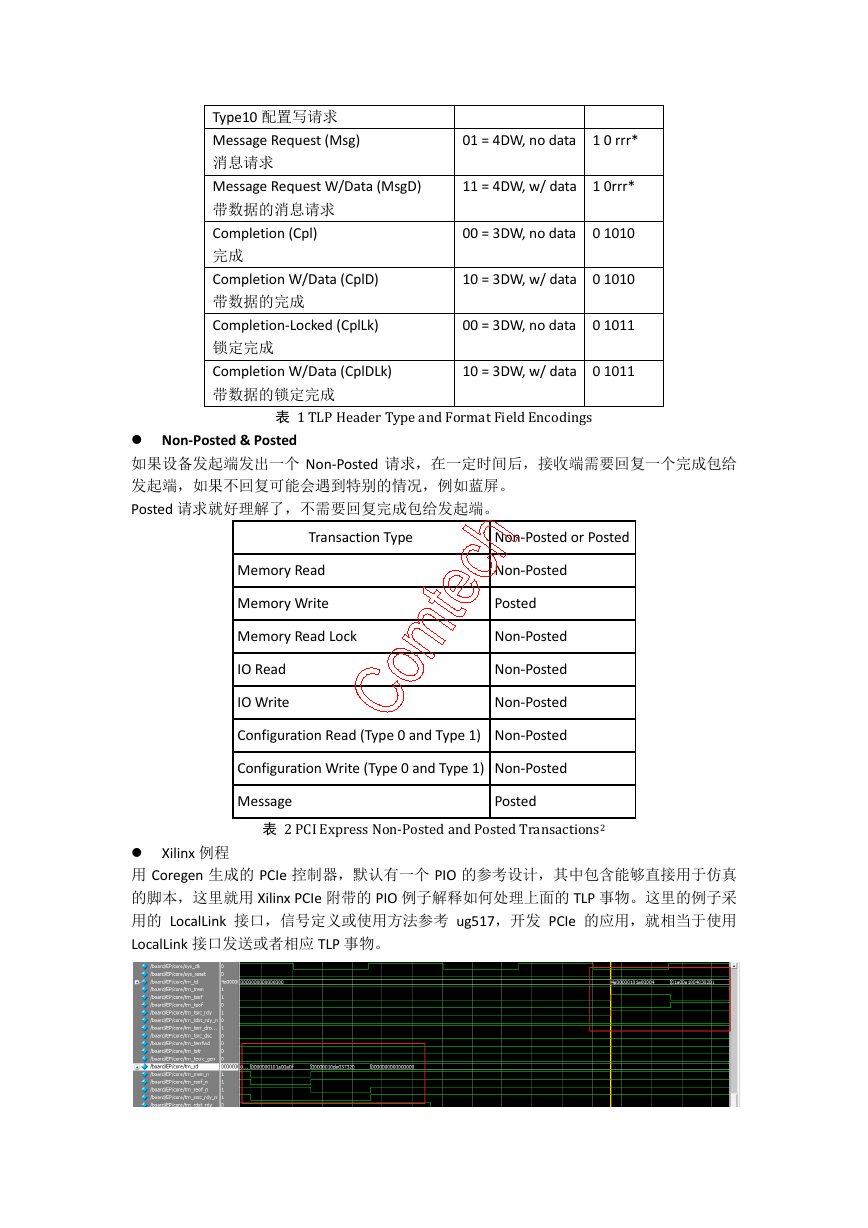

� Xilinx 例程

用 Coregen 生成的 PCIe 控制器,默认有一个 PIO 的参考设计,其中包含能够直接用于仿真

的脚本,这里就用 Xilinx PCIe 附带的 PIO 例子解释如何处理上面的 TLP 事物。这里的例子采

用的 LocalLink 接口,信号定义或使用方法参考 ug517,开发 PCIe 的应用,就相当于使用

LocalLink 接口发送或者相应 TLP 事物。

�

在左下框,sof 代表帧的开始,eof 代表帧的结束,收到的帧数据为 0x0000_0001_01a0_0a0f,

0x0000_0010_de03_7320 , rem_n 为高代表后面最后一个 DW 是无效的,因此,收到的完

整的帧为 0x0000_0001_01a0_0a0f_0000_0010 。按照上述包格式分析,Fmt 是 2’b00,Type

是 5’b0000,接收的是 Non-Posted 3DW 存储器读请求包(MRd)(具体请求的是什么下文

再讲)。既然是 Non-Posted 的请求包,就需要有完成包作为回复。

在右上框,发送的数据帧数据为 0x4a00_0001_01a0_0004,0x01a0_0a10_0403_0201。Fmt

是 2’b10,Type 是 5’b01010,判断为 3DW 带数据的完成包,0x4a00_0001_01a0_0004_

01a0_0a10 是头标,0x0403_0201 是所带的数据。

PCIe 设计很大一部分工作就是判断 RX 收到什么 TLPs,通过 TX 发送什么样的 TLPs。有时候

发现异常,分析这些最基本的 TLP 包结构是非常有效的诊断方式。

BAR 空间空间空间空间

上面讲到 PCIe 通讯是靠发送 TLP 包,如果再进一步参考了 PCIe 更详细的书籍就能发现读写

包里都有地址信息。如果板卡向 PC 发送 TLP 包,例如 MWr 包,那很好理解,地址信息就是

PC 的物理地址(注意这里说的是物理地址);如果是 MRd 包,那 PC 收到后回复一个完成包,

板卡从完成包分析出数据即得到 MRd 读取地址的数据。那 PC 如何读写板卡的数据呢?

简单的解释,PC 启动是,BIOS 探测所有的外设。对 PCIe(PCI)设备来说,BIOS 检测到板卡

有多少个 BAR 空间,每个空间有多大,然后对应为这些 BAR 空间分配地址。对 PC 设备来说,

它能“看”到 PCIe 板卡的空间只有 BAR 空间,也就只能访问这些 BAR 空间。也就是说,板

卡可以发送合法的 PCIe TLP 包,并得到 PC 端的相应;但是 PC 端访问板卡被局限在 BAR 空

间。例如,下图是 Realtek 网卡的 BAR 空间分配图:该网卡有 3 个 BAR 空间,BAR0、BAR2、

BAR4,BAR0 空间配置为 I/O 空间,BAR2 和 BAR4 配置为 Memory 空间。

图 3 Realtek 网卡的 BAR 空间

图 4 Realtek 网卡 Memory 空间大小

�

图 5 Realtek 网卡 IO 空间大小

从上两幅图来看,BAR2 空间大小为 0x1000,在 PC 的其实地址为 0xFDEF_F000;BAR4 空间

大小为 0x4000,起始地址为 0xFDEF_8000;BAR0 空间为 0x100,其实地址为 0x0000_DE00。

大小在接口芯片中已经定义好了,而起始地址在不同的 PC 上分配的地址是不同的,但是偏

移地址相同,访问板卡的效果就是相同的。例如,假设需要访问该板卡 BAR2 空间的地址 0x80,

在 PC 上访问 0xFDEF_8080 就对应读写 BAR2 空间的 0x80 地址了。

在 FPGA 中,BAR 空间的设置根据用户逻辑设计的需求来定义大小。假设我们需要和上面网

卡相同的设置,PCIe 核定制的时候就可以按照下列的选项:

图 6 PCIe 核 BAR 空间设置

中断中断中断中断

做过嵌入式和工程师应该对中断有较深的理解,中断处的调试相对于 BAR 空间也复杂

一些。

PCIe 可以发出两种中断,一种是虚拟 INTx 信号线的,一种是 MSI 的。

过去 PCI 板卡发送中断通过拉低 INTx(INTA#,INTB#,INTC#,INTD#)来申请中断,PC

检测到 INTx 的中断,就跳转执行 INTx 对应的中断驱动程序,驱动程序里需要操作板卡

将 INTx 拉回去,不然就发生嵌套中断了。用下面两个时序图来解释 INTx 中断,收到的

数据包内容为 0x3400_0000_0100_0020, 0x0000_0000_0000_0000,根据事物协议的章节

分析该包,Fmt 为 2’b01,Type 为 5’b10100,是消息请求,Message Code 为 8’b0010_0000,

是中断(INTx)消息。根据下图可以看到 received_assert_inta 为 1,收到 INTA#中断了。

�

图 7 INTA# Assert

收 到 INTA# 中 断 后 的 处 理 程 序 需 要 将 INTA# 拉 高 , 如 下 图 , 收 到 的 数 据 包 内 容 为

0x3400_0000_0100_0024, 0x0000_0000_0000_0000,Fmt 为 2’b01,Type 为 5’b10100,是消

息 请 求 , Message Code 为 8’b0010_0100 , 是 中 断 ( INTx ) 撤 销 消 息 。 下 图 可 以 看 到

received_deassert_inta 为 1,收到 INTA#中断撤销消息。

图 8 INTA# Deassert

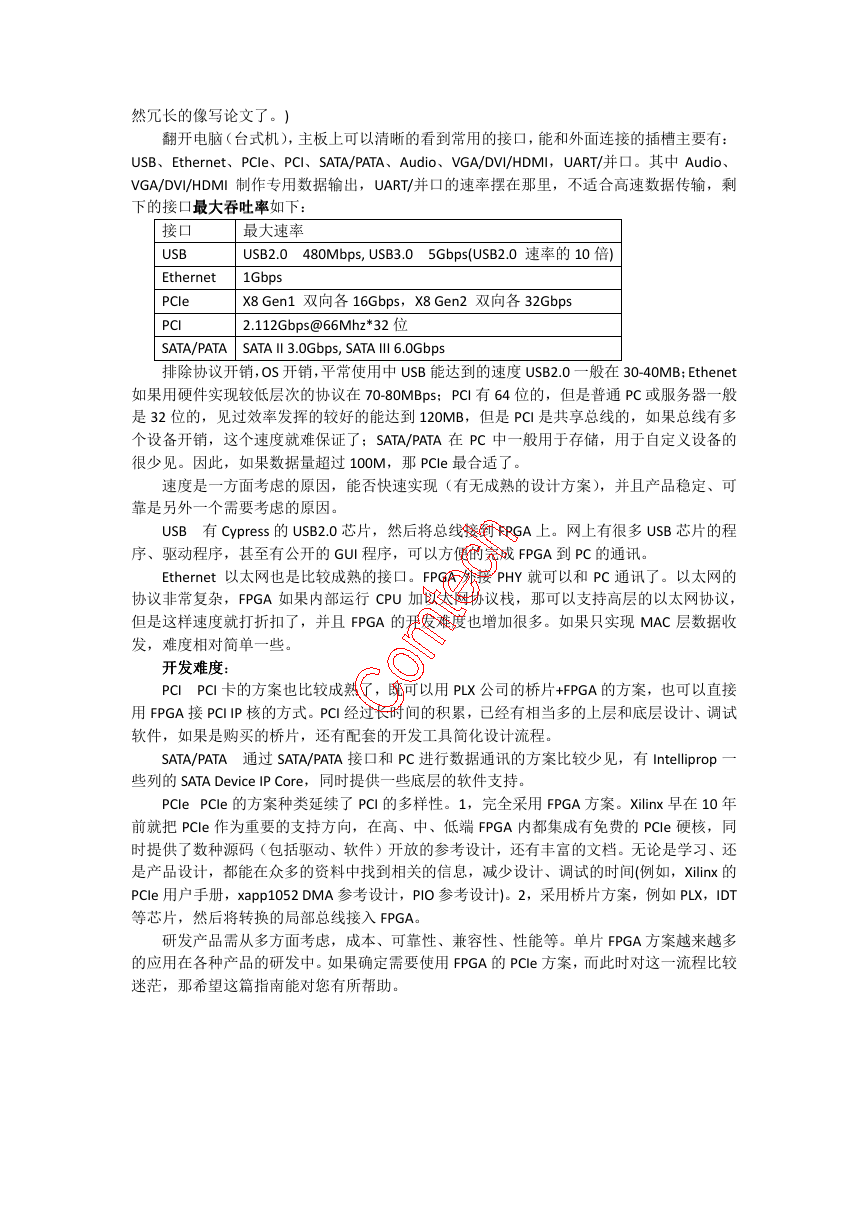

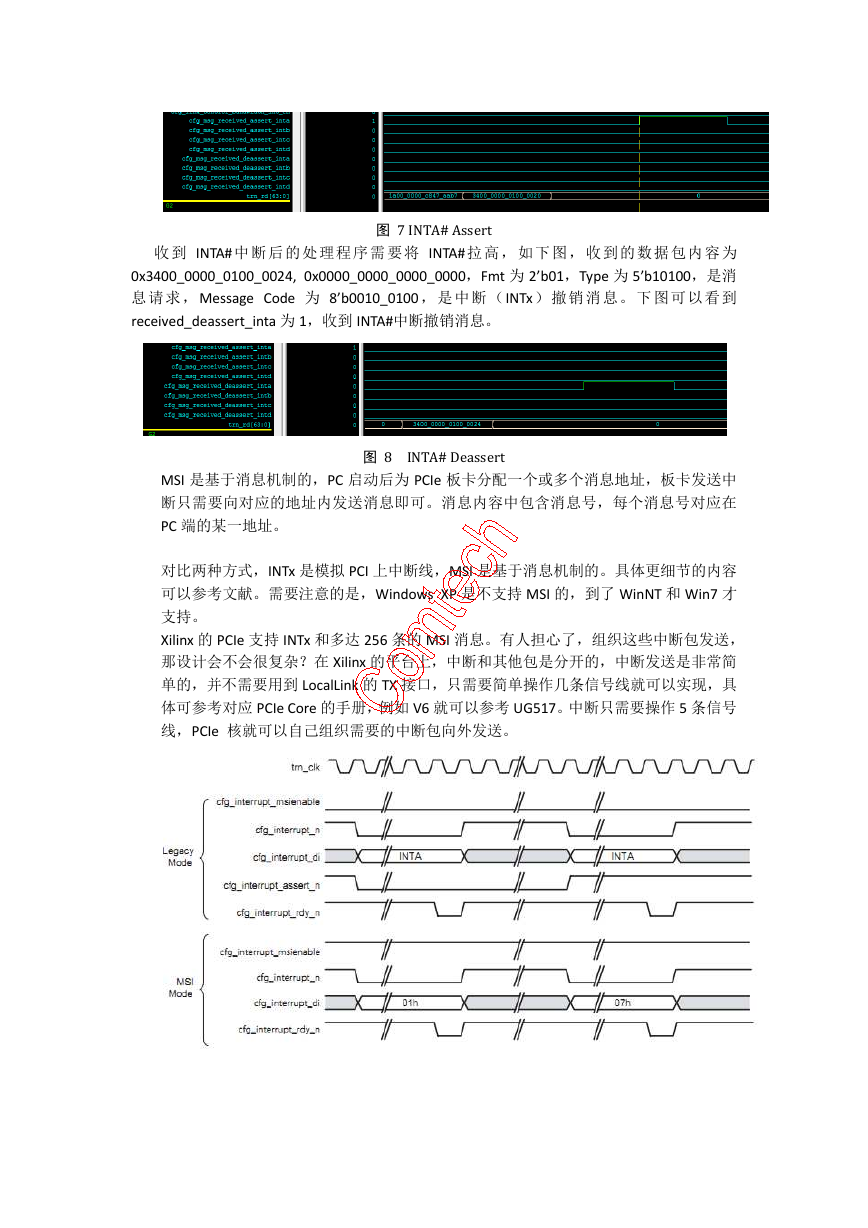

MSI 是基于消息机制的,PC 启动后为 PCIe 板卡分配一个或多个消息地址,板卡发送中

断只需要向对应的地址内发送消息即可。消息内容中包含消息号,每个消息号对应在

PC 端的某一地址。

对比两种方式,INTx 是模拟 PCI 上中断线,MSI 是基于消息机制的。具体更细节的内容

可以参考文献。需要注意的是,Windows XP 是不支持 MSI 的,到了 WinNT 和 Win7 才

支持。

Xilinx 的 PCIe 支持 INTx 和多达 256 条的 MSI 消息。有人担心了,组织这些中断包发送,

那设计会不会很复杂?在 Xilinx 的平台上,中断和其他包是分开的,中断发送是非常简

单的,并不需要用到 LocalLink 的 TX 接口,只需要简单操作几条信号线就可以实现,具

体可参考对应 PCIe Core 的手册,例如 V6 就可以参考 UG517。中断只需要操作 5 条信号

线,PCIe 核就可以自己组织需要的中断包向外发送。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc