BCM54616S Data Sheet

Revision History

Table of Contents

List of Figures

List of Tables

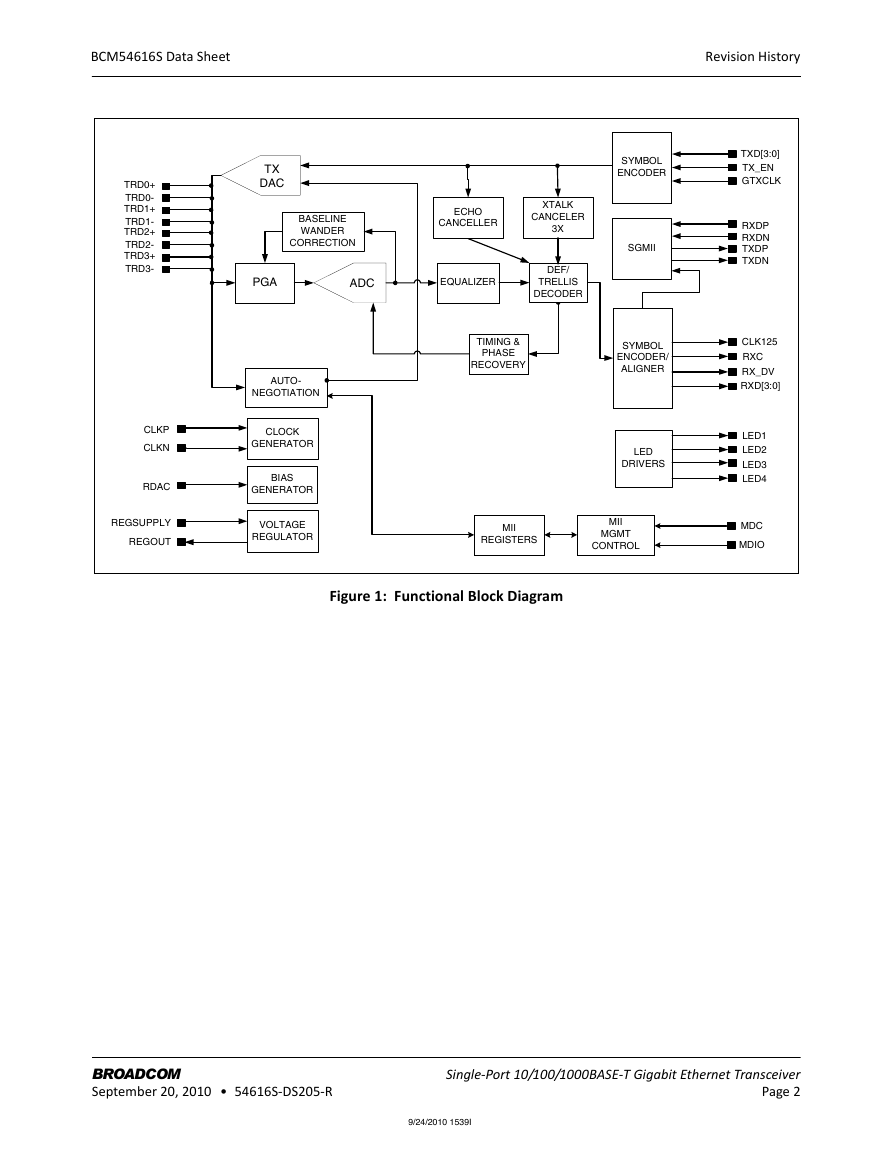

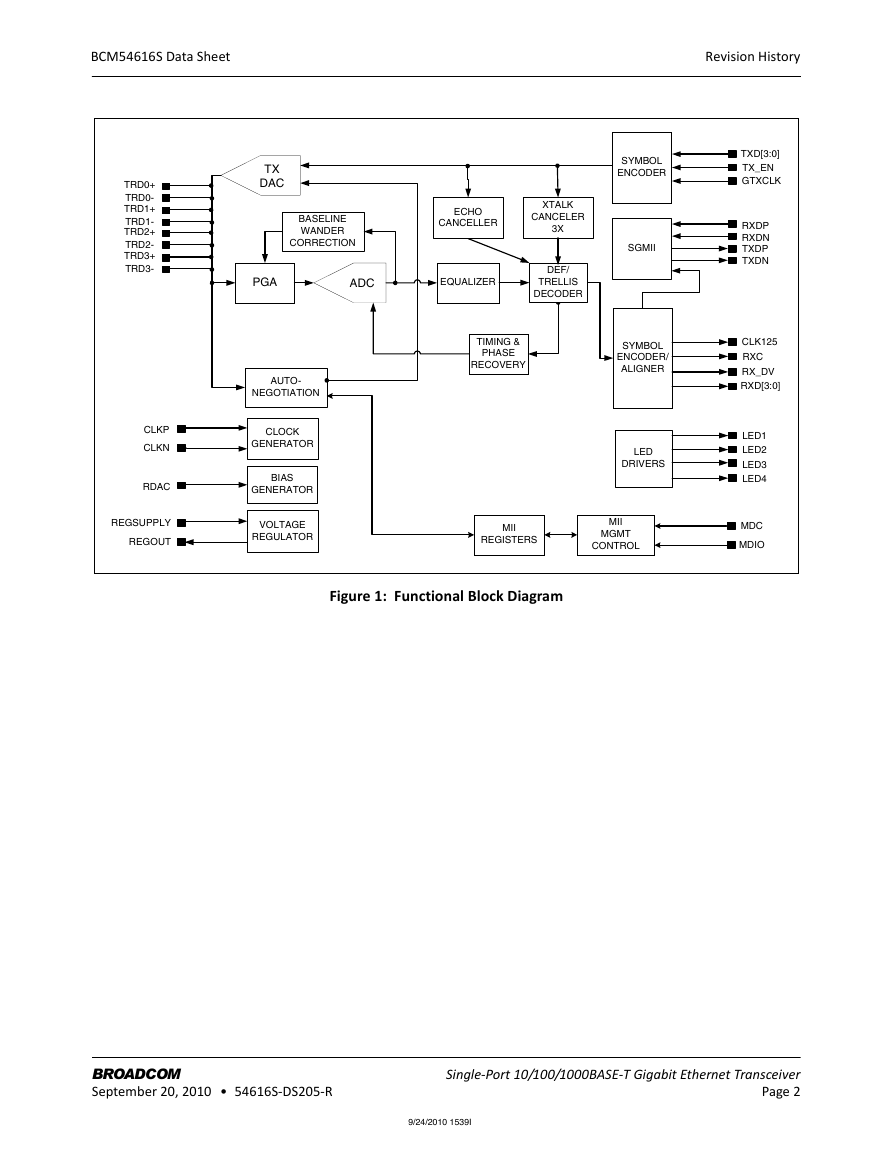

Section 1: Functional Description

Overview

Modes of Operation

Reduced Gigabit Media Independent Interface

Serial GMII Interface

SerDes Interface (Complies with IEEE 802.3™, Clauses 36 and 37)

Management Interface

Encoder

Decoder

Carrier Sense

Link Monitor

Digital Adaptive Equalizer

Echo Canceler

Crosstalk Canceler

Analog-to-Digital Converter

Clock Recovery/Generator

Baseline Wander Correction

Multimode TX Digital-to-Analog Converter

Stream Cipher

Wire Map and Pair Skew Correction

Automatic MDI Crossover

10/100BASE-T Forced Mode Auto-MDIX

Auto-Negotiation

Copper Mode

SGMII Mode

Ethernet@Wirespeed

Software Disable

Changing the Number of Failed Link Attempts Before Ethernet@Wirespeed Downgrade

Monitoring Ethernet@Wirespeed

Synchronous Ethernet

Energy Detect

Internal Voltage Regulator

Power-Down Modes

Jumbo Packets

Broadcom Serial Control Interface

BSC Master Mode

BSC Slave Mode

Section 2: Hardware Signal Descriptions

Section 3: Pinout

Section 4: Operational Description

Reset

PHY Address

Isolate Mode

Standby Power-Down Mode

Auto Power-Down Mode

CLK125 Clock Output

Ultra-Low Power-Down Mode

Reset Requirements

Internal Loopback Mode

Lineside (Remote) Loopback Mode

External Loopback Mode

Full-Duplex Operation

Master/Slave Configuration

Next Page Exchange

RGMII Interface

SGMII Interface

Control Information Exchange Between Links

Internal Voltage Regulator

Dual-Input Configuration/LED Output Function

General Purpose LED Programmability

Interrupt Function

LED Modes

Multicolor LED

Energy Link LED

Additional LED Modes

Section 5: Register Summary

MII Management Interface Register Programming

Preamble (PRE)

Start of Frame (ST)

Operation Code (OP)

PHY Address (PHYAD)

Register Address (REGAD)

Turnaround (TA)

Data

Register Map

Register Notations

1000BASE-T/100BASE-TX/10BASE-T Register Descriptions

Register 00h: 1000BASE-T/100BASE-TX/10BASE-T MII Control

Reset

Internal Loopback

Speed Selection (LSB)

Auto-Negotiation Enable

Power-Down

Isolate

Restart Auto-Negotiation

Duplex Mode

Speed Selection (MSB)

Collision Test

Register 01h: 1000BASE-T/100BASE-TX/10BASE-T MII Status

100BASE-T4 Capable

100BASE-TX Full-Duplex Capable

100BASE-TX Half-Duplex Capable

10BASE-T Full-Duplex Capable

10BASE-T Half-Duplex Capable

100BASE-T2 Full-Duplex Capable

100BASE-T2 Half-Duplex Capable

Extended Status

Management Frames Preamble Suppression

Auto-Negotiation Complete

Remote Fault

Auto-Negotiation Ability

Link Status

Jabber Detect

Extended Capability

Register 02h and 03h: 1000BASE-T/100BASE-TX/10BASE-T PHY Identifier

Register 04h: 1000BASE-T/100BASE-TX/10BASE-T Auto-Negotiation Advertisement

Next Page

Remote Fault

Reserved Technology

Asymmetric Pause

Pause Capable

100BASE-T4 Capable

100BASE-TX Full-Duplex Capable

100BASE-TX Half-Duplex Capable

10BASE-T Full-Duplex Capable

10BASE-T Half-Duplex Capable

Selector Field

Register 05h: 1000BASE-T/100BASE-TX/10BASE-T Auto-Negotiation Link Partner Ability

Next Page

Acknowledge

Remote Fault

Reserved Technology

Asymmetric Pause

Pause Capable

100BASE-T4 Capable

100BASE-TX Full-Duplex Capable

100BASE-TX Half-Duplex Capable

10BASE-T Full-Duplex Capable

10BASE-T Half-Duplex Capable

Protocol Selector Field

Register 06h: 1000BASE-T/100BASE-TX/10BASE-T Auto-Negotiation Expansion

NEXT_PAGE_RECEIVE_LOCATION_ABLE

NEXT_PAGE_RECEIVE_LOCATION

Parallel Detection Fault

Link Partner Next Page Ability

Next Page Capable

Page Received

Link Partner Auto-Negotiation Ability

Register 07h: 1000BASE-T/100BASE-TX/10BASE-T Next Page Transmit

Next Page

Message Page

Acknowledge2

Toggle

Message/Unformatted Code Field

Register 08h: 1000BASE-T/100BASE-TX/10BASE-T Link Partner Received Next Page

Next Page

Acknowledge

Message Page

Acknowledge2

Toggle

Message Code Field

Register 09h: 1000BASE-T Control

Test Mode

Master/Slave Configuration Enable

Master/Slave Configuration Value

Repeater/DTE

Advertise 1000BASE-T Full-Duplex Capability

Advertise 1000BASE-T Half-Duplex Capability

Register 0Ah: 1000BASE-T Status

Master/Slave Configuration Fault

Master/Slave Configuration Resolution

Local Receiver Status

Remote Receiver Status

1000BASE-T Full-Duplex Capability

1000BASE-T Half-Duplex Capability

Idle Error Count

Register 0Fh: 1000BASE-T/100BASE-TX/10BASE-T IEEE Extended Status

1000BASE-X Full-Duplex Capable

1000BASE-X Half-Duplex Capable

1000BASE-T Full-Duplex Capable

1000BASE-T Half-Duplex Capable

Auxiliary Register DescriptionsRegister 10h: 1000BASE-T/ 100BASE-TX/10BASE-T PHY Extended Control

MAC/PHY Interface Mode

Disable Automatic MDI Crossover

Transmit Disable

Interrupt Disable

Force Interrupt

Bypass 4B/5B Encoder/Decoder (100BASE-TX)

Bypass Scrambler/Descrambler (100BASE-TX)

Bypass MLT3 Encoder/Decoder (100BASE-TX)

Bypass Receive Symbol Alignment (100BASE-TX)

Reset Scrambler (100BASE-TX)

Enable LED Traffic Mode

Force LEDs On

Force LEDs Off

1000BASE-T PCS Transmit FIFO Elasticity (Copper Mode)

Register 11h: 1000BASE-T/100BASE-TX/10BASE-T PHY Extended Status

Auto-Negotiation Base Page Selector Field Mismatch

MDI Crossover State

Interrupt Status

Remote Receiver Status

Local Receiver Status

Locked

Link Status

CRC Error Detected

Carrier Extension Error Detected

Bad SSD Detected (False Carrier)

Bad ESD Detected (Premature End)

Receive Error Detected

Transmit Error Detected

Lock Error Detected

MLT3 Code Error Detected

Register 12h: 1000BASE-T/100BASE-TX/10BASE-T Receive Error Counter

Receive Error Counter

Register 13h: 1000BASE-T/100BASE-TX/10BASE-T False Carrier Sense Counter

False Carrier Sense Counter

Register 14h: 1000BASE-T/100BASE-TX/10BASE-T Receiver NOT_OK Counter

Local Receiver NOT_OK Counter

Remote Receiver NOT_OK Counter

Register 17h: Expansion Register Access

Expansion Register Select

Expansion Register Address

Register 18h: Shadow Access

Register 18h (Shadow 000): Auxiliary Control Register

External Loopback

Extended Packet Length

Edge Rate Control (1000BASE-T)

Transmit Mode

Disable Partial Response Filter

Edge Rate Control (100BASE-TX)

Shadow Register Select

Register 18h (Shadow 001): 10BASE-T

Manchester Code Error

EOF Error

Polarity Error

Block RX_DV Extension (IPG)

10BASE-T TXC Invert Mode

Jabber Disable

1000BASE-T Signal Detect Threshold

10BASE-T Signal Detect Threshold

10BASE-T Echo Mode

SQE Enable Mode

10BASE-T No Dribble

Shadow Register Select

Register 18h (Shadow 010): Power/MII Control

Super Isolate

Shadow Register Select

Register 18h (Shadow 100): Miscellaneous Test Register

Lineside [Remote] Loopback Enable

Lineside [Remote] Loopback Tristate

Swap RX MDIX

10BASE-T Half-Out

Shadow Register Select

Register 18h (Shadow 111): Miscellaneous Control

Write Enable (Bits 11:3)

Shadow Register Read Selector

Packet Counter Mode

Bypass Wirespeed Timer

Force Auto-MDIX Mode

RGMII RXD to RXC Skew

RGMII Enable

RGMII out-of-band status disable

Ethernet @Wirespeed Enable

Shadow Register Select

Register 19h: Auxiliary Status Summary

Auto-Negotiation Complete

Auto-Negotiation Complete Acknowledge

Auto-Negotiation Acknowledge Detect

Auto-Negotiation Ability Detect

Auto-Negotiation Next Page Wait

Auto-Negotiation HCD (Current Operating Speed and Duplex Mode)

Parallel Detection Fault

Remote Fault

Auto-Negotiation Page Received

Link Partner Auto-Negotiation Ability

Link Partner Next Page Ability

Link Status

Pause Resolution—Receive Direction and Transmit Direction

Register 1Ah: Interrupt Status

Energy Detect Change

Illegal Pair Swap

MDIX Status Change

Exceeded High Counter Threshold

Exceeded Low Counter Threshold

Auto-Negotiation Page Received

No HCD Link

No HCD

Negotiated Unsupported HCD

Scrambler Synchronization Error

Remote Receiver Status Change

Local Receiver Status Change

Duplex Mode Change

Link Speed Change

Link Status Change

CRC Error

Register 1Bh: Interrupt Mask

Interrupt Mask Vector

Register 1Ch Access

Register 1Ch (Shadow 00010): Spare Control 1

Write Enable

Shadow Register Selector

100BASE-FX Mode Copper Path

Link LED Mode

Register 1Ch (Shadow 00011): Clock Alignment Control

Write Enable

Shadow Register Selector

GTXCLK Clock Delay Enable

Register 1Ch (Shadow 00100): Spare Control 2

Write Enable

Shadow Register Selector

Energy Detect on INTR Pin

Register 1Ch (Shadow 00101): Spare Control 3

Write Enable

Shadow Register Selector

TXC/RXC Disable During Auto Power-Down

CLK125 Auto Power-Down

CLK125 Output

Register 1Ch (Shadow 01000): LED Status

Write Enable

Shadow Register Selector

Slave Indicator

FDX Indicator

INTR Indicator

LINKSPD Indicator

Transmit Indicator

Receive Indicator

Quality Indicator

Register 1Ch (Shadow 01001): LED Control

Write Enable

Shadow Register Selector

Activity/Link LED Enable

ACTIVITY LED Enable

Remote Fault LED Enable

Link Utilization LED Selector

Register 1Ch (Shadow 01010): Auto Power-Down

Write Enable

Shadow Register Selector

Auto Power-Down Mode

Sleep Timer Select

Wake-up Timer Select

Register 1Ch (Shadow 01100): External Control 2 Register

Write Enable

Shadow Register Selector

Enable IDDQ

Register 1Ch (Shadow 01101): LED Selector 1

Write Enable

Shadow Register Selector

LED2 Selector

LED1 Selector

Register 1Ch (Shadow 01110): LED Selector 2

Write Enable

Shadow Register Selector

LED4 Selector

LED3 Selector

Register 1Ch (Shadow 01111): LED GPIO Control/Status

Write Enable

Shadow Register Selector

LED I/O Status

Programmable LED I/O Control

Register 1Ch (Shadow 10001): SerDes 100-FX Status Register

Write Enable

Shadow Register Selector

100FX Link Status Change

Bad ESD Detected

False Carrier Detected

Transmit Error Detected

Receive Error Detected

Lock Timer Expired

Lost Lock

Faulting

Locked

100FX Link

Register 1Ch (Shadow 10011): SerDes 100-FX Control Register

Write Enable

Shadow Register Selector

100-FX Auto-Detect Timer Select

Disable RX Qualify

Force RX Qualify

Far End Fault Enable

Auto-Detect 100-FX SerDes

100-FX SerDes Full-Duplex

100-FX SerDes Enable

Register 1Ch (Shadow 10101): SGMII Slave Register

Write Enable

Shadow Register Selector

SerDes Link

SerDes Duplex

SerDes Speed

SerDes Link Status Change

Interface Select

RGMII SGMII Freq Lock Mode

SGMII Slave Mode

SGMII Slave Auto-Detection

Register 1Ch (Shadow 11000): 1000BASE-X Auto-Detect SGMII

Write Enable

Shadow Register Selector

SerDes Resolution Fault

1000BASE-T PCS Transmit FIFO Elasticity

SGMII 10/100BASE-T RX FIFO Frequency Lock Mode

Register 1Ch (Shadow 11110): Auto-Detect Medium Register

Write Enable

Shadow Register Selector

Invert Fiber SD From Pin

Fiber In Use LED Mode

Fiber LED Mode

Fiber Auto-Power Down Mode

Auto-Detect Medium Default

Auto-Detect Medium Priority

Auto-Detect Medium Enable

Register 1Ch (Shadow 11111): Mode Control Register

Write Enable

Shadow Register Selector

Interface Mode Select Change

Copper Link

SerDes link

Copper Energy Detect

Fiber Signal Detect

Interface Select

Enable 1000-X Registers

Register 1Dh (Bit 15 = 0): Master/Slave Seed

Enable Shadow Register

Master/Slave Seed Match

Link Partner Repeater/DTE Bit

Link Partner Manual Master/Slave Configuration Value

Link Partner Manual Master/Slave Configuration Enable

Local Master/Slave Seed Value

Register 1Dh (Bit 15 = 1): HCD Status

Enable Shadow Register

HCD 1000BASE-T FDX

HCD 1000BASE-T

HCD 100BASE-TX FDX

HCD 100BASE-TX

HCD 10BASE-T FDX

HCD 10BASE-T

HCD 1000BASE-T FDX (Link Never Came Up)

HCD 1000BASE-T (Link Never Came Up)

HCD 100BASE-TX FDX (Link Never Came Up)

HCD 100BASE-TX (Link Never Came Up)

HCD 10BASE-T FDX (Link Never Came Up)

HCD 10BASE-T FDX (Link Never Came Up)

Register 1Eh: Test Register 1

CRC Error Counter Selector

Force Link

Manual Swap MDI State

SerDes Register Descriptions

1000BASE-X MII Control

Reset

Internal Loopback

Auto-Negotiation Enable

Power-Down

Isolate

Restart Auto-negotiation

Duplex Mode

Collision Test

1000BASE-X MII Status

100BASE-T4 Capable

100BASE-X Full-Duplex Capable

100BASE-X Half-Duplex Capable

10BASE-T Full-Duplex Capable

10BASE-T Half-Duplex Capable

100BASE-T2 Full-Duplex Capable

100BASE-T2 Half-Duplex Capable

Extended Status

Management Frames Preamble Suppression

Auto-Negotiation Complete

Remote Fault

Auto-negotiation Ability

Link Status

Jabber Detect

Extended Capability

1000BASE-X Auto-Negotiation Advertisement

Remote Fault

Pause

Half-Duplex Capable

Full-Duplex Capable

1000BASE-X Auto-Negotiation Link Partner Ability

1000BASE-X Mode

Next Page

Acknowledge

Remote Fault

Pause

Half-Duplex Capable

Full-Duplex Capable

SGMII Mode

Copper Link

Acknowledge

Copper Duplex

Copper Speed

1000BASE-X Auto-Negotiation Extended Status

Next Page Capable

Page Received

1000BASE-X IEEE Extended Status

1000BASE-X Full-Duplex Capable

1000BASE-X Half-Duplex Capable

1000BASE-T Full-Duplex Capable

1000BASE-T Half-Duplex Capable

Expansion Registers

Expansion Register 00h: Receive/Transmit Packet Counter

Packet Counter

Expansion Register 04h: Multicolor LED Selector

Flash Now

In Phase

MULTICOLOR[2] LED Selector

MULTICOLOR[1] LED Selector

Expansion Register 05h: Multicolor LED Flash Rate Controls

Alternating Rate

Flash Rate

Expansion Register 06h: Multicolor LED Programmable Blink Controls

Blink Update Now

Blink Rate

Expansion Register 08h: 10BT Controls

Auto Early DAC Wake

Expansion Register 0Eh: Synchronous Ethernet Controls

MII-Lite Enable

TX SOP Enable

TX SOP Select

RX SOP Enable

RX SOP Select

RXCLK Select

RX_ER Mux Control

Expansion Register 44h: Recovered Clock Controls

Recovered Clock Enable

Section 6: Timing and AC Characteristics

Section 7: Electrical Characteristics

Section 8: Mechanical and Thermal

RoHS-Compliant Packaging

Mechanical Information

Thermal Information

Section 9: Ordering Information

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc