电快速瞬变脉冲群(EFT)抗扰度设计注意事项

AN80994

作者:Shruti Hanumanthaiah、Srinivas NVNS

相关项目:无

相关器件系列:所有 PSoC 器件

相关应用笔记:AN2155、AN78175

AN80994 介绍了提高嵌入式系统设计中的电快速瞬变脉冲群(EFT)抗扰度的最佳实践。本应用笔记说明了快速瞬变脉冲群对

混合信号的嵌入式控制器的影响,并提供了提高 EFT 抗扰度方法,以及有助于降低这些影响的设计建议。 它还总结了

IEC 61000-4-4 EFT 测试要求。

6.3 目标板设计时的注意事项 ............................... 20

6.4 固件技术 ........................................................ 36

7 总结 ........................................................................ 38

8 关于作者 ................................................................. 38

9 参考材料 ................................................................. 39

A 附录 A:IEC 61000-4-4 EFT 测试要求 ................... 40

A.1 测试等级 ........................................................ 40

A.2 测试装置 ........................................................ 41

A.3 测试程序 ........................................................ 42

文档修订记录................................................................... 44

全球销售和设计支持 ........................................................ 45

产品 ................................................................................. 45

PSoC®解决方案 ............................................................... 45

赛普拉斯开发者社区 ........................................................ 45

技术支持 .......................................................................... 45

目录

1 简介 .......................................................................... 2

EFT 是什么? ............................................................ 2

2

2.1 EFT 波形特性 ...................................................... 3

3 故障模式 ................................................................... 4

3.1 复位 ................................................................. 5

3.2 闩锁 ................................................................. 6

3.3 模拟和数字信号的损坏 ..................................... 7

3.4 通信故障 .......................................................... 7

3.5 存储器破坏 ....................................................... 8

4 性能标准 ................................................................... 8

5 故障排除以及提高某出错系统的 EFT 抗干扰方法 ..... 8

5.1 系统 ................................................................. 9

5.2 PCB 布局........................................................... 11

5.3 原理图 ............................................................ 13

6 设计注意事项和错误降低技术 ................................. 16

6.1 系统级注意事项 .............................................. 17

6.2 电源供电设计注意事项 ................................... 18

安全注意事项

EFT 测试包含危险电压。

必须充分遵守电气安全规则。

请咨询获得认证的安全技术人员。

www.cypress.com

文档编号:002-03849 版本*A

1

�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

1 简介

本应用笔记说明了电快速瞬变脉冲群(EFT)对嵌入式控制器的影响,并提供了降低这些影响的硬件和固件技术。本应

用笔记还介绍了一系列指南,使用这些指南,设计人员能够构建瞬变抗扰系统。

制订了国际标准,以便说明瞬变特性。这些标准还给产品设计人员提供了有关合规性的测试方法的指导。电气产品快速

瞬变抗扰度要求由国际电工委员会( IEC)在 IEC 61000-4-4 中(针对 EFT)定义。

EFT 是什么?章节说明了 IEC 61000-4-4 标准中所定义的 EFT 以及测试波形的特性。下一章节,故障模式,则介绍了

瞬变可能给嵌入式系统造成的影响。故障排除以及提高某出错系统的 EFT 抗干扰方法章节中提供了调试技巧,并列出

了一些提高故障系统的 EFT 抗扰度的可用方法。

设计工程师的首要目标是:即使在非导电环境下使用,也要确保一个终端产品正常操作及其性能。通常,重点内容为产

品的功能,而不是系统本身。设计工程师必须考虑产品设计方面的内容,包括多个问题,比如电磁干扰和抗扰度要求。

如果一个产品未通过兼容测试(EFT 或其他测试),则需要重新设计或返工。这样,设计成本会明显增加。这些成本

还不包括延迟时间、客户的不满以及市场份额流失。因此,进行系统设计的同时,设计工程师应尽量降低系统的错误。

设计注意事项和错误降低技术章节说明了系统设计工程师通过考虑某些设计时间规则可以预先阻止的有关 EFT 的问题。

本应用笔记的重点内容是目标电路板设计中的注意事项。它还总结了一个系统及其电源的某些重要设计注意事项。此外,

它还提供了固件技术,这些技术可由错误检测和恢复机制组成。

附录部分介绍了 IEC 61000-4-4 标准的总结。本应用笔记还提供了资料以供参考。

2

EFT 是什么?

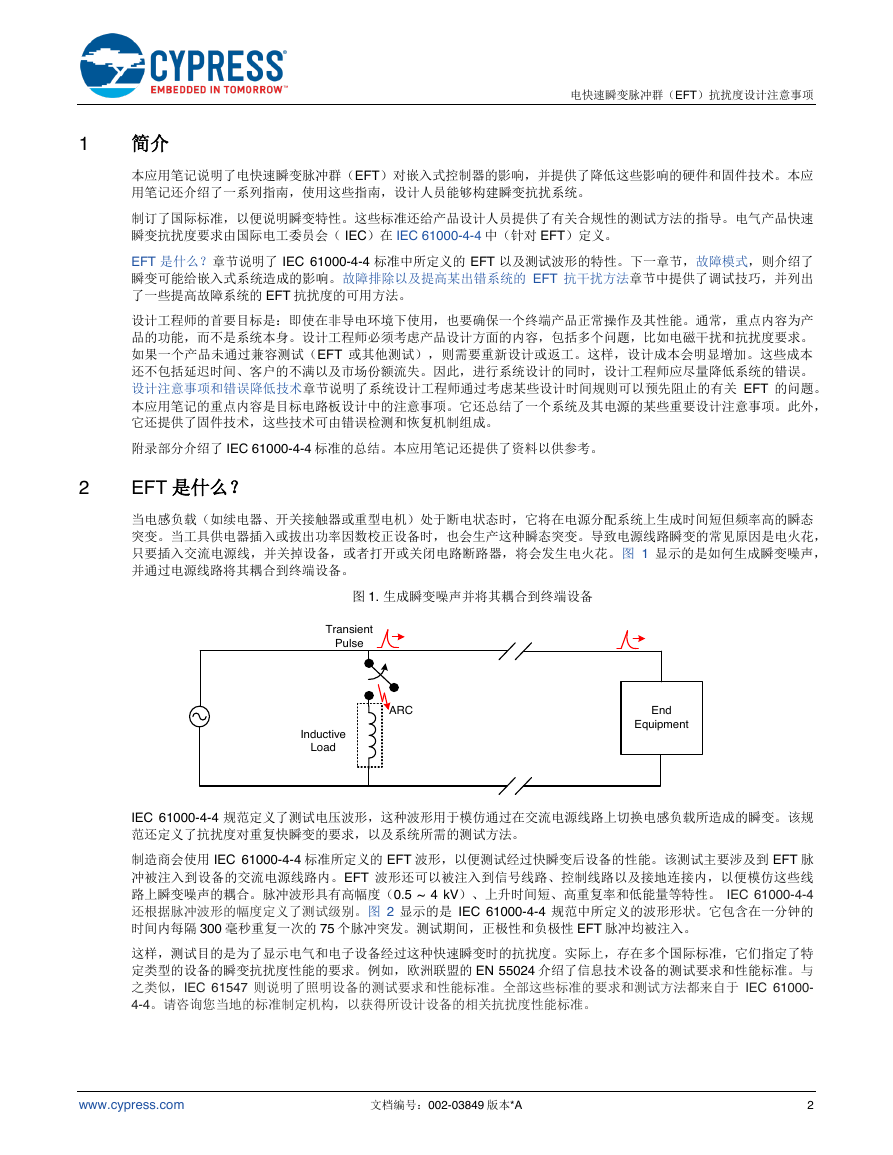

当电感负载(如续电器、开关接触器或重型电机)处于断电状态时,它将在电源分配系统上生成时间短但频率高的瞬态

突变。当工具供电器插入或拔出功率因数校正设备时,也会生产这种瞬态突变。导致电源线路瞬变的常见原因是电火花,

只要插入交流电源线,并关掉设备,或者打开或关闭电路断路器,将会发生电火花。图 1 显示的是如何生成瞬变噪声,

并通过电源线路将其耦合到终端设备。

图 1. 生成瞬变噪声并将其耦合到终端设备

IEC 61000-4-4 规范定义了测试电压波形,这种波形用于模仿通过在交流电源线路上切换电感负载所造成的瞬变。该规

范还定义了抗扰度对重复快瞬变的要求,以及系统所需的测试方法。

制造商会使用 IEC 61000-4-4 标准所定义的 EFT 波形,以便测试经过快瞬变后设备的性能。该测试主要涉及到 EFT 脉

冲被注入到设备的交流电源线路内。EFT 波形还可以被注入到信号线路、控制线路以及接地连接内,以便模仿这些线

路上瞬变噪声的耦合。脉冲波形具有高幅度(0.5 ~ 4 kV)、上升时间短、高重复率和低能量等特性。 IEC 61000-4-4

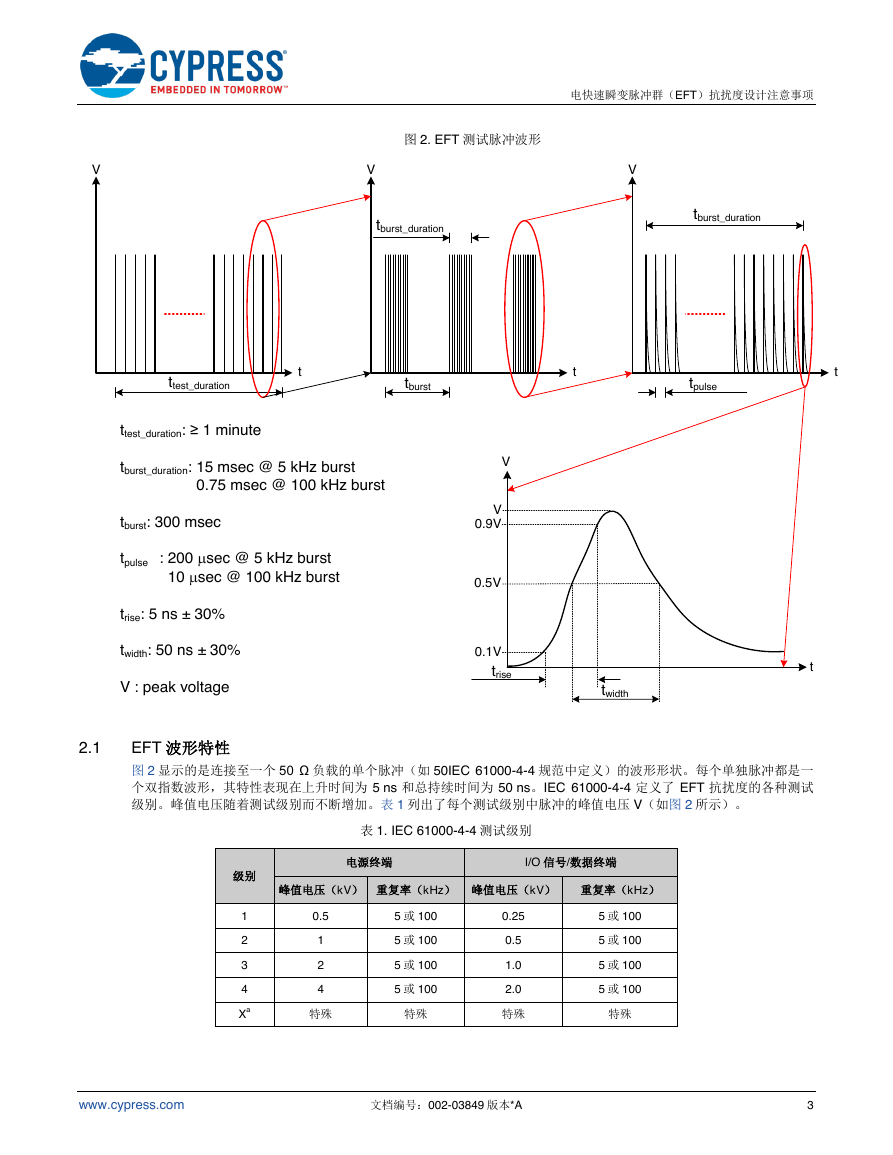

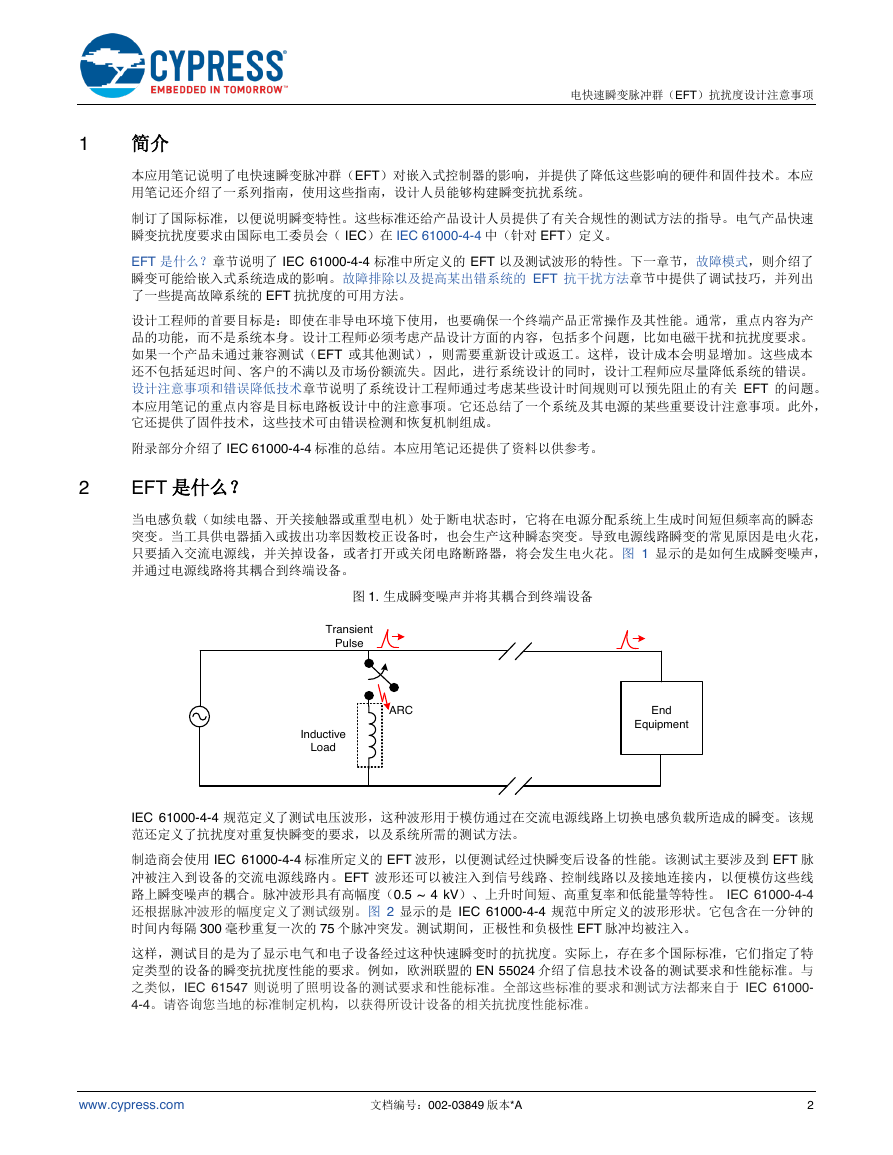

还根据脉冲波形的幅度定义了测试级别。图 2 显示的是 IEC 61000-4-4 规范中所定义的波形形状。它包含在一分钟的

时间内每隔 300 毫秒重复一次的 75 个脉冲突发。测试期间,正极性和负极性 EFT 脉冲均被注入。

这样,测试目的是为了显示电气和电子设备经过这种快速瞬变时的抗扰度。实际上,存在多个国际标准,它们指定了特

定类型的设备的瞬变抗扰度性能的要求。例如,欧洲联盟的 EN 55024 介绍了信息技术设备的测试要求和性能标准。与

之类似,IEC 61547 则说明了照明设备的测试要求和性能标准。全部这些标准的要求和测试方法都来自于 IEC 61000-

4-4。请咨询您当地的标准制定机构,以获得所设计设备的相关抗扰度性能标准。

www.cypress.com

文档编号:002-03849 版本*A

2

Inductive LoadEnd EquipmentARCTransient Pulse�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

图 2. EFT 测试脉冲波形

2.1

EFT 波形特性

图 2 显示的是连接至一个 50 Ω 负载的单个脉冲(如 50IEC 61000-4-4 规范中定义)的波形形状。每个单独脉冲都是一

个双指数波形,其特性表现在上升时间为 5 ns 和总持续时间为 50 ns。IEC 61000-4-4 定义了 EFT 抗扰度的各种测试

级别。峰值电压随着测试级别而不断增加。表 1 列出了每个测试级别中脉冲的峰值电压 V(如图 2 所示)。

表 1. IEC 61000-4-4 测试级别

电源终端

I/O 信号/数据终端

峰值电压(kV) 重复率(kHz) 峰值电压(kV) 重复率(kHz)

0.5

1

2

4

特殊

5 或 100

5 或 100

5 或 100

5 或 100

特殊

0.25

0.5

1.0

2.0

特殊

5 或 100

5 或 100

5 或 100

5 或 100

特殊

级别

1

2

3

4

Xa

www.cypress.com

文档编号:002-03849 版本*A

3

VtVtVtttest_durationtbursttpulsetburst_durationtburst_durationttest_duration: ≥ 1 minutetburst_duration: 15 msec @ 5 kHz burst 0.75 msec @ 100 kHz bursttburst: 300 msectpulse: 200 sec @ 5 kHz burst 10 sec @ 100 kHz bursttrise: 5 ns ± 30%twidth: 50 ns ± 30%V : peak voltageVtV0.9V0.5V0.1Vtwidthtrise�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

注意 1:重复率的典型值为 5 kHz;但在现实生活中,100 kHz 更接近实际值。

注意 2:制造商决定了需要测试的终端。

“X”是一个特殊级别。该级别必须在设备规范中被指定。

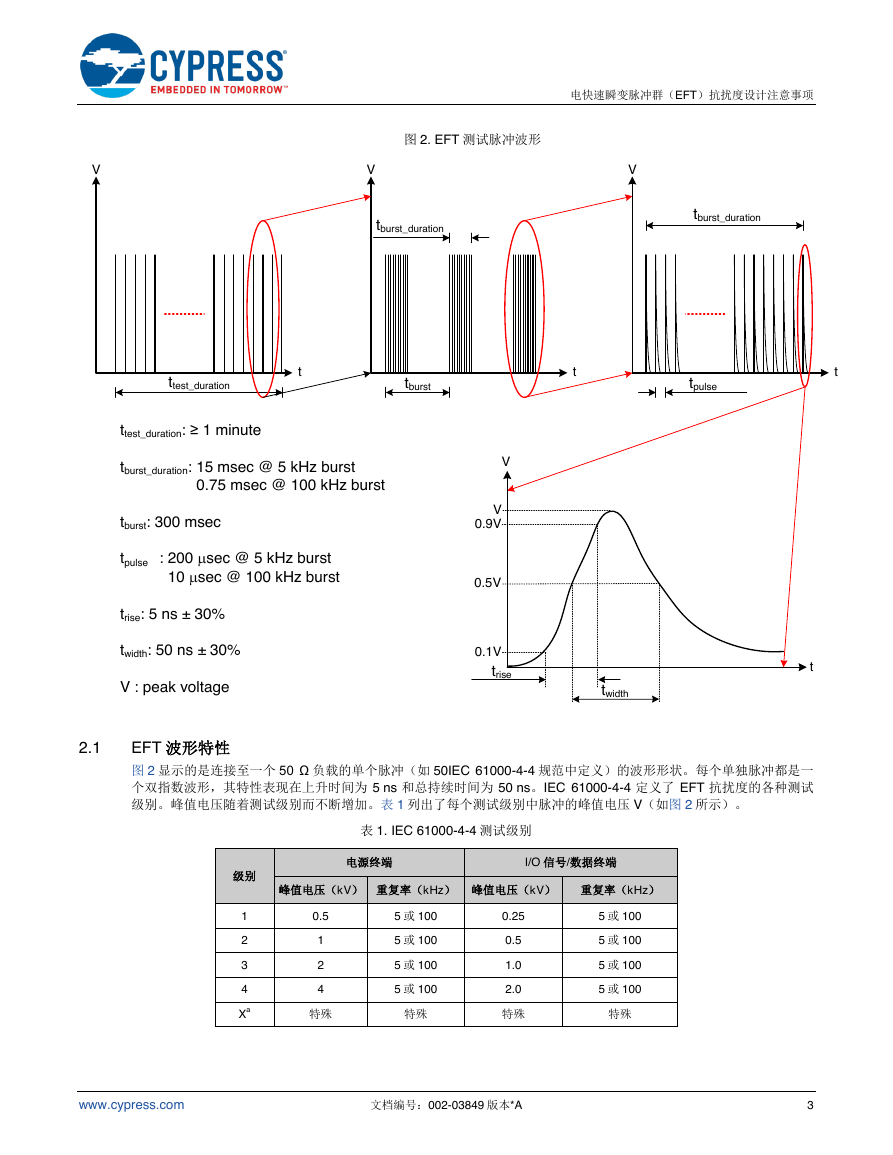

它有助于深入了解 EFT 突发的频谱。图 3 显示的是在 5 kHz 时脉冲突发的频谱。请注意,突发频率(5 kHz)可以是频

谱中最具优势的幅度之一。该问题应多加考虑。通常,过滤 EFT 脉冲相当容易,然而当提供了较低频率(5 或 100

kHz)的突发时,进行过滤会变得比较难。如果每 300 ms 低频率突发本身又被重复一次,这样将提供另一个频率为

3.33 Hz 的组件。

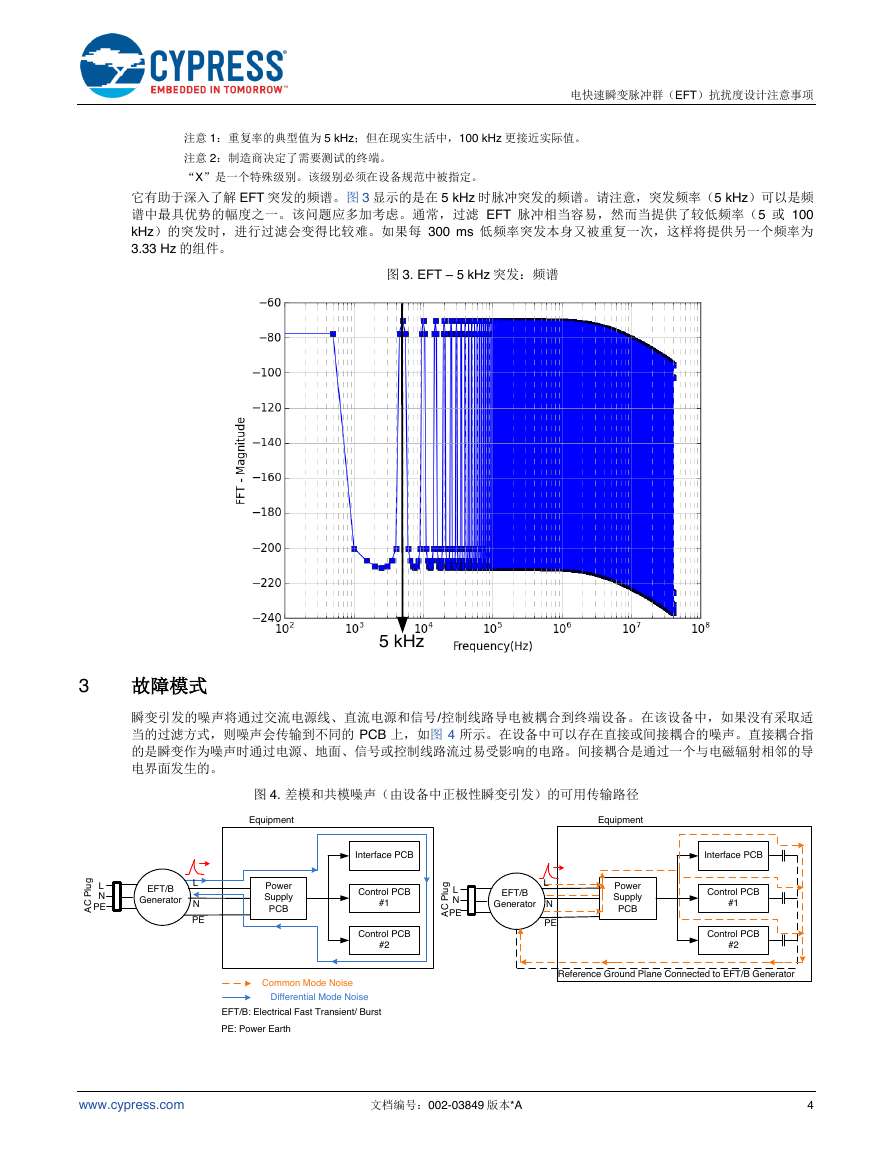

图 3. EFT – 5 kHz 突发:频谱

3 故障模式

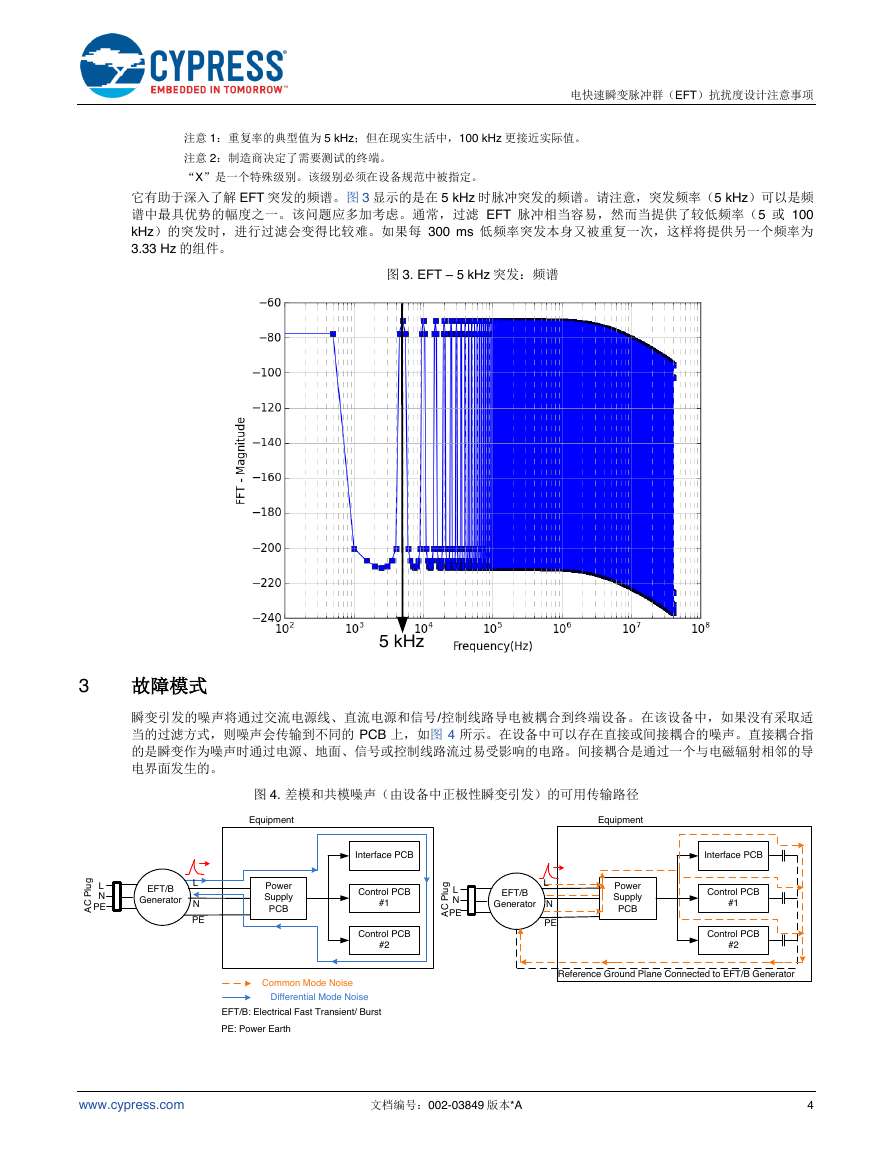

瞬变引发的噪声将通过交流电源线、直流电源和信号/控制线路导电被耦合到终端设备。在该设备中,如果没有采取适

当的过滤方式,则噪声会传输到不同的 PCB 上,如图 4 所示。在设备中可以存在直接或间接耦合的噪声。直接耦合指

的是瞬变作为噪声时通过电源、地面、信号或控制线路流过易受影响的电路。间接耦合是通过一个与电磁辐射相邻的导

电界面发生的。

图 4. 差模和共模噪声(由设备中正极性瞬变引发)的可用传输路径

www.cypress.com

文档编号:002-03849 版本*A

4

5 kHzCommon Mode NoiseDifferential Mode NoiseEFT/B: Electrical Fast Transient/ BurstEquipmentInterface PCBPower Supply PCBControl PCB #2Control PCB #1Reference Ground Plane Connected to EFT/B GeneratorAC PlugLNPENPELEFT/B GeneratorEquipmentInterface PCBPower Supply PCBControl PCB #2Control PCB #1AC PlugLNPEEFT/B GeneratorNPELPE: Power Earth�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

如图 4 所示,瞬变引发的噪声可能是共模噪声,也可能是差模噪声。共模噪声在两个导体中存在或被其“共用”。

通常,共模噪声存在于各导体的“同相位”中。差模噪声仅存在于一个导体中,或存在于两个导体的反相位中。

嵌入式控制器的设计目的是生成信号(如高速串行通信时钟,该信号的时序规范相当于瞬变引发的噪声的实现规范),

并在这些信号上进行操作。因此,瞬变引起的噪声会干扰这些信号。在广泛的分类中,以下模块、引脚和信号受瞬变引

发的噪声的影响最大:

电源与接地信号

复位电路

时钟/振荡器信号

边沿敏感的触发器

高频率数字信号

模拟信号

通信模块,如 I2C、SPI、UART

CPU

闪存/RAM

如果瞬变引发的噪声影响到这些模块中的一个或多个,则会发生以下系统故障类型:

复位

闩锁

模拟和数字信号的损坏

通信故障

存储器破坏

3.1 复位

由于瞬变引发的噪声,器件可以进行以下某种复位:

外部复位

上电复位

基于低压检测(LVD)的复位

欠压复位

看门狗复位

软件复位

复位引脚上瞬变引发的噪声可以触发一个外部复位。因此,根据复位引脚为高电平有效或低电平有效,一个外部复位可以因供电

电压降低或接地参考电压发生变化而发生。某些控制器还具有备用的复位引脚。在这种情况下,器件还可以因备用复位引脚上的

噪声而被复位。

www.cypress.com

文档编号:002-03849 版本*A

5

�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

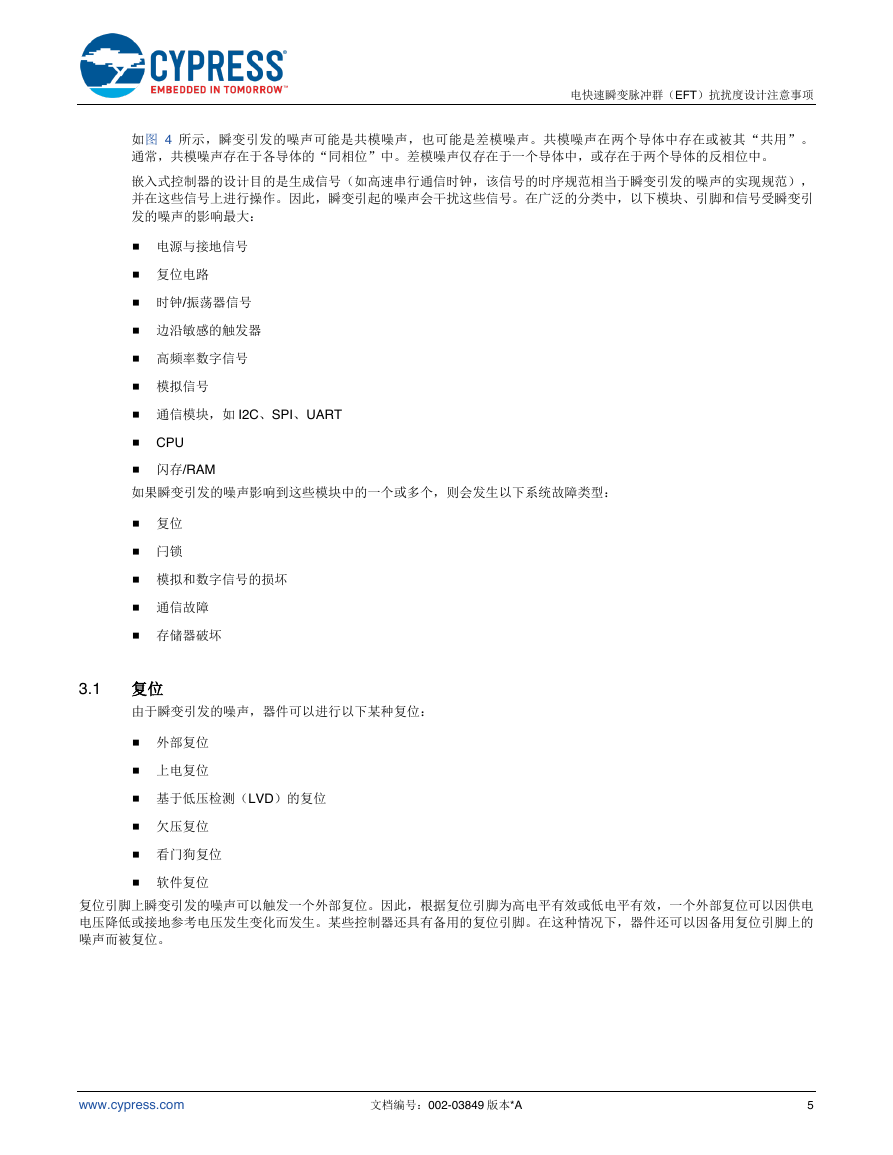

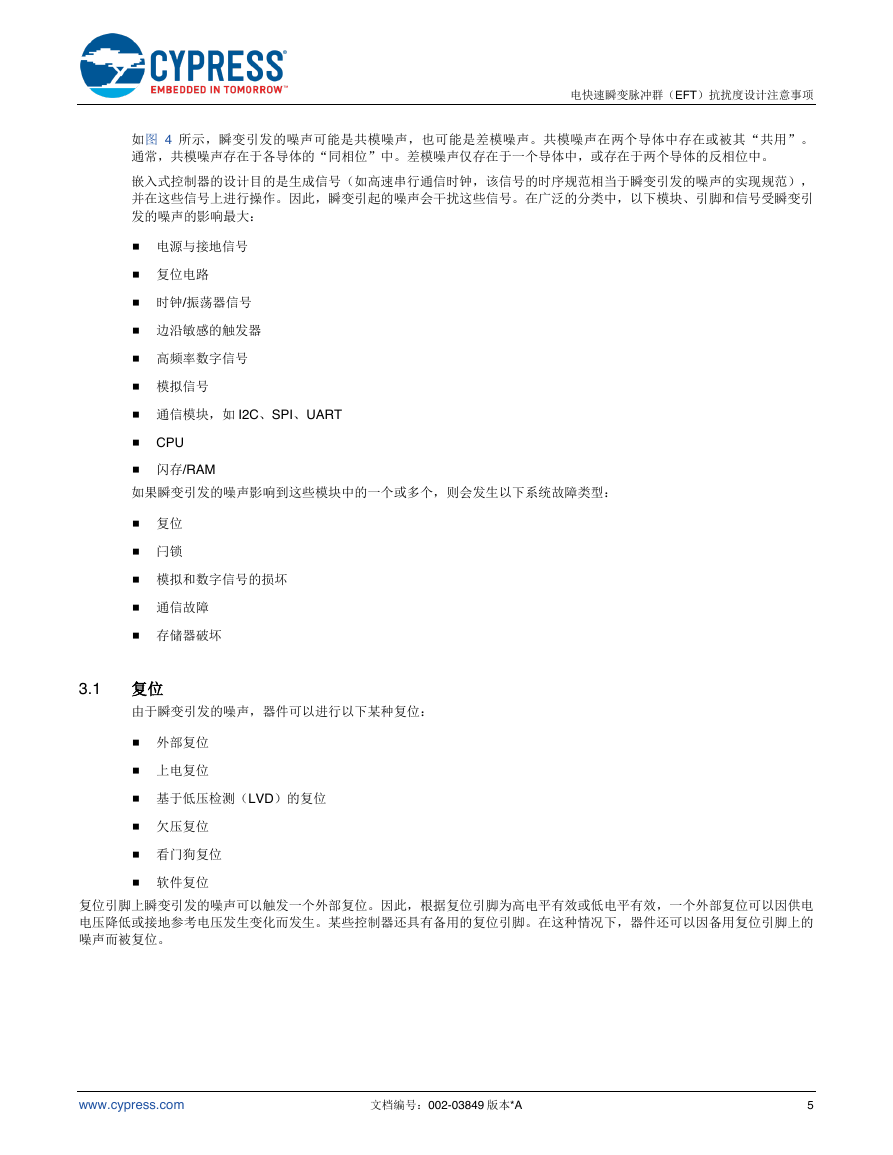

图 5.供电线路上的瞬变噪声波形(在一个交流-直流转换器的输出上测量得出)

图 5 显示的是 EFT 测试波形被注入到转换器时供电线路上的瞬变噪声波形(在一个交流-直流转换器的输出上测量得

出)。正如您所看到的,峰值电压为~350 V。当交流-直流转换器的输出端存在负载(如控制器电路)时,噪声的特性

可能会因滤波器以及控制器供电引脚上的去耦网络不同而不同。

上电、LVD 和欠压等复位类型将在以下各种情况下发生:

瞬变引发的噪声下拉了供电电压

瞬变引发的噪声改变了接地参考电压

瞬变引发的噪声触发了 I/O 上 ESD 钳制电路,使器件能够观察到有效供电电压降低,从而触发欠压复位

如果有效供电电压低于器件工作电压范围的最小值,则会发生上电复位。如果在控制器使能了欠压复位和基于 LVD 的

复位,则当有效供电电压低于触发电压并能够在超过最小时间内保持该电压值时,会发生这些事件。

如果固件无法及时清除看门狗定时器中的内容,那么会发生一个看门狗复位。这是因为一个故障子系统(如 CPU 或闪

存)通常会引起意外的固件操作。

如果检测出系统中的异常行为(如:由于信号完整性的损坏,主设备收到错误数据)时,主设备需要复位从设备,那么

将发生一个软件复位。如果代码执行不正常,并且输入了一个异常代码,也会发生软件复位。这种不正常的代码执行的

原因可能是 CPU、时钟、闪存或 RAM 中的损坏状态。

3.2 闩锁

闩锁指的是瞬变引发的噪声没有造成实际损害的系统故障类型。它会使能电路上的所有组件,从而使电源能够破坏器件,

或者电路无法运行(除非执行一个电源周期复位)。接地反弹或接地参考电压的变化(由瞬变引发的噪声导致)可以使

CMOS 电路进入闩锁状态。具体地讲,这是在 CMOS 电路的电源轨之间创建一个低阻抗路径的过程,从而触发一个承

载寄生电流的路径,该触发操作会破坏器件的正常运行。进行一个电源周期复位可纠正这种情况。由于过电流,闩锁会

引起器件的破坏。

www.cypress.com

文档编号:002-03849 版本*A

6

�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

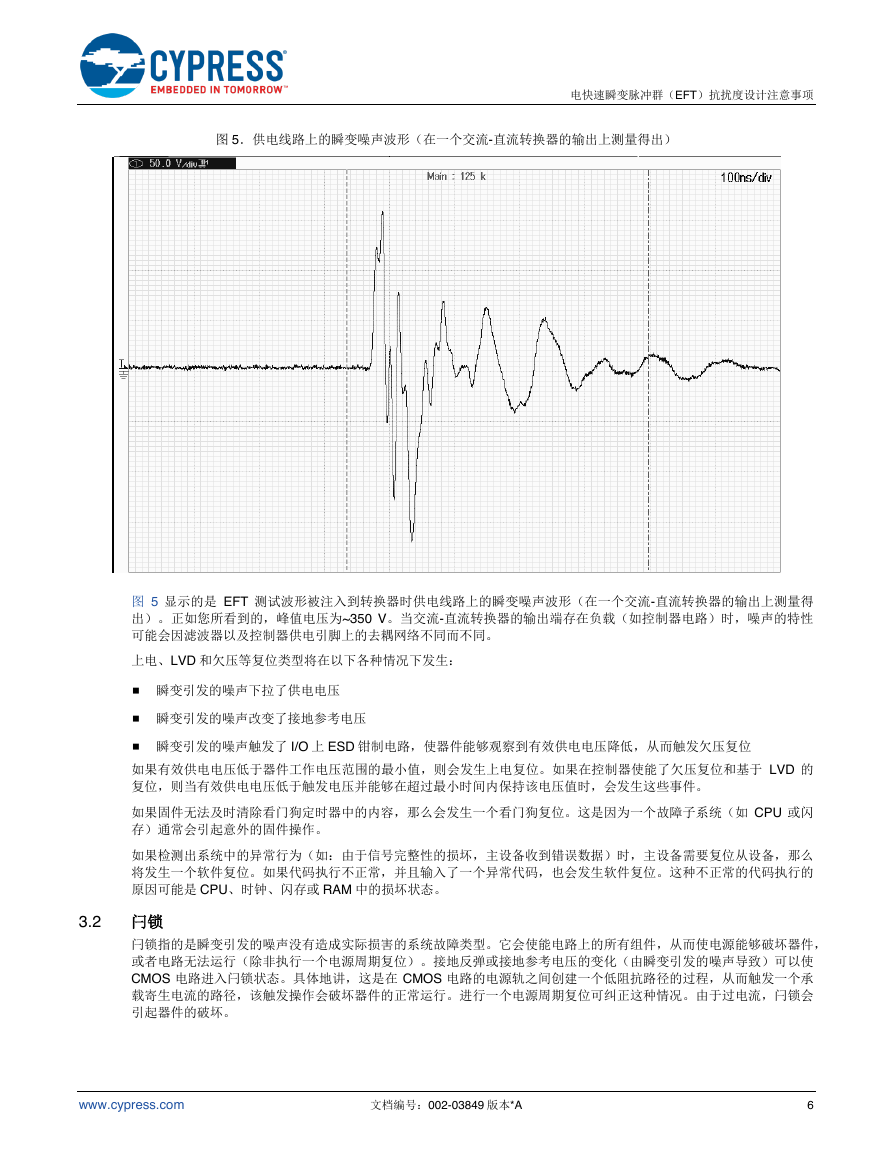

3.3 模拟和数字信号的损坏

与低带宽数字电路或慢速模拟电路相比,快速数字电路更容易发生基于 EFT 的故障。

边沿敏感的输入更易受瞬变引发的噪声的影响。即使已经使用了低通滤波器,一个足够大的瞬变能够注入的电能仍足以

破坏器件的操作。瞬变还可以作为毛刺传输,如图 6 所示。在输入是高速度数字输入(如时钟和数据输入)的情况下,

这些毛刺会被误认为是有效的数据脉冲。

图 6. I/O 信号上的毛刺(由瞬变导致)

振荡器/外部时钟引脚也会受瞬变噪声的影响。瞬变本身可以被控制器视为有效时钟脉冲。

由于信号的损坏,在模拟模块的模拟输入引脚上出现的瞬变,会导致失真数据。处理低电平模拟信号时,该效应可能更

严重。

通常,控制器上的输入/输出端口具有多种功能。通过更改引脚状态、驱动模式或引脚功能,瞬变事件也会破坏引脚/端

口的正常运行。在极端情况下,实际上,瞬变事件可以触发引脚上的 ESD 保护模块并使控制器进入闩锁状态。

3.4 通信故障

嵌入式应用中的常用通信协议分别是 I2C、SPI 和 UART。通信故障可以由以下原因引发:

控制器中的通信模块故障

瞬变引发的噪声(通过电源和地面传输到内部电路)可能会使该模块受到损害或应力。

时钟线路上的时钟延展或毛刺

时钟信号上的毛刺可能会破坏操作。另一方面,如果器件无法收到其他器件的 ACK 信号,时钟可能被延展。这可

能是由内部模块的故障或主设备的故障(需要发送 ACK)引起。当控制器中的状态机发生故障时,时钟也可能被

延展。

信号完整性破坏

由于电源和地面上的高噪声被传输到被引用的通信线路上,信号完整性可能受到破坏,因此违背了协议规范。

收发器的故障

在 UART 通信的另一端,I2C、SPI 主设备/从设备或发送器/接收器易受瞬变噪声的影响。这些器件的复位、损害或

故障会破坏该通信。

数据查看系统(如电脑)和控制器(如 USB 至 UART 桥接器、RS232、UART 电平转换器和串行线缆)间的接口

会发生故障。

本质上,UART 比 I2C 或 SPI 协议更稳定,因为在 UART 协议中,信号采样将在位时间窗口的中心进行,而 I2C 或 SPI

中的信号采样则在时钟边沿进行的。用于 UART 通信时,由于更高的电压电平,电平转换器提高了信号容限,从而提

高了 SNR。

www.cypress.com

文档编号:002-03849 版本*A

7

GlitchGlitch�

电快速瞬变脉冲群(EFT)抗扰度设计注意事项

3.5 存储器破坏

瞬变引发的噪声会破坏存储器(如闪存或 RAM),因为这些存储器会对系统时钟或闪存写入电压造成干扰。存储器被

破坏时,由于一个闪存校验和错误,系统可能会无法被启动,或者闪存或 RAM 中的损坏数据或代码可以使系统无法正

常操作。闪存损坏可能是永久性的,或者需要进行一个电源周期复位或重新编程才能恢复到正常状态。另一方面,由于

RAM 的损坏,要想恢复正常操作,可能需要进行一个电源周期复位或任意其他复位。

子系统故障可能是永久性的,也可能是暂时的。如果损害是永久性的,那么很容易检测出来。如果损害是暂时的(如闩

锁或存储器损坏),那么对设备执行电源周期复位能够恢复其正常操作状态。经过 EFT 测试时,子系统可能被部分损

害,但仍是功能齐全的。受到电源、高温度或不正常工作条件的影响时,被损害的组件可能会发生永久性的故障。这种

潜在影响很难被发现和解决。

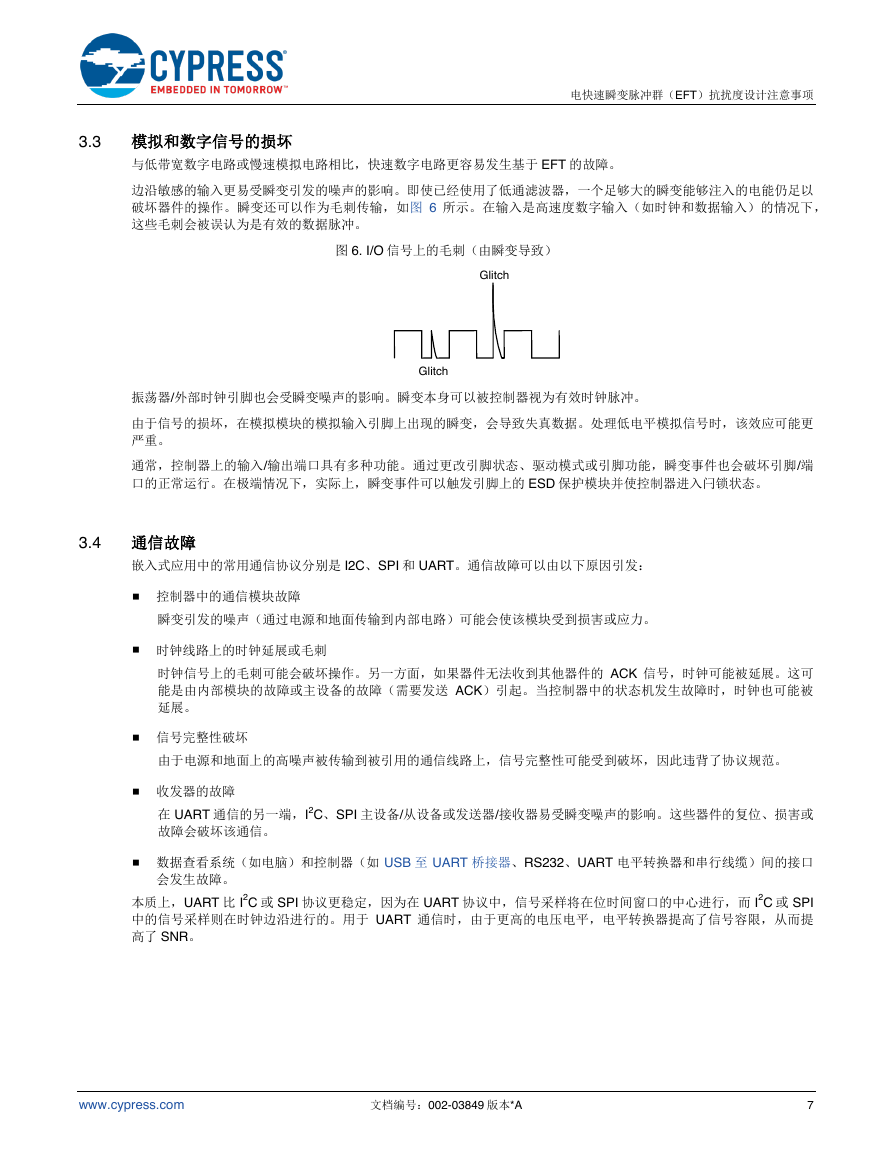

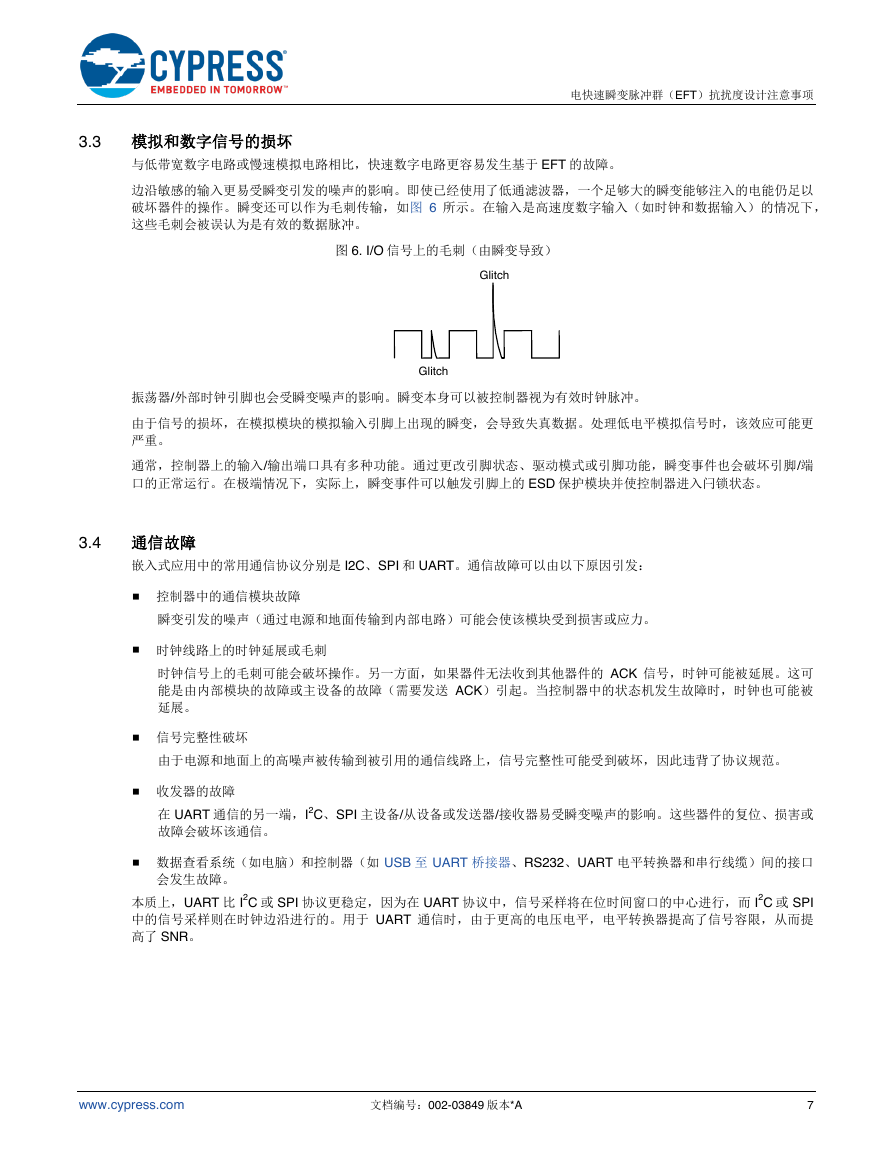

4 性能标准

一个控制器的功能损失或性能降低(与其规范在 IEC 61000-4-4 中所定义的性能相关)可被分为以下各种标准。

标准

说明

性能标准 A

测试后,正常的性能符合制造商指定的标准。

表 2. 性能标准

性能标准 B

测试期间,它们的功能会暂时损失或性能被降低;测试后,无需任何干预,控制器可以恢复其正常性能。

性能标准 C

测试期间,功能会暂时损失或性能被降低;测试后,需要干预才能使控制器恢复其正常性能。

性能标准 D

测试期间功能会损失,并且性能会降低;由于损害,控制器无法恢复正常状态。

需要特别注意的是,被评定为特定系统的故障条件可能与另一个系统无关。例如,在执行 EFT 测试期间,一个工业处

理控制器不能接受间接性的器件复位,但用户接口可接受这种复位。因此,必须考虑终端应用的要求及其容忍瞬变噪声

的能力。

5 故障排除以及提高某出错系统的 EFT 抗干扰方法

对瞬变引发的噪声问题进行有效的故障排除非常重要,但它通常被视为系统合规性测试的部分。在进行合规性测试时,

如果发生故障,设计师应确定故障原因。设计师和负责运行合规性测试的人必须合作确定故障的原因。

如果能确定故障类型,那么可以快速识别在使用微控制器的系统中发生的大多数故障。在进行 EFT 测试期间或在进行

该测试后,您应该确定在系统中所发生的故障类型(前面内容中介绍了这些类型)以及它们的原因。

您一旦确定了相关故障的原因,请逐步解决它。下面是一些故障排除的提示:

1. 查找复位相关的问题时,在测试期间检测该控制器的供电引脚并查找明显的原因。在固件中设置一个调试程序,

用于指示一个复位。

2. 如果发生了某个栓锁,请观察由控制器抽取的电流是否超过它的普通额定值。在其他情况下,请通过引入调试程序

来查找一个固件冻结。

3. 对于模拟或时钟相关问题,请检测相关的 I/O 线以发现噪声或短时脉冲。如果同某个器件的通信被限制,则需要注

意时钟延展。

4. 如果闪存/RAM 被损坏,则应该配置一个固件调试程序(如端口引脚切换)并监控该引脚的状态,从而检查固件流

程是否满足预期条件。在进行这些测试期间以及进行这些测试后,请读取受影响存储器中的内容。

请注意,建议使用带有隔离接地的示波器。否则,示波器接地会分流瞬变噪声,从而使读取结果有误。在典型的示波器

中,信号接地端被内部接地。请参考图 7。

www.cypress.com

文档编号:002-03849 版本*A

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc