BiCMOS带隙基准电压源的设计及应用

带隙基准电压源的设计及应用

基于0.18 μm SiGe BiCMOS工艺,设计了应用于一款“10-Gbps 跨阻放大器(TIA)”芯片的带隙基准电压源。该

带隙基准电压源工作在3.0 V~3.6 V的电源电压下,输出基准参考电压为1.2 V,温度系数为10.0 ppm/℃,低频时

电源抑制比为-69 dB,具有良好的性能。应用该带隙基准电压源完成了TIA芯片中偏置电路模块的设计,该偏置

电路除了提供偏置电流外,还具备带宽调节功能,可实现对TIA输出电压信号带宽进行7.9 GHz、8.9 GHz、9.8

GHz和10.1 GHz四档调节,提高了TIA芯片的应用性。目前,带隙基准电压源与偏置电路随TIA芯片正在进行

MPW(多项目晶圆)流片。

0 引言引言

得益于集成电路技术的深入研究与迅速发展,各类基于模拟、数字技术的通信设备和消费品已成为当今一大热点。[1]。

带隙基准电压源广泛应用于光接收机前置跨阻放大器(TIA)、模数转换器(ADC)、数模转换器(DAC)、低压差线性稳

压器(LDO)、温度传感器、电压检测器、高精度比较器等模拟和数模混合集成电路中,是不可缺少的关键基本模块,其性

能很大程度上决定了系统集成芯片的性能。

基于CMOS工艺的带隙基准源,可以实现高集成度,达到较低的功耗;基于双极型工艺的带隙基准源,在高速电路有着广

泛的应用,有着很强的电流驱动能力。而[2]。

1 带隙基准电压源工作原理

带隙基准电压源工作原理

带隙基准电压源的目标是产生一个基准电压——与电源和工艺均不存在关系,且同时具有确定微小温度特性。假设电压

V1随温度升高而减小,电压V2随温度升高而增加,选取适当的系数α1和α2使得α1×( V1/ T)+α2×( V2/ T)=0。因此,能够

获得带隙基准电压,即有VREF=α1V1+α2V2。

1.1 Brokaw带隙基准电压源结构

带隙基准电压源结构

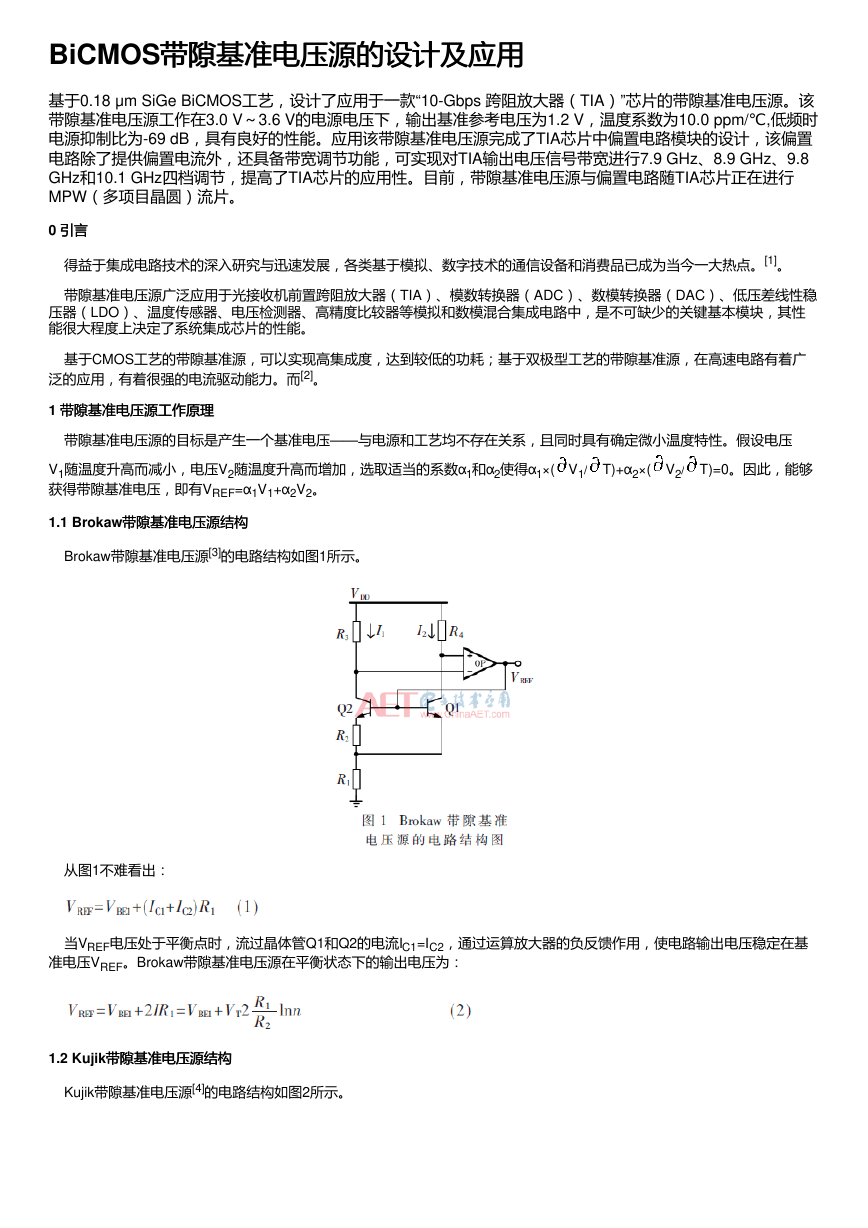

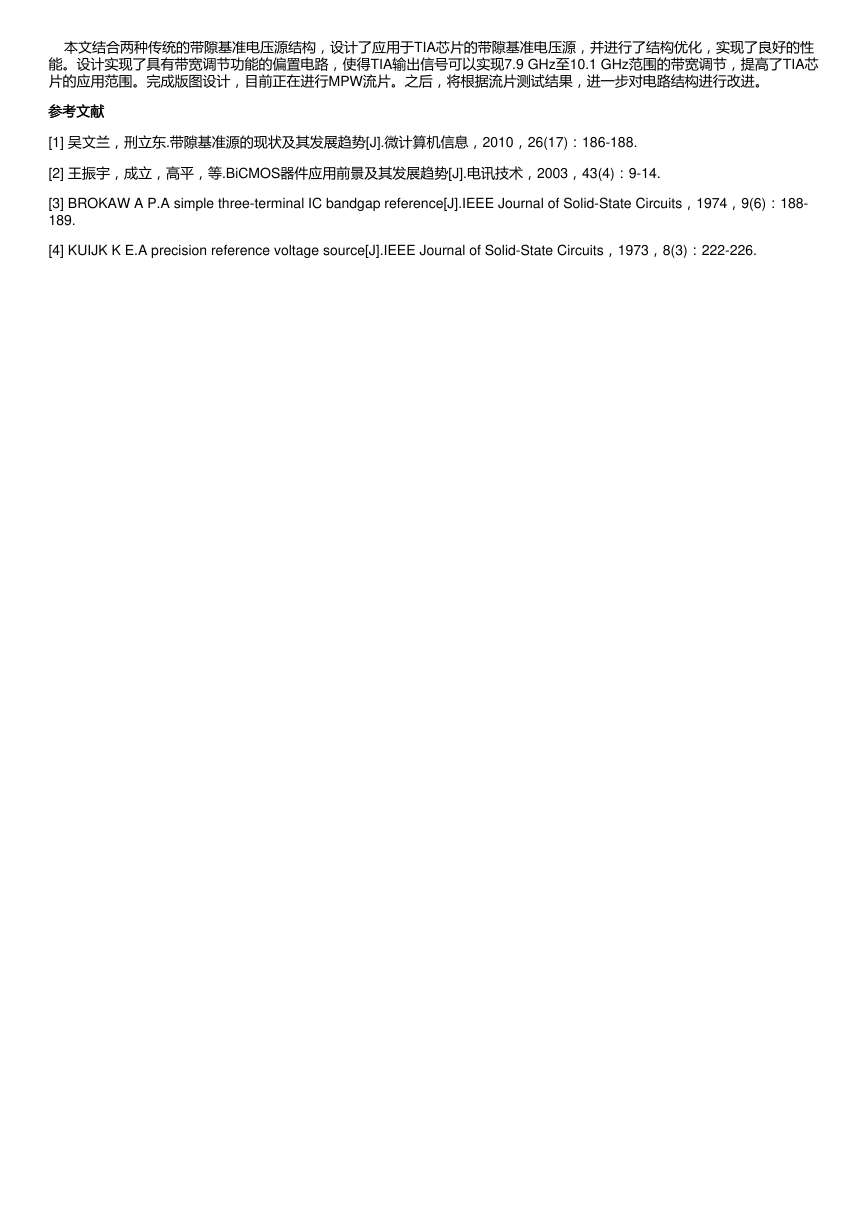

Brokaw带隙基准电压源[3]的电路结构如图1所示。

从图1不难看出:

当VREF电压处于平衡点时,流过晶体管Q1和Q2的电流IC1=IC2,通过运算放大器的负反馈作用,使电路输出电压稳定在基

准电压VREF。Brokaw带隙基准电压源在平衡状态下的输出电压为:

1.2 Kujik带隙基准电压源结构

带隙基准电压源结构

Kujik带隙基准电压源[4]的电路结构如图2所示。

�

该电路结构与Brokaw带隙基准电压源电路结构有相似之处,通过运算放大器的负反馈作用,得到稳定的带隙基准电压

VREF。

图中PNP晶体管Q1和Q2为二极管接法的双极型晶体管,根据运算放大器的“虚短”、“虚断”特性,可以得到输出电压

VREF为:

2 BiCMOS带隙基准电压源的设计

带隙基准电压源的设计

2.1 电路分析

电路分析

结合上述两种带隙基准电压源结构进行相应改进后,本文中的带隙基准电压源的整体电路如图3所示。

为了提高电路系统的稳定性,利用“密勒效应”,在运算放大器的两级之间添加一个大的电容进行密勒补偿,得到一个低频极

点。电容被分成几个并联以及采用了MOS管电容,电阻也被分开采用了串联的连接方式,均是考虑到了版图设计以及匹配性

的需求。

在传统的核心电路结构中,都是采用MOS管来为核心电路提供偏置电流,而本设计采用npn晶体管来提供偏置电流。通过

前面的分析,可以得知使用MOS来提供偏置电流,会出现传输电流为零的“简并点”现象,需要启动电路来激励,而npn晶体管

则不存在这种“简并点”,因此本设计中的核心电路不需要启动电路来进行激励。此外,运算放大器与晶体管Q3和Q4、电阻

R3和R4共同构成反馈回路。因为设计目标中的输出电压为1.2 V,双极型晶体管的基极-发射极电压VBE约为0.8 V,而电源电

压为3.3 V,因此需要使用电阻进行分压,否则难以得到1.2 V的输出电压。

晶体管Q1和Q2采用二极管连接方式,它们的发射极面积不相等,其面积的比值为n:1。本文中两个晶体管的发射极面积比

值为16:2,即n=8,取该值一是降低失调的影响,二是提高器件匹配性,因此这两个晶体管的基极-发射极电压VBE也不相等。

由VB1=VB2可得:

�

则可得晶体管Q1和Q2的基极-发射极电压VBE的差值ΔVBE为:

因此,调节上式中的电阻的比值,便可以得到接近理想温度系数的带隙基准电压。

图3的放大器结构中,PMOS管M1、M2和M3都是允许传输零电流的,此时运算放大器无法正常工作,因为NMOS管M3的

漏极存在零简并点。为了破坏这个“简并点”,需要一个启动电路来进行激励。晶体管Q7、Q8、Q9和电阻R8构成的支路有电流

传输,由于3个晶体管都是以二极管的形式连接的,且每个晶体管的基极-发射极的电压VBE为0.8 V,则Q10的基极电压为3个

VBE,即2.4 V,因此该晶体管会迅速开启,并有电流传输,其发射极连接在运算放大器电路中的MOS管M3的漏极和M5的漏

极之间,则Q10的发射极电流会迅速注入这两个MOS管,进而抬高节点电位,激励MOS管导通,从而使运算放大器达到正常

工作状态。待整个带隙基准电路处于稳定工作状态时, Q10发射极电位将被拉至带隙基准电压VREF与一个基极-发射极电压

VBE之和,即2.0 V,此时Q10的基、射两极之间的压降将会降到0.4 V,Q10关断,不再有电流传输,节省了功耗。

2.2 版图及后仿真

版图及后仿真

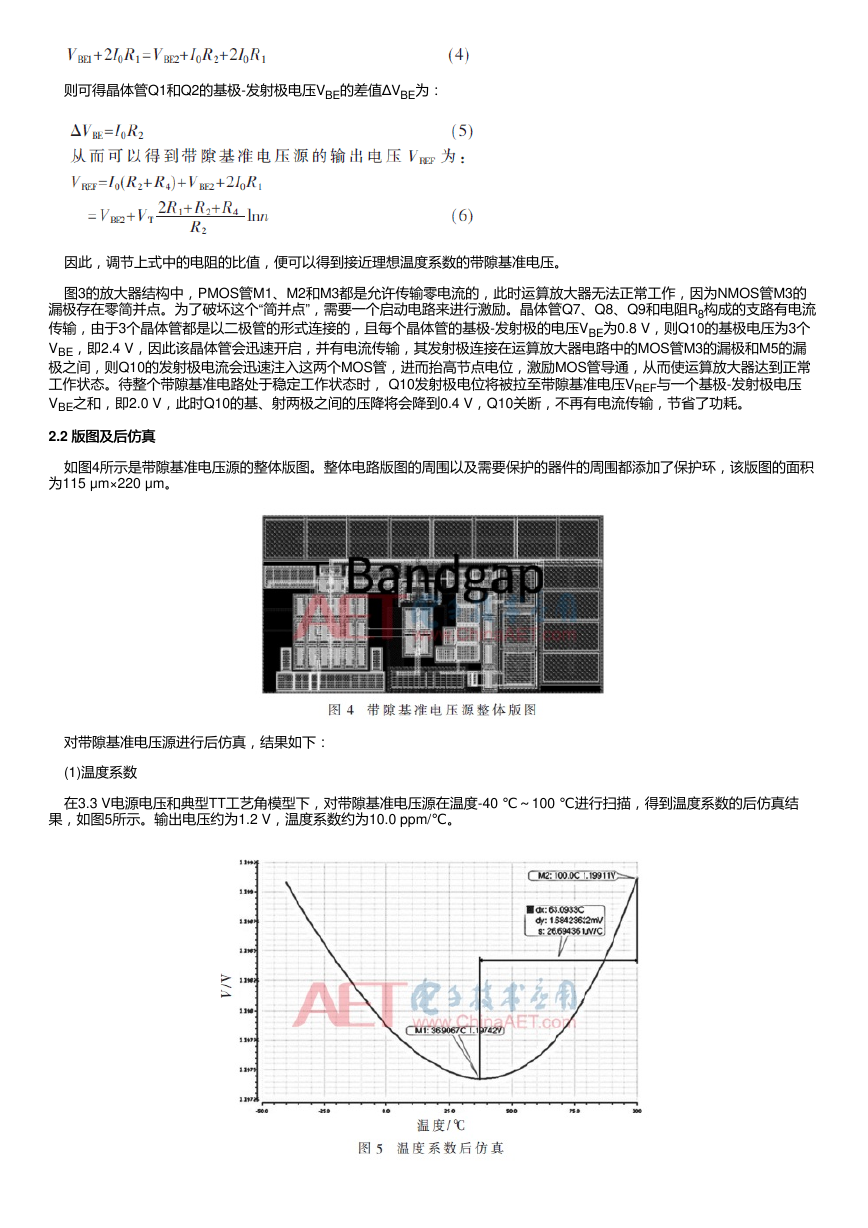

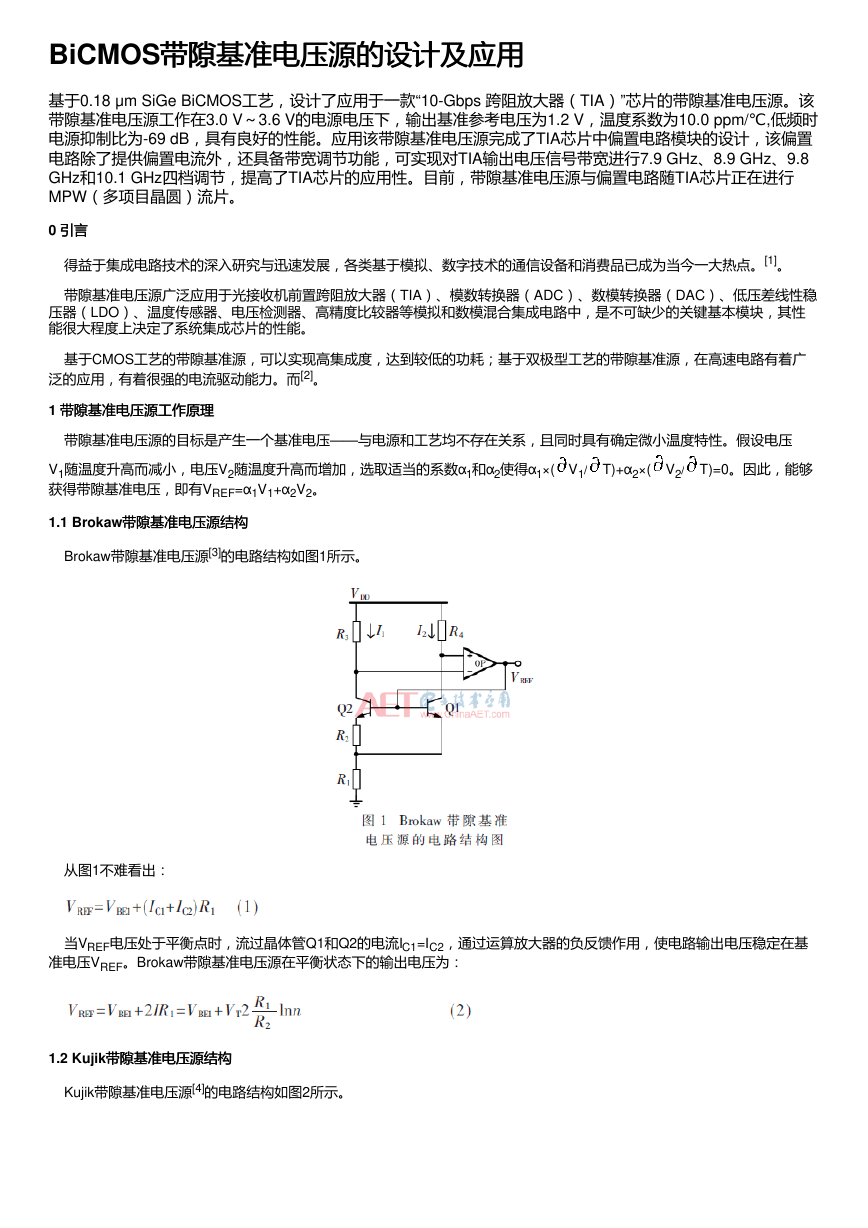

如图4所示是带隙基准电压源的整体版图。整体电路版图的周围以及需要保护的器件的周围都添加了保护环,该版图的面积

为115 μm×220 μm。

对带隙基准电压源进行后仿真,结果如下:

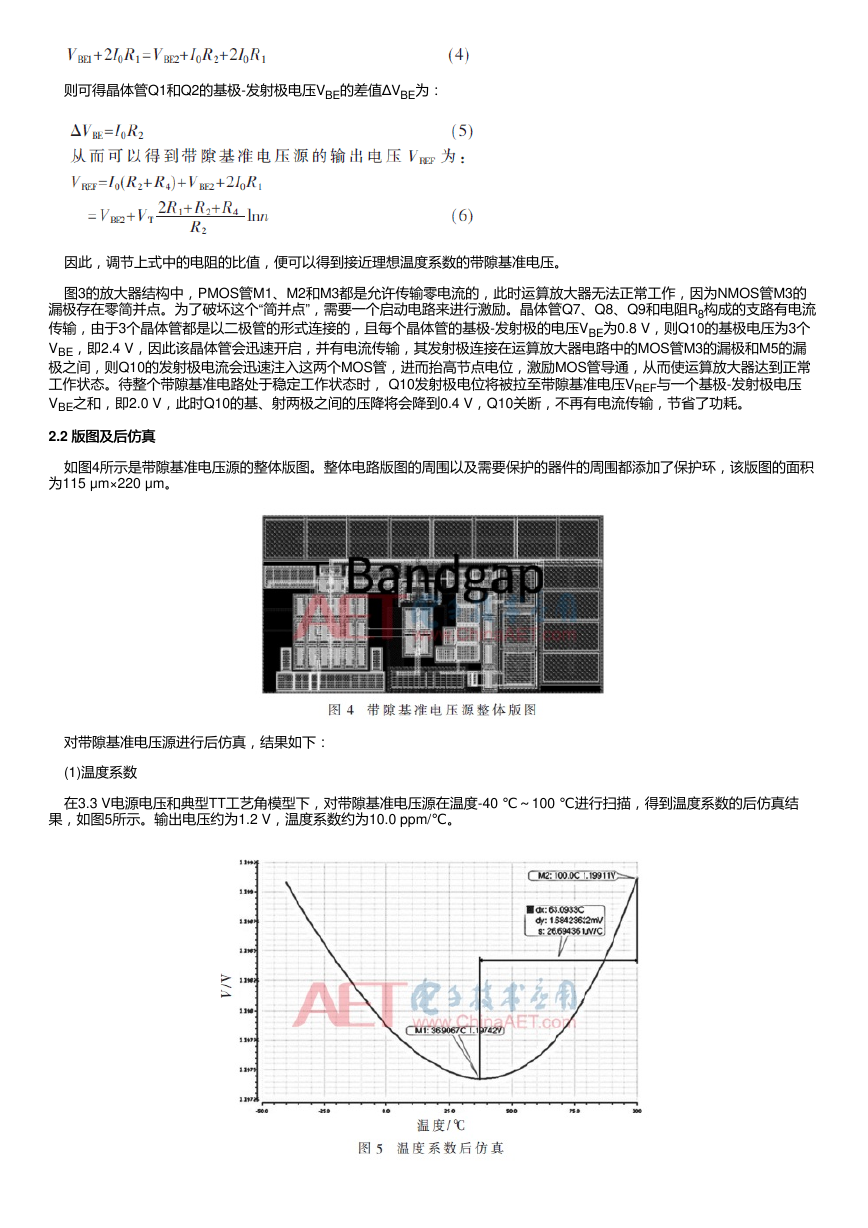

(1)温度系数

在3.3 V电源电压和典型TT工艺角模型下,对带隙基准电压源在温度-40 ℃~100 ℃进行扫描,得到温度系数的后仿真结

果,如图5所示。输出电压约为1.2 V,温度系数约为10.0 ppm/℃。

�

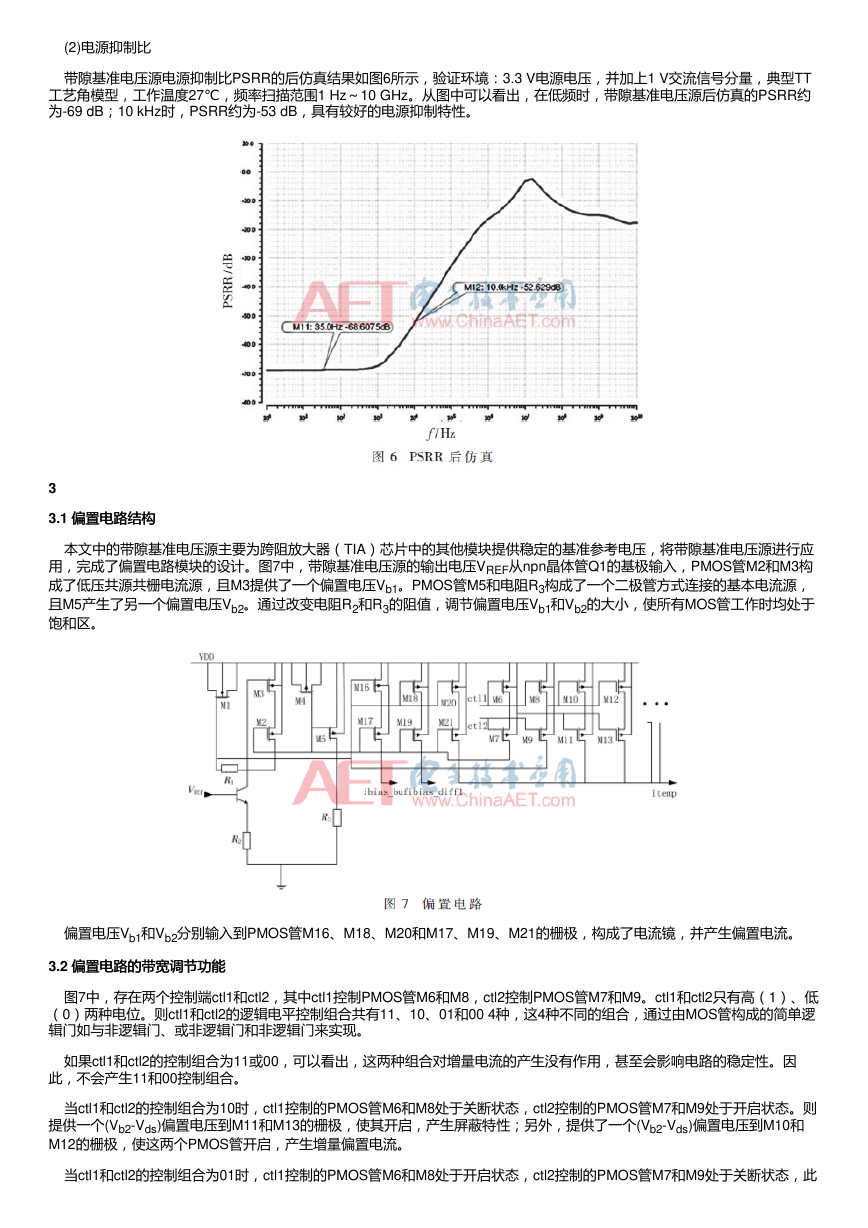

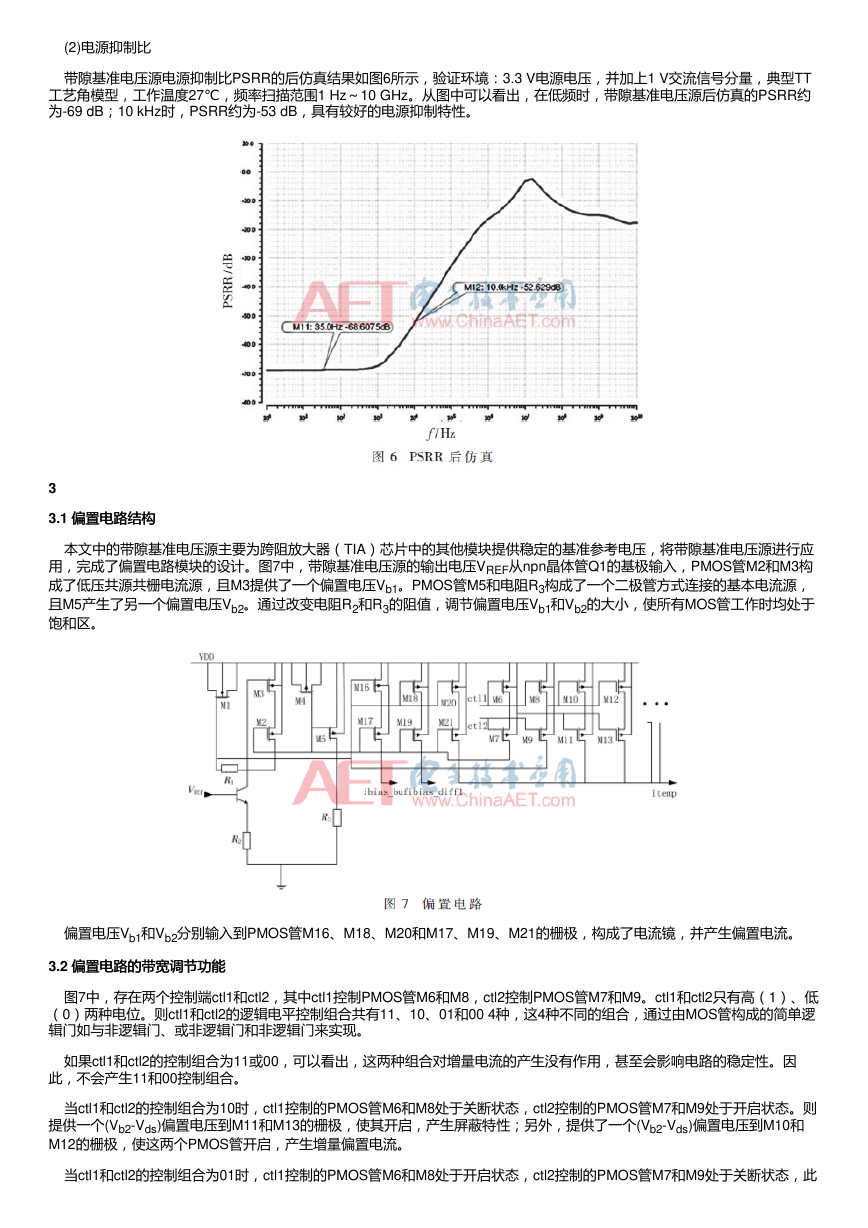

(2)电源抑制比

带隙基准电压源电源抑制比PSRR的后仿真结果如图6所示,验证环境:3.3 V电源电压,并加上1 V交流信号分量,典型TT

工艺角模型,工作温度27℃,频率扫描范围1 Hz~10 GHz。从图中可以看出,在低频时,带隙基准电压源后仿真的PSRR约

为-69 dB;10 kHz时,PSRR约为-53 dB,具有较好的电源抑制特性。

3

3.1 偏置电路结构

偏置电路结构

本文中的带隙基准电压源主要为跨阻放大器(TIA)芯片中的其他模块提供稳定的基准参考电压,将带隙基准电压源进行应

用,完成了偏置电路模块的设计。图7中,带隙基准电压源的输出电压VREF从npn晶体管Q1的基极输入,PMOS管M2和M3构

成了低压共源共栅电流源,且M3提供了一个偏置电压Vb1。PMOS管M5和电阻R3构成了一个二极管方式连接的基本电流源,

且M5产生了另一个偏置电压Vb2。通过改变电阻R2和R3的阻值,调节偏置电压Vb1和Vb2的大小,使所有MOS管工作时均处于

饱和区。

偏置电压Vb1和Vb2分别输入到PMOS管M16、M18、M20和M17、M19、M21的栅极,构成了电流镜,并产生偏置电流。

3.2 偏置电路的带宽调节功能

偏置电路的带宽调节功能

图7中,存在两个控制端ctl1和ctl2,其中ctl1控制PMOS管M6和M8,ctl2控制PMOS管M7和M9。ctl1和ctl2只有高(1)、低

(0)两种电位。则ctl1和ctl2的逻辑电平控制组合共有11、10、01和00 4种,这4种不同的组合,通过由MOS管构成的简单逻

辑门如与非逻辑门、或非逻辑门和非逻辑门来实现。

如果ctl1和ctl2的控制组合为11或00,可以看出,这两种组合对增量电流的产生没有作用,甚至会影响电路的稳定性。因

此,不会产生11和00控制组合。

当ctl1和ctl2的控制组合为10时,ctl1控制的PMOS管M6和M8处于关断状态,ctl2控制的PMOS管M7和M9处于开启状态。则

提供一个(Vb2-Vds)偏置电压到M11和M13的栅极,使其开启,产生屏蔽特性;另外,提供了一个(Vb2-Vds)偏置电压到M10和

M12的栅极,使这两个PMOS管开启,产生增量偏置电流。

当ctl1和ctl2的控制组合为01时,ctl1控制的PMOS管M6和M8处于开启状态,ctl2控制的PMOS管M7和M9处于关断状态,此

�

时M7和M9承担隔离电压Vb1和Vb2的作用。那么,M8的漏极与M9的源极间电位为1,使得M10和M12处于关断状态;此

外,M6的漏极与M7的源极间电位也为1,使得M11和M13也处于关断状态,则无增量偏置电流产生。

实际电路中,有多个这样的可控电流模块并列,通过对不同可控电流模块分别提供不同的控制组合,可以实现不同个数的

可控偏置电流的叠加。则需要全局控制逻辑对其进行控制,如图8所示,引入了逻辑信号bwh_ctl和bwl_ctl,共有4种逻辑电平

控制组合:11、10、01和00。则可以对TIA的输出信号的带宽实现4档调节,经过多次验证,4档调节满足需求。

3.3 版图及后仿真

版图及后仿真

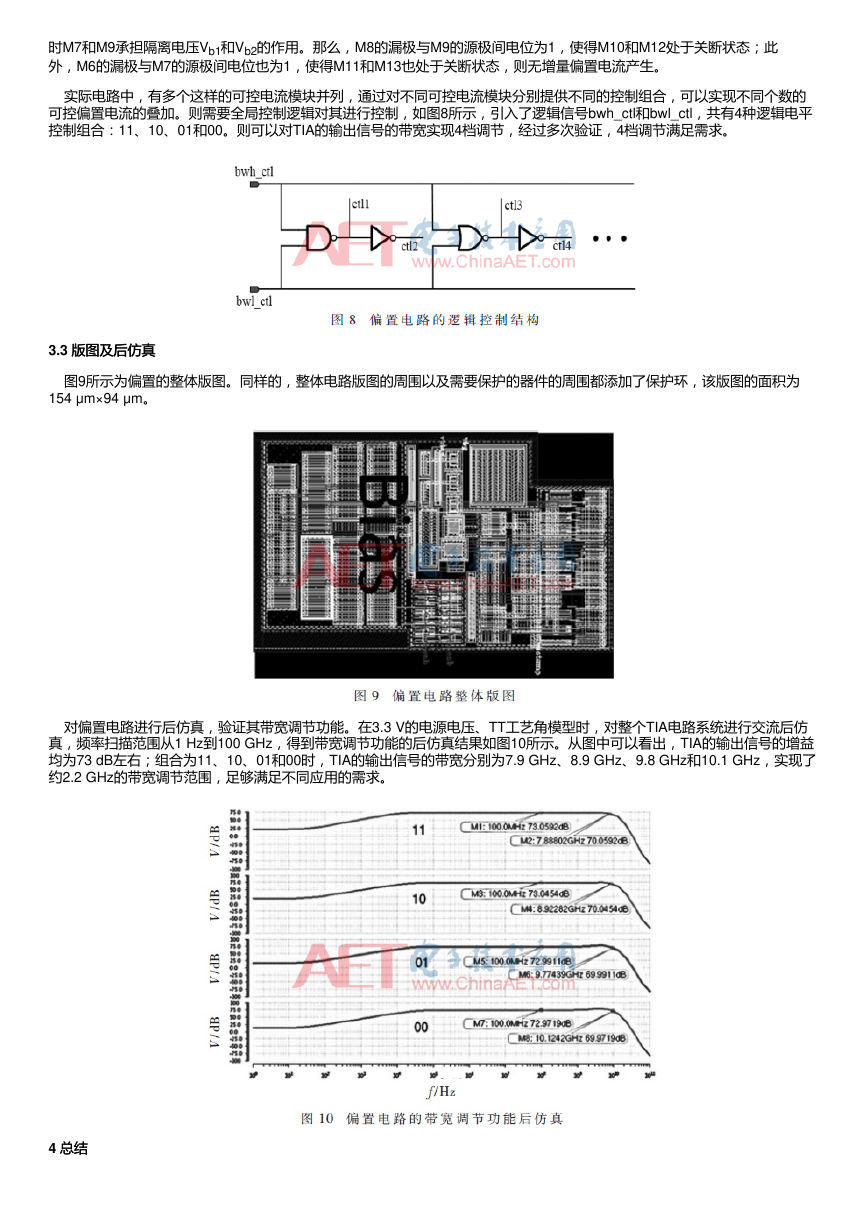

图9所示为偏置的整体版图。同样的,整体电路版图的周围以及需要保护的器件的周围都添加了保护环,该版图的面积为

154 μm×94 μm。

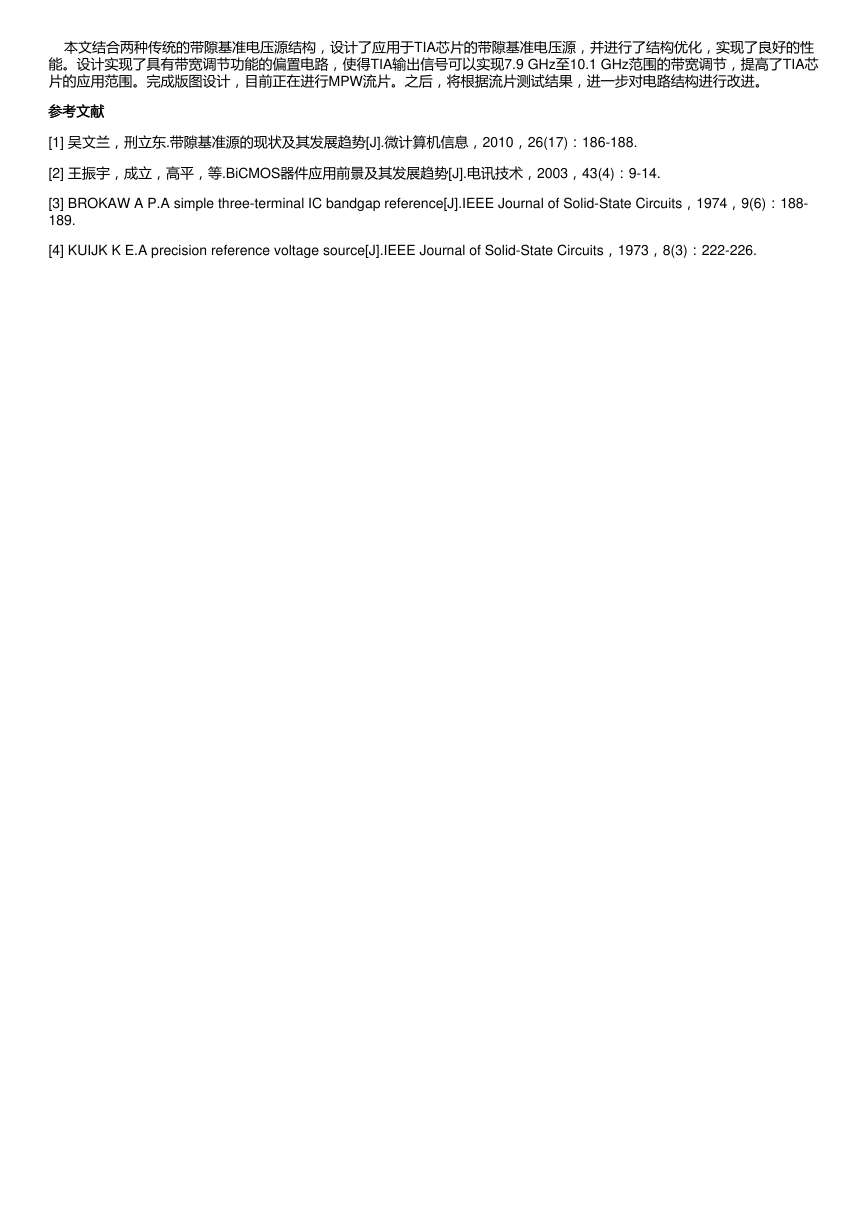

对偏置电路进行后仿真,验证其带宽调节功能。在3.3 V的电源电压、TT工艺角模型时,对整个TIA电路系统进行交流后仿

真,频率扫描范围从1 Hz到100 GHz,得到带宽调节功能的后仿真结果如图10所示。从图中可以看出,TIA的输出信号的增益

均为73 dB左右;组合为11、10、01和00时,TIA的输出信号的带宽分别为7.9 GHz、8.9 GHz、9.8 GHz和10.1 GHz,实现了

约2.2 GHz的带宽调节范围,足够满足不同应用的需求。

4 总结总结

�

本文结合两种传统的带隙基准电压源结构,设计了应用于TIA芯片的带隙基准电压源,并进行了结构优化,实现了良好的性

能。设计实现了具有带宽调节功能的偏置电路,使得TIA输出信号可以实现7.9 GHz至10.1 GHz范围的带宽调节,提高了TIA芯

片的应用范围。完成版图设计,目前正在进行MPW流片。之后,将根据流片测试结果,进一步对电路结构进行改进。

参考文献

参考文献

[1] 吴文兰,刑立东.带隙基准源的现状及其发展趋势[J].微计算机信息,2010,26(17):186-188.

[2] 王振宇,成立,高平,等.BiCMOS器件应用前景及其发展趋势[J].电讯技术,2003,43(4):9-14.

[3] BROKAW A P.A simple three-terminal IC bandgap reference[J].IEEE Journal of Solid-State Circuits,1974,9(6):188-

189.

[4] KUIJK K E.A precision reference voltage source[J].IEEE Journal of Solid-State Circuits,1973,8(3):222-226.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc