第 18 卷第 4 期

1997 年 8 月

半 导 体 光 电

Semiconductor Optoelectronics

Vol. 18 No. 4

Aug. 1997

CCD 驱动电路设计的新方法 ①

刘光昌 陈 欣 黄 亮

(暨南大学 ,广州 510632)

摘 要 : 本文详述了以往设计 CCD 驱动电路的三种方案 ,分析了各自的优缺

点 ,并提出了一种新的设计方法 。采用这种设计方法 ,电路简单 ,易实现 。给出了用

这种方法对 TCD1200D 驱动电路的具体设计实例 。

关键词 : 电荷耦合器件 驱动电路 单片机 可编程门阵列

中图法分类号 : TN786 ; TP368. 1

A ne w method for design of CCD driving circuit

L IU Guangchang CHEN Xin HUAN G Liang

( Jinan University , Guangzhou 510632 ,CHN)

Abstract :Three schemes for previous design of CCD driving circuit are discussed in

detail ,followed by analysis of their advantages and disadvantages. A new design method

with simple and easy implementation is proposed. A practical design of TCD1200D

driving circuit using this method is given as an example.

Keywords :CCD ,Driving Circuit ,Monolithic Microcomputer , GAL

1 引言

着 CCD 器件的进一步推广 ,同时也激起了不

少科技工作者的研究热情 。

CCD 由于其高精度 、高分辨率 、性能稳

定 、功耗低 、寿命长以及具有自扫描功能等特

点 ,已广泛用于摄像机 、复印机 、图文传真 、文

字 、图像识别 、自动精密测量等方面 。近十年

来 ,CCD 像感应器的各项性能指标越来越

高 ,价格大幅度下降 ,成为现代光电子学和现

代测试技术中最活跃 、最富有成果的新兴领

域之一 。

但是 ,由于 CCD 赖以正常工作的各驱动

信号的产生电路较复杂 ,其成品价格往往与

CCD 芯片的在同一个数量级 ,这极大地影响

①1996 - 11 - 15 收稿 ;1997 - 05 - 16 定稿

2 理论分析

从已发表的研究成果看 ,设计 CCD 驱动

电路大致有三种方法 :

CCD 产品说明书或经典著作 1 提供的

驱动电路图及早期实际使用的驱动电路几乎

全都是由普通数字电路芯片实现的 。它由主

振 、交迭脉冲产生 、分频 、译码以及驱动等部

分构成 。

CCD 芯片的早期产品 ,由于需要复杂的

三相或四相交迭脉冲 ,一般整个驱动电路需

20 个左右芯片 ,体积较大 、成本高 、设计也复

�

232 半 导 体 光 电 1997 年 8 月

杂 。

不少研究者仔细研究了 CCD 产品说明

书提供的典型波形和说明 ,在对 CCD 工作影

响不大的前提下 ,修改脉冲波形以简化电路

设计 ,仅在一定程度上减少了芯片数量 ,但这

往往需要相当高的专业知识 。

以便将“数据”填满 16 k 字节 ,每 16 k 之后自

动复位 ,但这样会拖长一行的扫描时间 。另

一种方法是加一些电路使一行数据正常结束

时即在 8 k 后的某个地址时强制复位 。

采用这种方案形成的驱动电路所需芯片

在 10 片左右 。

第二个方案是用 EPROM 来产生 CCD

第三 种 方 案 是 用 单 片 机 输 出 驱 动 波

所需波形 2 。

形 3 。

在 CCD 的一行周期中含有多个 (一般以

千计) 移位时钟 。在一个移位时钟中各路信

号在不同的时刻发生变化 ,设计者将移位时

钟周期划分成若干个等时间间隔 ,称为状态 ,

时钟波形电平变化发生在一定状态变化时

刻 ,这样一行就被分为上万个状态 ,各路信号

或 1 或 0 ,构成一个状态的数据 ,依次装到可

擦除只读存贮器 EPROM 中 ,只要等时间间

隔地依次输出这些数据就形成 CCD 所需的

各路波形 。

这一方案的设计思想十分显然 ,不论对

何种型号的 CCD ,其硬件结构几乎不需要变

化 。只需按 CCD 的典型驱动波形图 ,将 E

PROM 输出数据与 CCD 信号相对应 ,以及将

波形化成状态数据就可以了 ,设计起来十分

简单 。

这种设计方法所需 EPROM 一般在 16 k

字节或以上 。由主振电路经计数器形成地址

信号 送 给 EPROM , 其 数 据 输 出 经 驱 动 送

CCD 对应管脚 。

电路中比较复杂 ,需要考虑的主要有两

点 : (1) 因为 EPROM 需地址信号 14 位或以

上 ,不存在这么多位的同步计数器 ,如果用多

片同步计数器串联 ,也就不会同步了 ;如用异

步计数器 ,由于各位地址信号之间会有延迟

从而使得 EPROM 输出数据有“毛刺”。这要

在计数器与 EPROM 地址脚间加电路以使地

址信号同时到达 EPROM 或者在 EPROM 数

据脚后加锁存器 ,使得只有地址稳定后才锁

存输出数据 ; (2) 假定某 CCD 一行的状态数

只略大于 8 k ,设计上要使用 16 k 存贮器 。

一种方法是人为地增加一行中的移位周期数

由于绝大多数 CCD 应用系统都含有单

片机 ,这使有关 CCD 应用系统开发者十分自

然地考虑用单片机的并行锁存输出口输出所

需的驱动脉冲信号 ,再经驱动芯片接到 CCD

对应管脚上 。

这一方案与 EPROM 方案有些相似 , E

PROM 方案每改变地址就输出新的状态数

据 ,而此方案是用单片机的口输出指令改变

输出数据 。

这一方案的电路极其简单 ,只需单片机

加驱动芯片 ,而且只是部分地占用了单片机

的硬 、软件资源 ,单片机同时还用于应用系统

的其它工作 。

但是 ,这种方法产生的移位脉冲频率一

般难以超过 200 kHz。例如假定所使用单片

机机器周期为 1μs ,且假定一个移位周期含

8 个状态 ,那么即使是全部采用单机器周期

改变口输出数据 ,移位脉冲频率也只能达到

125 kHz。

此外 ,由于一个状态变到另一个状态往

往不只一位信号变化 ,即是说不能只用 CL R

或 SET 等 位 操 作 指 令 , 而 还 要 采 用 INC ,

DEC 等能引起两位或更多位变化的指令 ,这

就需要精心安排单片机输出的哪一位对应哪

一路驱动信号 ,甚至在单片机输出位间插上

无效输出位 (即该位信号不送往任何 CCD 管

脚) ,然后再合理选用有关指令 ,特别是需要

充分使用单片机的单机器周期的口输出指

令 。这样在设计上显然比 EPROM 方案要复

杂 。

这一方案对于 CCD 的一些简单应用系

统可能是适合的 。但是 ,单片机花在形成驱

�

第 18 卷第 4 期 刘光昌等 : CCD 驱动电路设计的新方法

332

动波形上是“太累了”,单片机执行的指令大

部分是用于产生这些驱动波形 ,只在两行间

过渡段对各路输出冻结一段时间 ,赶忙做点

对 CCD 视频输出进行处理等工作 。

近年来 ,新型号的 CCD 芯片不断涌现 ,

像元数增多 ,驱动脉冲频率增高 ,性能越来越

好 ;大多数在片内还集成了交迭脉冲发生电

路 ,片外驱动也只需 TTL 电平 ,给 CCD 驱动

器的设计和制作带来了很大方便 。例如天津

大学为新一代的线阵芯片 TCD1200D 设计

的驱动电路由一只晶振及五个数字芯片构

成 。

在这种情况下 ,前述第三种方案由于所

形成的移位频率不可能太高而不适于频率较

高的新 CCD 芯片 ;而第二种方案 ,除了保留

设计简单的优点外 ,由于新型芯片像元数多 ,

需要大容量的 EPROM ,其电路的芯片数 、体

积 、耗电 、成本等都没有什么吸引人之处了 。

天津大学只用几只数字电路芯片就形成

了一个实用的 CCD 驱动电路 ,他们是在对厂

家提供的典型波形作了一些修改 (特别是

FSH信号) 后实现的 , 这需要相当的专业知

识 。当然 ,这已经够使人们振奋的了 ,我们仔

细观察 、研究了天津大学的电路及其波形 ,设

计的难点主要是 FSH ,于是一种新的设计思

路产生了 : 用可编程器件形成 CCD 所需的

F1 , F2 , FR 等周期性脉冲信号 ,而每当一行

结束时由单片机送出 FSH信号 ,这样可大大

简化驱动电路的设计 。

3 实验

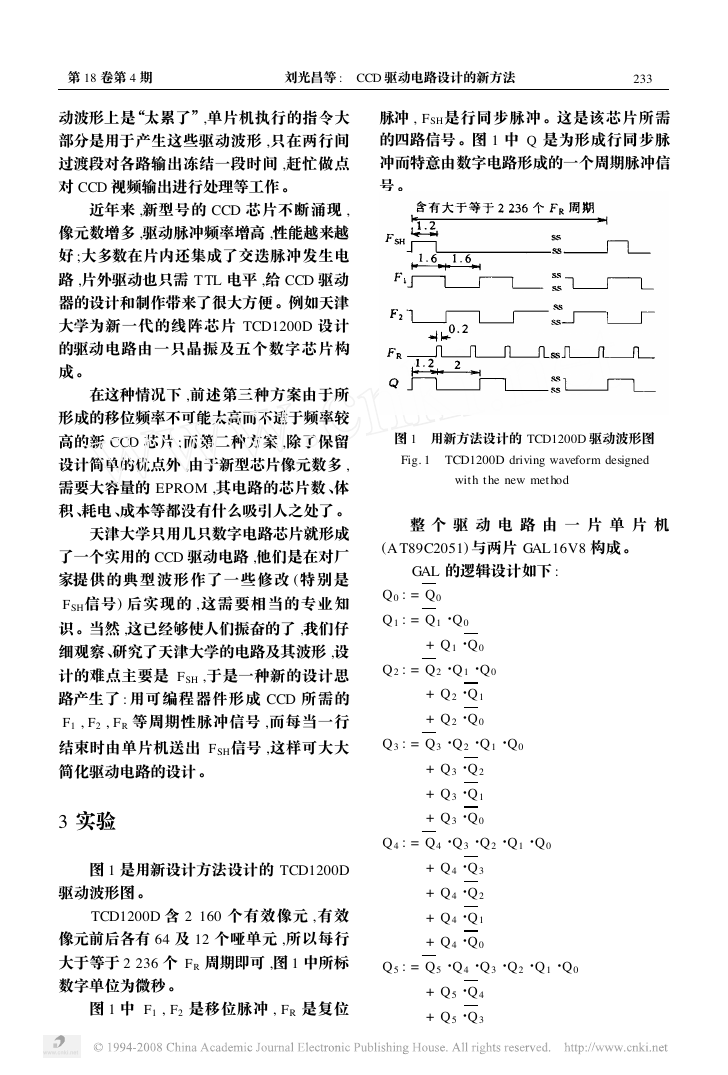

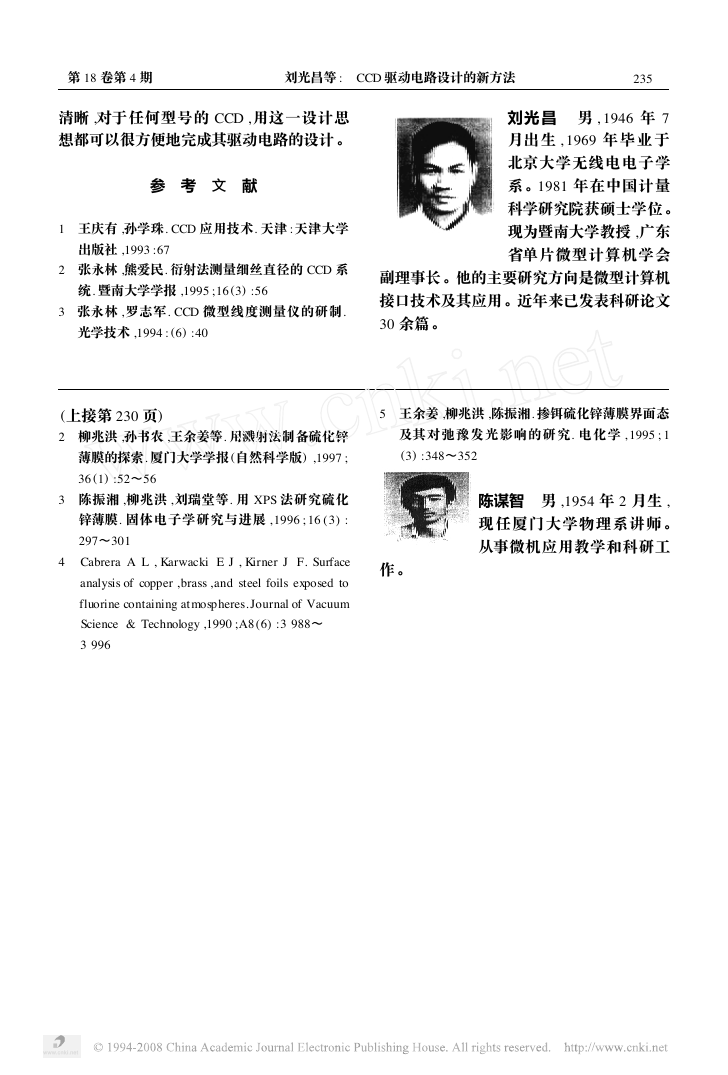

图 1 是用新设计方法设计的 TCD1200D

驱动波形图 。

TCD1200D 含 2 160 个有效像元 ,有效

像元前后各有 64 及 12 个哑单元 ,所以每行

大于等于 2 236 个 FR 周期即可 ,图 1 中所标

数字单位为微秒 。

图 1 中 F1 , F2 是移位脉冲 , FR 是复位

脉冲 , FSH是行同步脉冲 。这是该芯片所需

的四路信号 。图 1 中 Q 是为形成行同步脉

冲而特意由数字电路形成的一个周期脉冲信

号 。

图 1 用新方法设计的 TCD1200D 驱动波形图

Fig. 1 TCD1200D driving waveform designed

with the new method

整 个 驱 动 电 路 由 一 片 单 片 机

(A T89C2051) 与两片 GAL16V8 构成 。

GAL 的逻辑设计如下 :

Q 0 : = Q 0

Q 1 : = Q 1·Q 0

+ Q 1·Q 0

Q 2 : = Q 2·Q 1·Q 0

+ Q 2·Q 1

+ Q 2·Q 0

Q 3 : = Q 3·Q 2·Q 1·Q 0

+ Q 3·Q 2

+ Q 3·Q 1

+ Q 3·Q 0

Q 4 : = Q 4·Q 3·Q 2·Q 1·Q 0

+ Q 4·Q 3

+ Q 4·Q 2

+ Q 4·Q 1

+ Q 4·Q 0

Q 5 : = Q 5·Q 4·Q 3·Q 2·Q 1·Q 0

+ Q 5·Q 4

+ Q 5·Q 3

�

432 半 导 体 光 电 1997 年 8 月

+ Q 5·Q 2

+ Q 5·Q 1

+ Q 5·Q 0

F2 = Q 5

FR = Q 4·Q 3·Q 2

Q = Q 5·Q 4 + Q 5·Q 3

FSH = P·Q

式中 ,·表示与 , + 表示或 , - 表示非 。

单片机使用 的晶振为 20 M Hz ,由于单

片机 内 含 振 荡 电 路 , 所 以 它 可 以 输 出 20

M Hz 的信号 ,用作 GAL 的 CL K。

Q 0 , Q 1 , …Q 5 分别为其 2 频 ,4 分频 …

64 分频信号 。Q 5 即为 F1 ,其反相得到 F2 。

TCD1200D 产品说明书对驱动波形设计说明

中要求 (下称“设计要求”) 移位脉冲 F1 和 F2

互为相反 ,最高工作频率为 1 M Hz ,典型值

为 500 kHz ,现约为 310 kHz ,在正常工作范

围内 。

设计要求 FR 脉宽最小值 40 ns ,典型值

为 250 ns ;还要求其下降沿要在 F1 或 F2 的

下降沿之前至少 100 ns ,典型值为 125 ns ;现

这两个值均为 200 ns ,满足要求 。

Q 是一个频率与 F1 相同 ,其高低电平

各为 1. 2μs ,2μs 的周期信号 。 FSH是每隔大

于等于 2 236 个 FR 周期取一个 Q 的正脉冲

形成的 。

在每一行完成 (即上一帧 FSH后经历大

于等于 2 236 个 FR 周期) 时 ,由单片机查询

到 Q 为高电平就输出一个 3μs 宽的正脉冲

信号 (即逻辑式中的 P) ,它与 Q 信号相与就

得到 FSH 。

假定 Q 信号送往单片机 P1. 7 ,而 P 信

号从单片机 P3. 7 输出 ,则单片机输出 P 部

分的编程如下 :

J NB P1. 7 , $; Q 不为高电平时再重复

查询

SETB P3. 7 ;输出 P 高电平

NOP ;延时 0. 6μs

NOP ;延时 0. 6μs

NOP ;延时 0. 6μs

NOP ;延时 0. 6μs

CL R P3. 7 ;输出 P 低电平

单片机使用 20 M Hz 时钟 ,一个机器周

期 0. 6μs ,单片机查询到 Q 为高电平的时刻

到实际输出 P 高电平的时刻需两个机器周

期即 1. 2μs ,由于 Q 的高电平宽度只有 1. 2

μs ,故可知 P 信号的前沿一定在 Q 为低电平

的状态 ,且 P 信号 (3μs 宽) 正好包容一个 Q

的高电平状态 , P·Q 就恰为一个 Q 正脉冲 ,

这就是所形成的 FSH 。

设计要求 FSH必须被包容在 F1 之中 。

由于 FSH是 Q 5 (即 F1) 经一定逻辑关系才形

成的 ,所以其前沿一定滞后于 F1 ;而其后沿

(参见 Q 的后沿) 又超前 F1 的后沿约 0. 4

μs ,故满足要求 。

本设计中使用 GAL 芯片 ,其管脚可灵活

方便地定义 , 使电路紧凑 , 连线十分简单 。

GAL 还有足够的驱动能力 ,不需另加驱动芯

片便可驱动 CCD 。

单片机所用晶振及片内振荡电路被借用

于驱动波形形成电路 ,不需专门另用一套电

路 。而且驱动电路与单片机共用晶振 ,有同

步关系 ,对单片机的一些工作还会带来好处 。

这样的设计只用了三片芯片 ,而且 GAL

约有 3/ 4 片富余 ,可用于应用系统中其他的

数字电路 ;该驱动电路对单片机在硬件上只

占用 2 位信号线 ,软件上在每一帧 (毫秒量

级) 只占用几条指令 (微秒量级) 的工作 ,可谓

是单片机“附带”就完成了驱动 CCD 所需的

工作 。

4 结论

这一设计已用于高精度测量系统中 ,装

置十分紧凑 、微型化 ,已用于广东省高校开放

性教学提高型重点实验室中作为现代化光电

子技术的一个实验 ,供本科高年级学生或研

究生及其他高校教师学习 。

这种设计方法简单 、灵活 、设计思想十分

�

第 18 卷第 4 期 刘光昌等 : CCD 驱动电路设计的新方法

532

清晰 ,对于任何型号的 CCD ,用这一设计思

想都可以很方便地完成其驱动电路的设计 。

参 考 文 献

1 王庆有 ,孙学珠. CCD 应用技术. 天津 :天津大学

出版社 ,1993 :67

2 张永林 ,熊爱民. 衍射法测量细丝直径的 CCD 系

统. 暨南大学学报 ,1995 ;16 (3) :56

3 张永林 ,罗志军. CCD 微型线度测量仪的研制.

光学技术 ,1994 : (6) :40

刘光 昌 男 , 1946 年 7

月出 生 , 1969 年 毕 业 于

北京大学无线电电子学

系 。1981 年在中国计量

科学研究院获硕士学位 。

现为暨南大学教授 ,广东

省单片微型计算机学会

副理事长 。他的主要研究方向是微型计算机

接口技术及其应用 。近年来已发表科研论文

30 余篇 。

(上接第 230 页)

2 柳兆洪 ,孙书农 ,王余姜等. 用溅射法制备硫化锌

薄膜的探索. 厦门大学学报 (自然科学版) ,1997 ;

36 (1) :52~56

3 陈振湘 ,柳兆洪 ,刘瑞堂等. 用 XPS 法研究硫化

锌薄膜. 固体电子学研究与进展 ,1996 ; 16 (3) :

297~301

4 Cabrera A L , Karwacki E J , Kirner J F. Surface

analysis of copper ,brass ,and steel foils exposed to

fluorine containing atmospheres. Journal of Vacuum

Science & Technology ,1990 ;A8 (6) :3 988~

3 996

5 王余姜 ,柳兆洪 ,陈振湘. 掺铒硫化锌薄膜界面态

及其对弛豫发光影响的研究. 电化学 , 1995 ; 1

(3) :348~352

陈谋智 男 ,1954 年 2 月生 ,

现任厦门大学物理系讲师 。

从事微机应用教学和科研工

作 。

�