SD Host Controller Specification

1. GENERAL DESCRIPTION ........................................................................................................3

2.

3.

4.

5.

FEATURES ...................................................................................................................................3

PIN CONFIGURATIONS............................................................................................................4

PIN DESCRIPTIONS...................................................................................................................4

BLOCK DIAGRAM .....................................................................................................................4

5.1. 系统框图 5.1-1......................................................................................................................5

5.2. 引脚信号说明表 5.2-1..........................................................................................................5

6. REGSTERS ...................................................................................................................................6

6.1.

6.2.

REGISTER MAP.......................................................................................................................6

HOST CONTROLLER内部寄存器描述....................................................................................7

6.2.1. 配置寄存器类型说明......................................................................................................8

6.2.2.

SD Host Standard Register ...............................................................................................8

7.

SUB MODULER IMPLEMENT...............................................................................................64

7.1.

7.2.

7.3.

7.4.

7.5.

7.6.

CPU BUS INTERFACE ...........................................................................................................64

PRESCALER ..........................................................................................................................69

FIFO(DATA BUFFER) ......................................................................................................70

STANDARD REGISTERS .........................................................................................................72

COMMAND CONTROL...........................................................................................................73

DATA CONTROL....................................................................................................................75

1

�

1. Contents

1. Contents

2. Block Diagram

3. Inputs

4. Outputs

5. Bidirectional

6. Operation

7. Register Definitions

1. Register 1

2. Register 2

Inputs

________________________________________

2. Block Diagram

3.

4. Outputs

5. Operation

2

�

Revision History

No.

Version Dates

Pages 说明

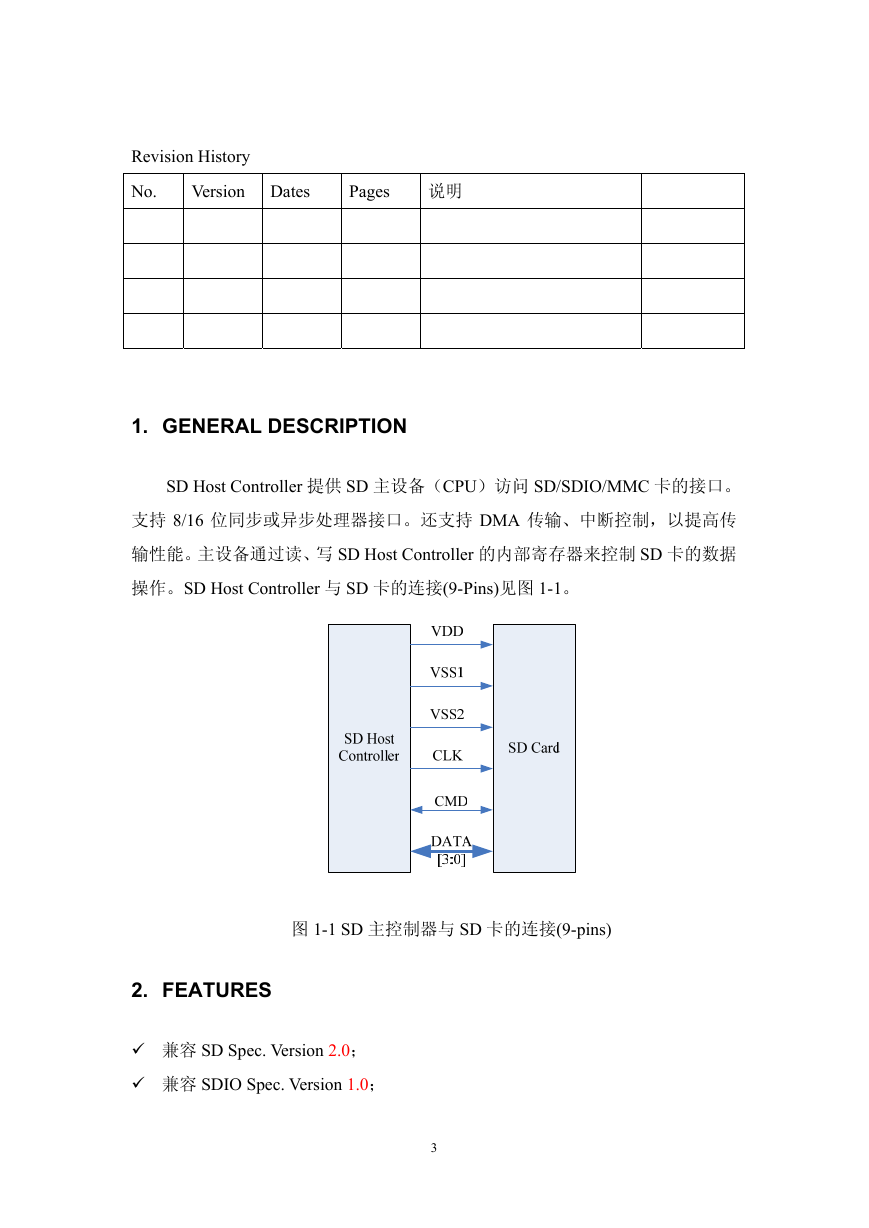

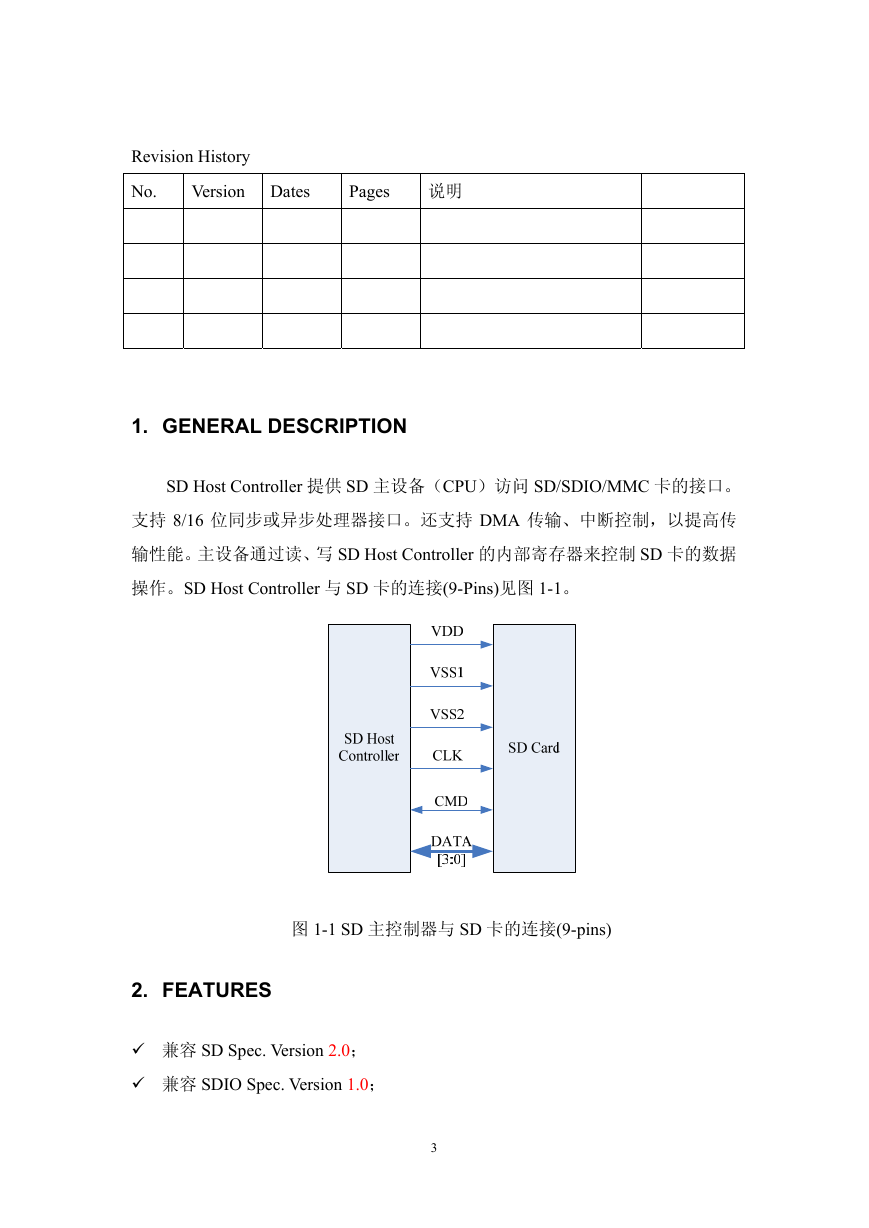

1. GENERAL DESCRIPTION

SD Host Controller 提供 SD 主设备(CPU)访问 SD/SDIO/MMC 卡的接口。

支持 8/16 位同步或异步处理器接口。还支持 DMA 传输、中断控制,以提高传

输性能。主设备通过读、写 SD Host Controller 的内部寄存器来控制 SD 卡的数据

操作。SD Host Controller 与 SD 卡的连接(9-Pins)见图 1-1。

图 1-1 SD 主控制器与 SD 卡的连接(9-pins)

2. FEATURES

兼容 SD Spec. Version 2.0;

兼容 SDIO Spec. Version 1.0;

3

�

兼容 MMC Spec. Version 4.0;

支持 SD、MMC、SPI 模式;

支持 SDIO 中断和挂起、恢复操作;

内置 512 字节 FIFO 用于读、写数据缓冲;

支持同步、异步处理器接口;

支持 AMBA AHB SLAVE,Generic #1,Generic #2;

支持 DMA 和中断传输模式;

支持 32 Bit 数据总线的处理器接口;

Operation Voltage:2.7~3.6v for SD/SDIO/MMC,2.5/3.3v for CPU;

40-bit Command Register;

136-bit Response Register;

CRC7 & CRC16;

8-bit Prescaler Logic;

3. PIN CONFIGURATIONS

4. PIN DESCRIPTIONS

5. BLOCK DIAGRAM

4

�

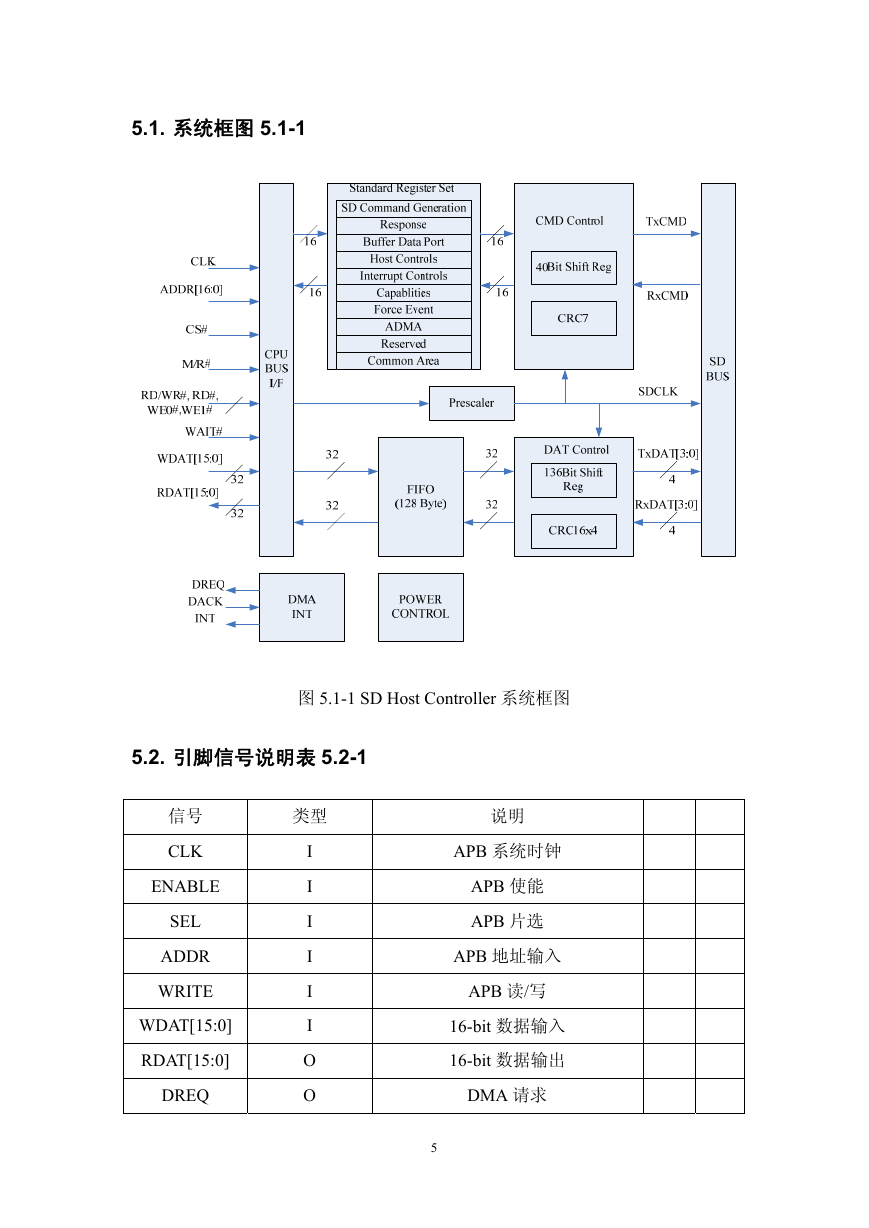

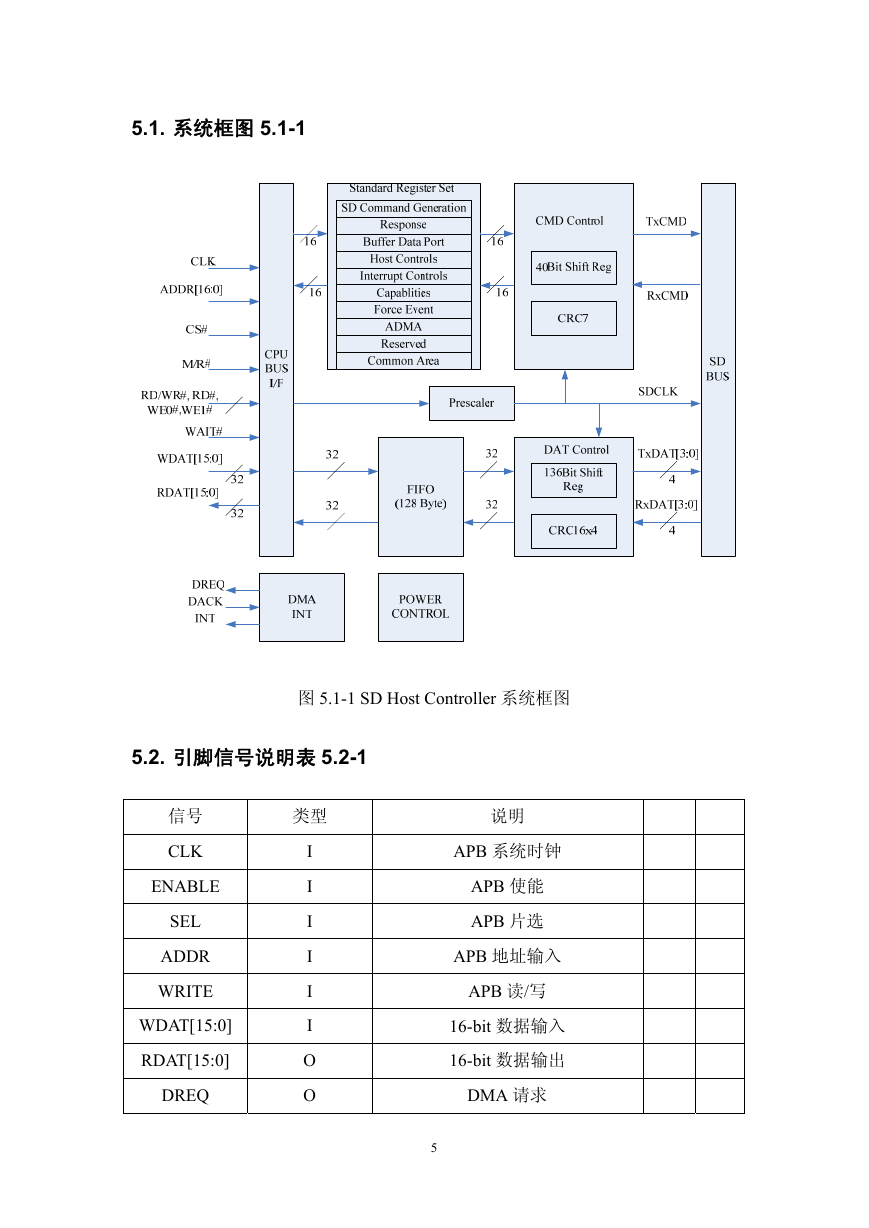

5.1. 系统框图 5.1-1

图 5.1-1 SD Host Controller 系统框图

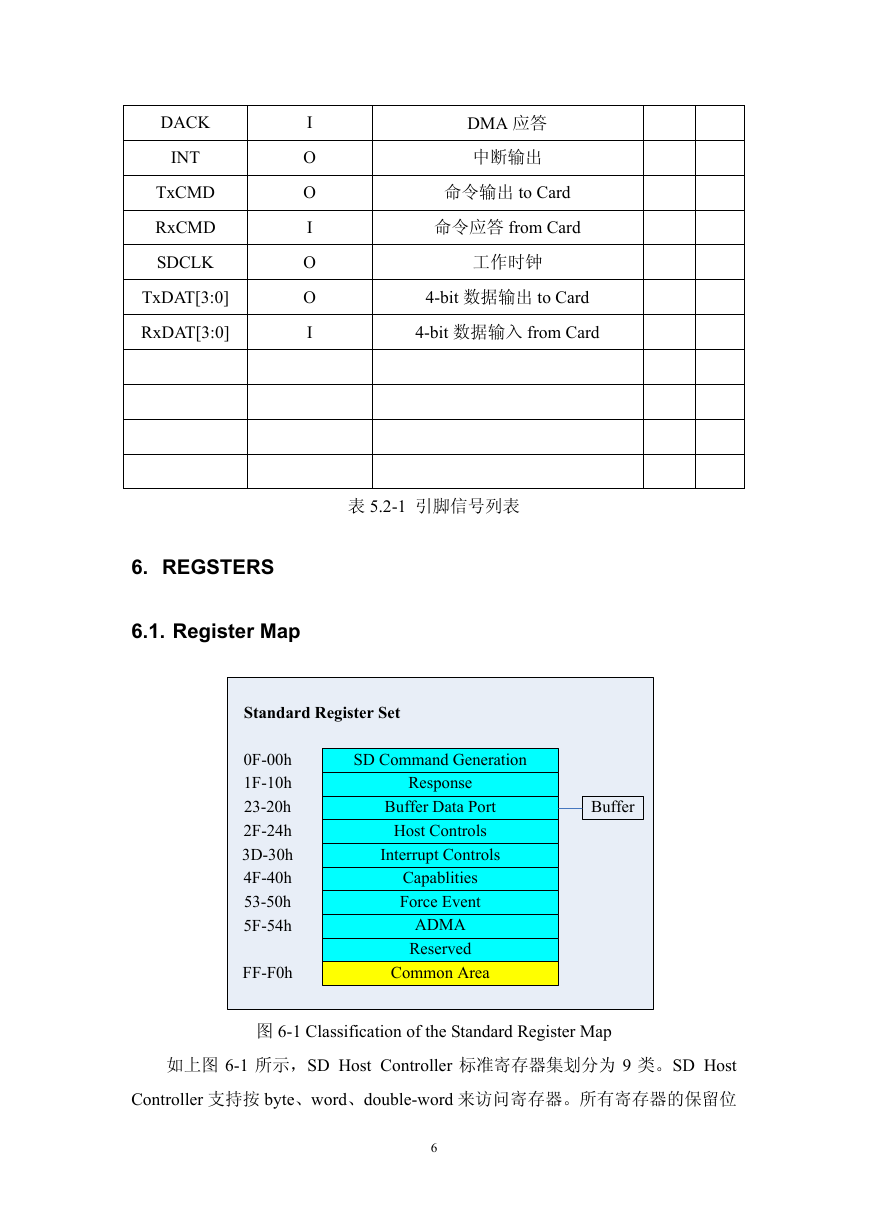

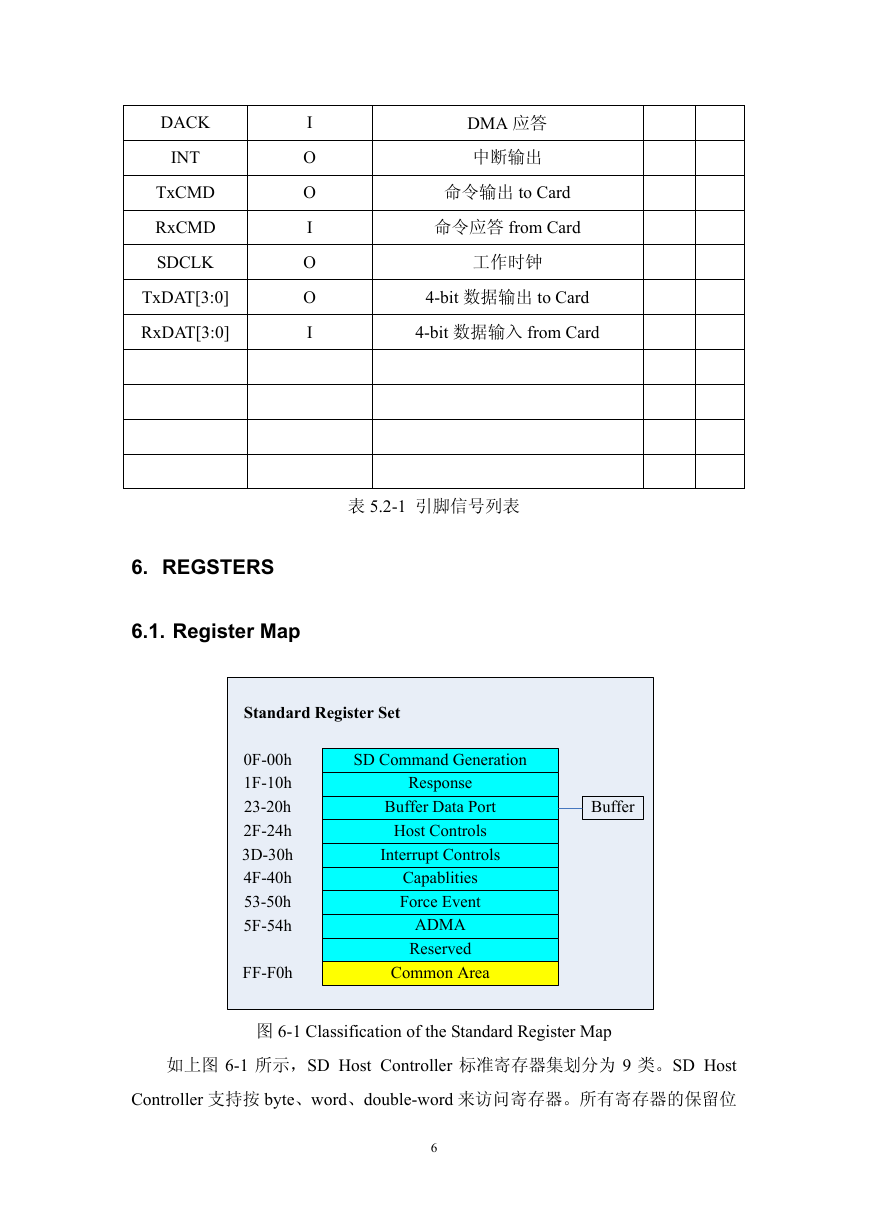

5.2. 引脚信号说明表 5.2-1

信号

CLK

ENABLE

SEL

ADDR

WRITE

WDAT[15:0]

RDAT[15:0]

DREQ

类型

I

I

I

I

I

I

O

O

5

说明

APB 系统时钟

APB 使能

APB 片选

APB 地址输入

APB 读/写

16-bit 数据输入

16-bit 数据输出

DMA 请求

�

DMA 应答

中断输出

命令输出 to Card

命令应答 from Card

工作时钟

4-bit 数据输出 to Card

4-bit 数据输入 from Card

表 5.2-1 引脚信号列表

DACK

INT

TxCMD

RxCMD

SDCLK

TxDAT[3:0]

RxDAT[3:0]

I

O

O

I

O

O

I

6. REGSTERS

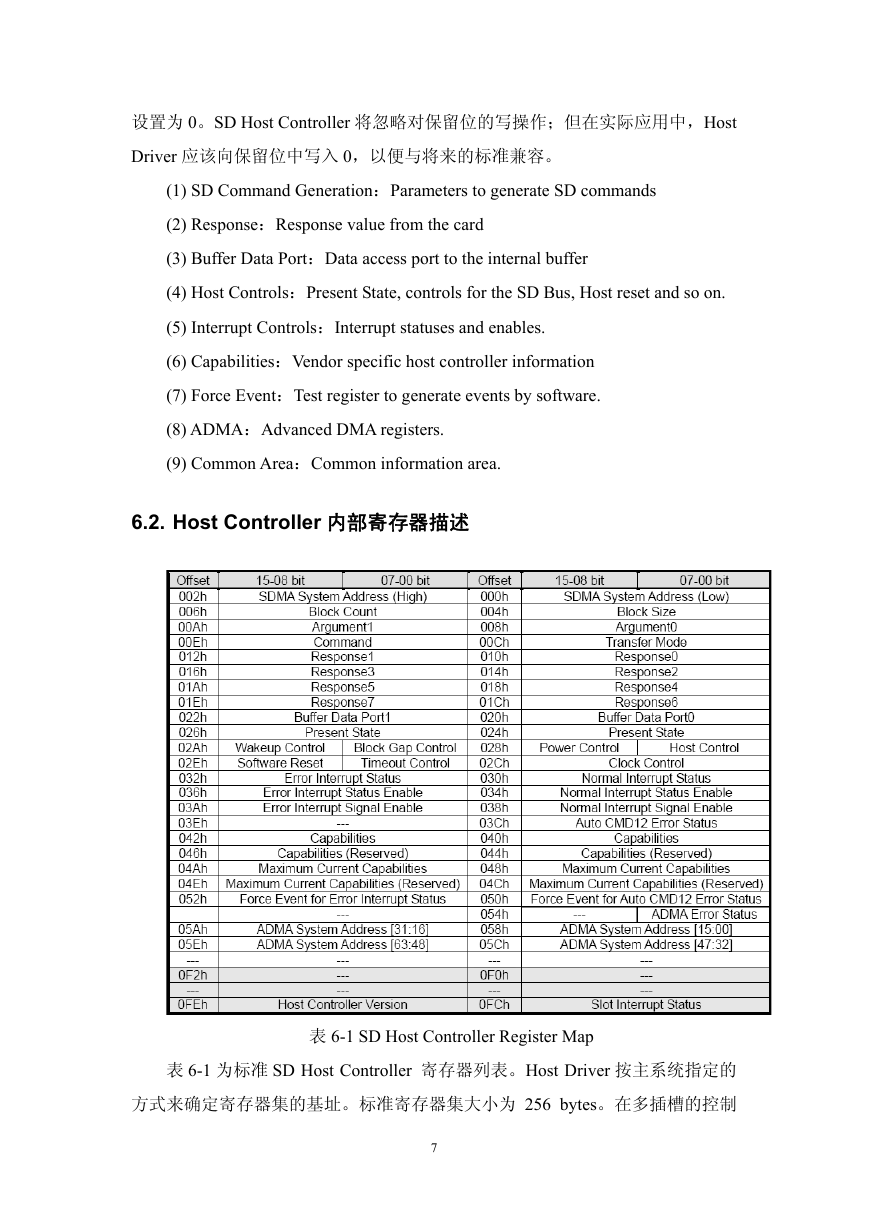

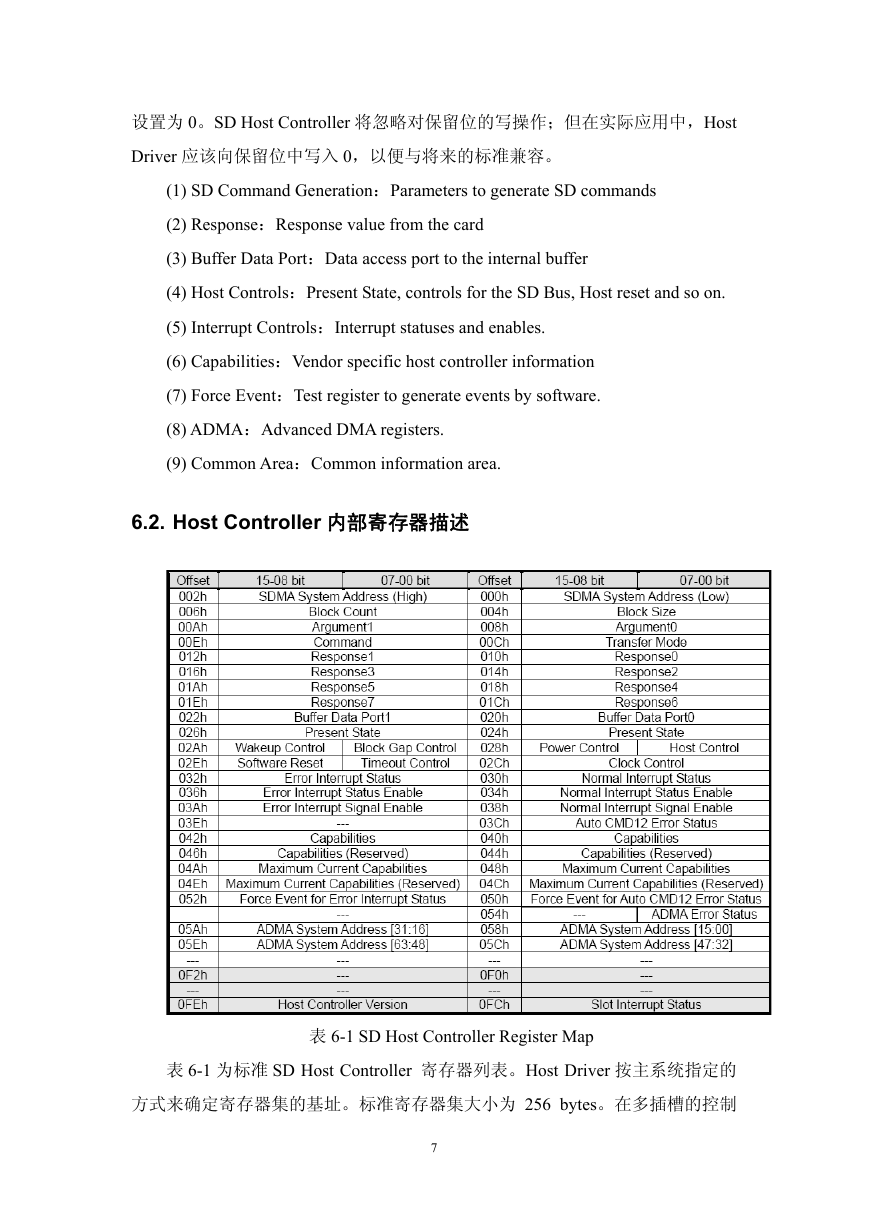

6.1. Register Map

Standard Register Set

0F-00h

1F-10h

23-20h

2F-24h

3D-30h

4F-40h

53-50h

5F-54h

FF-F0h

SD Command Generation

Response

Buffer Data Port

Host Controls

Interrupt Controls

Capablities

Force Event

ADMA

Reserved

Common Area

Buffer

图 6-1 Classification of the Standard Register Map

如上图 6-1 所示,SD Host Controller 标准寄存器集划分为 9 类。SD Host

Controller 支持按 byte、word、double-word 来访问寄存器。所有寄存器的保留位

6

�

设置为 0。SD Host Controller 将忽略对保留位的写操作;但在实际应用中,Host

Driver 应该向保留位中写入 0,以便与将来的标准兼容。

(1) SD Command Generation:Parameters to generate SD commands

(2) Response:Response value from the card

(3) Buffer Data Port:Data access port to the internal buffer

(4) Host Controls:Present State, controls for the SD Bus, Host reset and so on.

(5) Interrupt Controls:Interrupt statuses and enables.

(6) Capabilities:Vendor specific host controller information

(7) Force Event:Test register to generate events by software.

(8) ADMA:Advanced DMA registers.

(9) Common Area:Common information area.

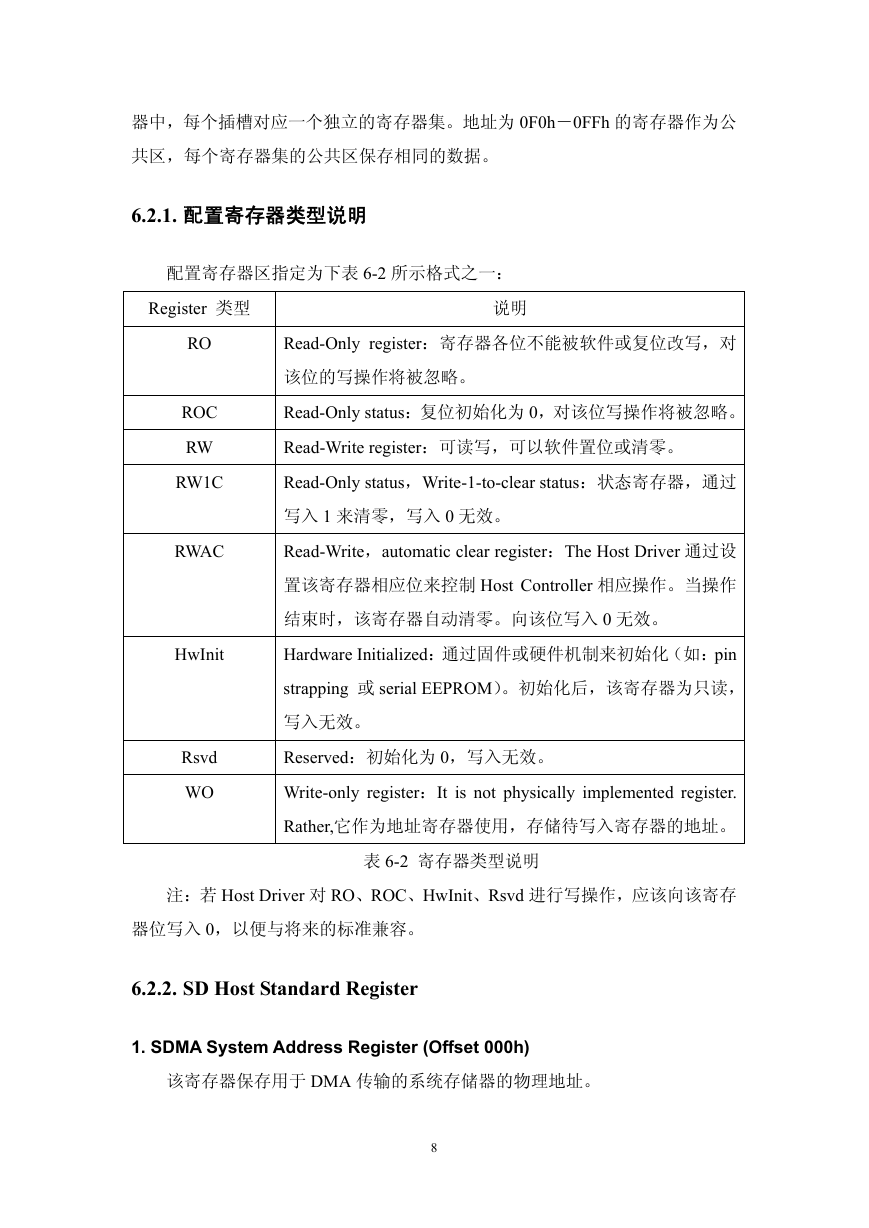

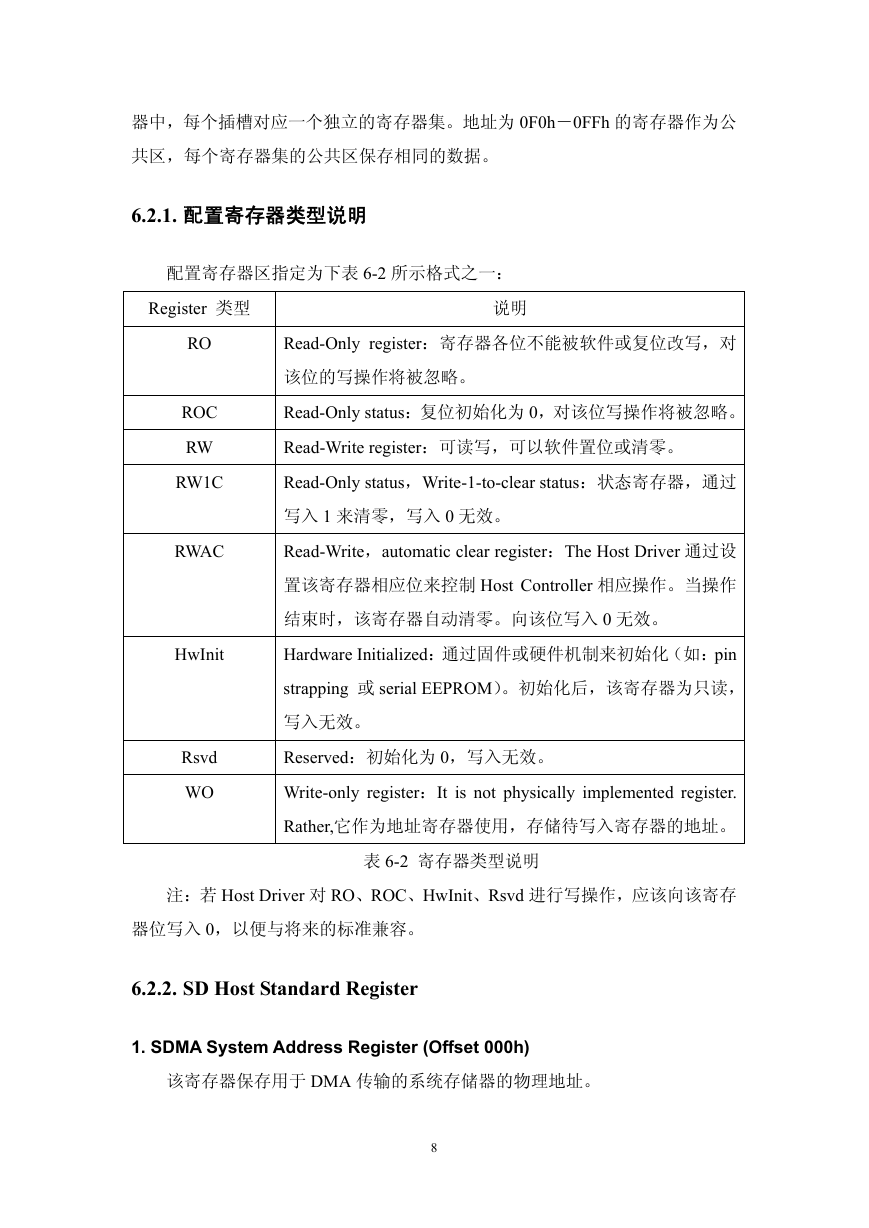

6.2. Host Controller 内部寄存器描述

表 6-1 SD Host Controller Register Map

表 6-1 为标准 SD Host Controller 寄存器列表。Host Driver 按主系统指定的

方式来确定寄存器集的基址。标准寄存器集大小为 256 bytes。在多插槽的控制

7

�

器中,每个插槽对应一个独立的寄存器集。地址为 0F0h-0FFh 的寄存器作为公

共区,每个寄存器集的公共区保存相同的数据。

6.2.1. 配置寄存器类型说明

配置寄存器区指定为下表 6-2 所示格式之一:

Register 类型

RO

ROC

RW

RW1C

RWAC

HwInit

Rsvd

WO

说明

Read-Only register:寄存器各位不能被软件或复位改写,对

该位的写操作将被忽略。

Read-Only status:复位初始化为 0,对该位写操作将被忽略。

Read-Write register:可读写,可以软件置位或清零。

Read-Only status,Write-1-to-clear status:状态寄存器,通过

写入 1 来清零,写入 0 无效。

Read-Write,automatic clear register:The Host Driver 通过设

置该寄存器相应位来控制 Host Controller 相应操作。当操作

结束时,该寄存器自动清零。向该位写入 0 无效。

Hardware Initialized:通过固件或硬件机制来初始化(如:pin

strapping 或 serial EEPROM)。初始化后,该寄存器为只读,

写入无效。

Reserved:初始化为 0,写入无效。

Write-only register:It is not physically implemented register.

Rather,它作为地址寄存器使用,存储待写入寄存器的地址。

表 6-2 寄存器类型说明

注:若 Host Driver 对 RO、ROC、HwInit、Rsvd 进行写操作,应该向该寄存

器位写入 0,以便与将来的标准兼容。

6.2.2. SD Host Standard Register

1. SDMA System Address Register (Offset 000h)

该寄存器保存用于 DMA 传输的系统存储器的物理地址。

8

�