�

2

2

嵌 入 式 技 术

田开坤等 :基于 CPLD 的单片机接口设计

基于 CPLD 的单片机接口设计

田开坤 ,徐海霞

(湖北师范学院 电工电子实验教学中心 湖北 黄石 435002)

摘 要 :现在分离元件在很多电路设计中还在普遍使用 ,完成逻辑转换 、地址译码 、数据锁存等任务 ,在 PLD 技术相当成

熟的今天 ,采用 PLD 代替传统分离元器件 ,将会极大地减小 PCB 尺寸 ,节约成本 。对 CPLD 器件和开发工具进行研究 ,提出

一种单片机与 CPLD 总线接口方案 。运用该方案设计单片机系统实现 A/ D ,D/ A ,L CD 等多种外设的接口 ,电路简洁 ,并给

出 CPLD 电路设计方案 ,总体电路原理图和关键程序代码 。

关键词 :CPLD ;分离元件 ; PLD ; EDA

中图分类号 : TP331. 1 文献标识码 :B 文章编号 :1004

373X(2008) 02

034

03

Design of Single Chip Computer Interface Based on CPLD

( Electrician and Electronics Experiment Center , Hubei Normal University , Huangshi ,435002 ,China)

TIAN Kaikun ,XU Haixia

Abstract :Many circuit design still use separative component s in nowadays ,completes the logic to transform ,the address

decoding ,the data lock saves and so on. Today the PLD technology has become more and more mature ,using the PLD technol

ogy instead of tradational separative component s not only reduce the PCB size ,but also save the co st. This paper researches

CPLD devices and the reference tools ,proposes a bus interface between single chip comp uter and CPLD. The single chip com

puter system contain A/ D ,D/ A ,L CD and something else ,adopting this way ,making the circuit more easy and clear. This pa

per also gives CPLD circuit design scheme ,circuit theory graphic and the main p rogram code.

Keywords :CPLD ;separative component s ; PLD ; EDA

1 引 言

2 CPLD 开发工具

随着 PLD( 可编程器件) 技术的成熟 ,应用越来越广

泛 。单片机系统中 ,例如 RAM ,A/ D ,D/ A ,L ED 等常需要

一些门电路作为接口 ,通常采用诸如 74 系列 、40 系列等分

离元件实现 ,往往电路庞大复杂 ,不便集成 。PLD 以可编

程特性受到设计者的青睐 , 成为 替 代分 离元 件 的最 佳

选择。

复杂可 编 程逻 辑 器 件 ( Complex Programable Logic

Device ,CPLD) ,其内部有大量的门电路 ,组合逻辑的功能

很强 ,能完成任何数字器件的功能 。高性能 CPU ,简单的

74 电路 ,都可以用 CPLD 实现。CPLD 如同一张白纸或是

一堆积木 ,工程师可以通过传统的原理图输入法 ,或是硬

件描述语言自由地设计一个数字系统 。用户可以反复编

程 、擦除 、使用或在外围电路连接不变的情况下用不同软

件实现不同的功能。

CPLD 基本都是由 E2 PROM 和 FL ASH 工艺制造 ,一

上电就可以工作 , 无需其他芯片配合 , 使用方便 , 容 易

设计。

收稿日期 :2007

08

03

43

CPLD 器件的设计与开发离不开 EDA 工具软件 ,现

在有很多支持 CPLD/ FP GA 设计的软件。

在众多的开发工具中 , Xilinx 的 ISE 软件是非常流行

的一种 。ISE 集成开发软件是 Xilinx 公司最新的 EDA 开

发 工 具 , 他 支 持 所 有 的 Xilinx 芯 片 , 如 XC9500 ,

XC9500XL 等 。

Ateral 公司的 Maxplus Ⅱ,Quart us Ⅱ,也是业界最著

名的 CPLD/ FP GA 开发工具 ,支持所有的 Ateral 芯片 ,如

MAX3000 ,MAX7000 ,MAX

Ⅱ系列。

由于 EDA 软件已经发展得相当完善 ,用户甚至可以

不用详细了解 CPLD 的内部结构 ,也可以用自己熟悉的方

法 :如原理图输入或 HDL 语言来完成相当优秀的 CPLD

设计 。

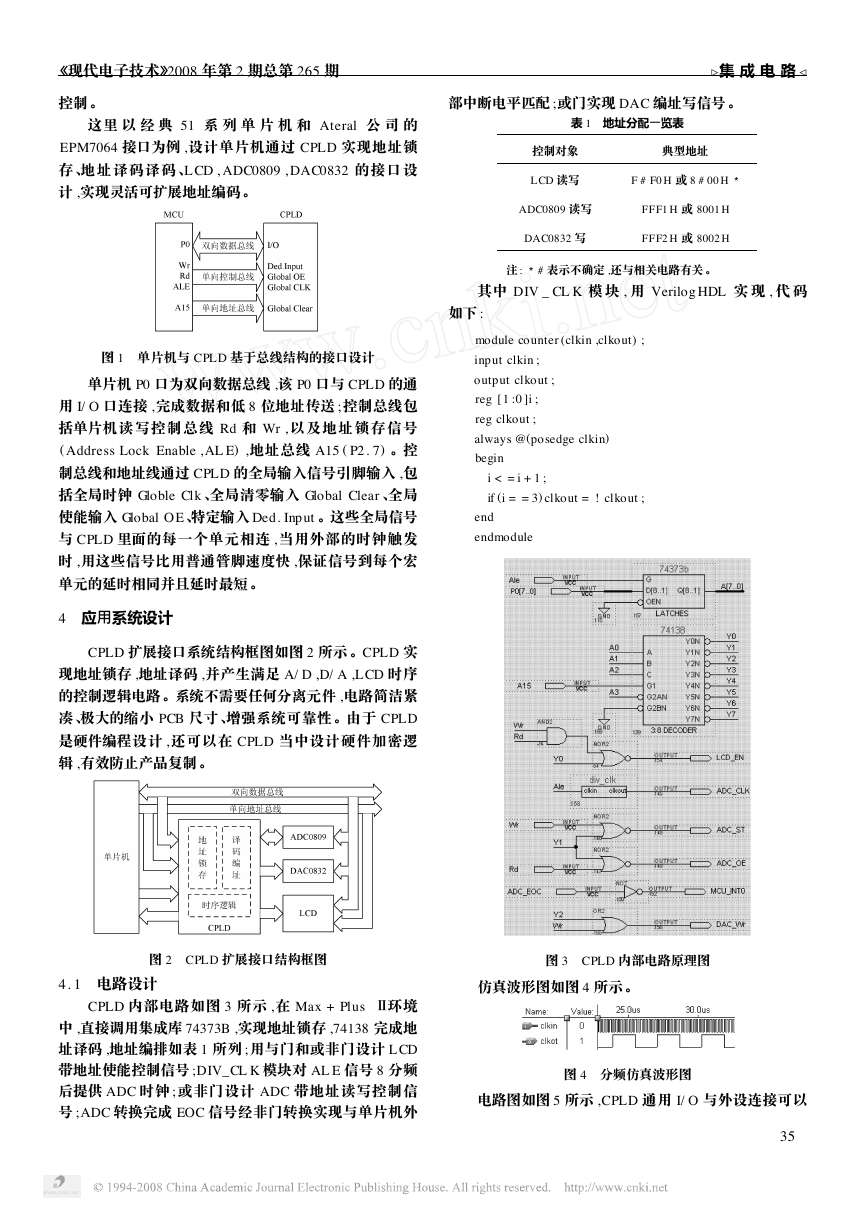

3 单片机与 CPLD 接口设计

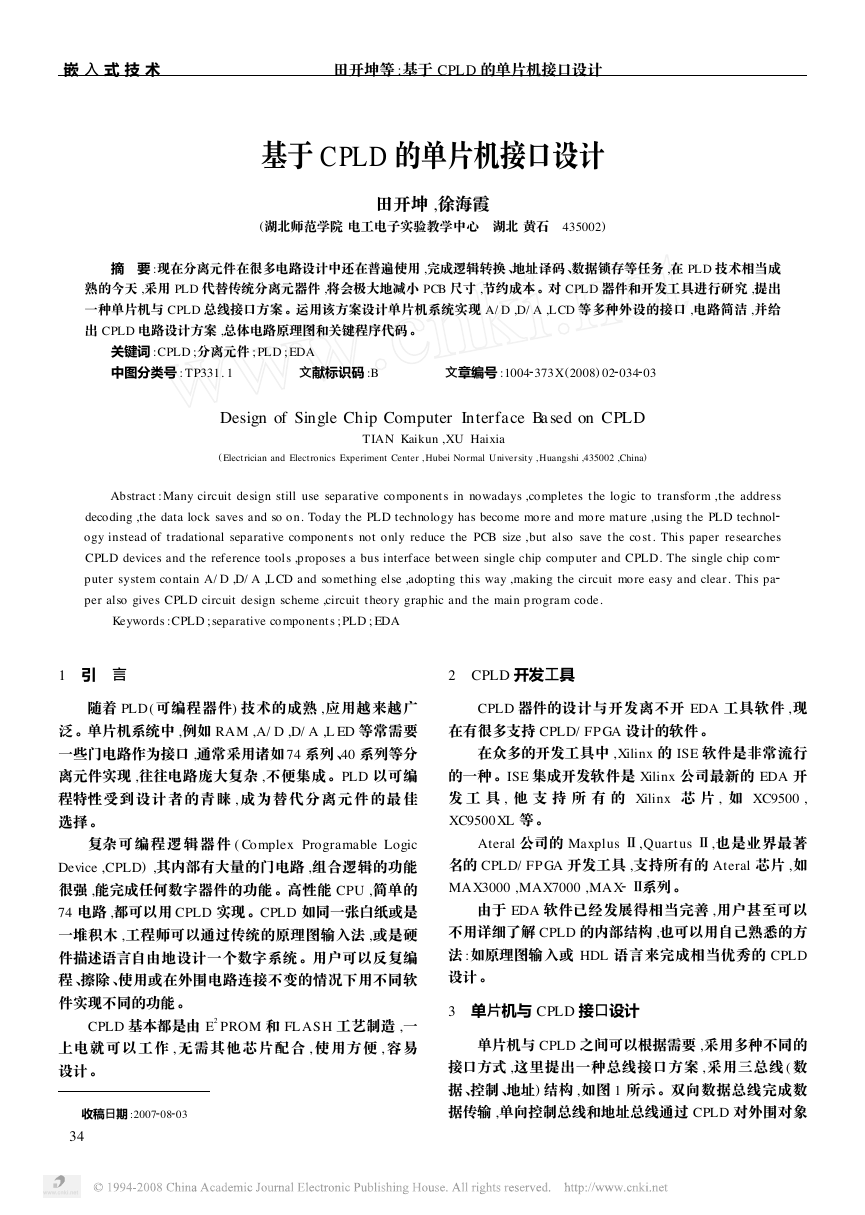

单片机与 CPLD 之间可以根据需要 ,采用多种不同的

接口方式 ,这里提出一种总线接口方案 ,采用三总线 ( 数

据 、控制、地址) 结构 ,如图 1 所示。双向数据总线完成数

据传输 ,单向控制总线和地址总线通过 CPLD 对外围对象

《现代电子技术》2008 年第 2 期总第 265 期

集 成 电 路

控制。

部中断电平匹配 ;或门实现 DAC 编址写信号 。

表 1 地址分配一览表

控制对象

典型地址

L CD 读写

F # F0 H 或 8 # 00 H

ADC0809 读写

FFF1 H 或 8001 H

DAC0832 写

FFF2 H 或 8002 H

# 表示不确定 ,还与相关电路有关 。

注 :

其中 DIV _ CL K 模 块 , 用 Verilog HDL 实 现 , 代 码

如下 :

module counter (clkin ,clkout) ;

input clkin ;

output clkout ;

reg [ 1 :0 ]i ;

reg clkout ;

always @(posedge clkin)

begin

i < = i + 1 ;

if (i = = 3) clkout = ! clkout ;

end

endmodule

这里 以 经 典 51 系 列 单 片 机 和 Ateral 公 司 的

EPM7064 接口为例 ,设计单片机通过 CPLD 实现地址锁

存 、地址译码译码 、L CD , ADC0809 , DAC0832 的接口 设

计 ,实现灵活可扩展地址编码。

图 1 单片机与 CPLD 基于总线结构的接口设计

单片机 P0 口为双向数据总线 ,该 P0 口与 CPLD 的通

用 I/ O 口连接 ,完成数据和低 8 位地址传送 ;控制总线包

括单片机读写控制总线 Rd 和 Wr , 以及地址锁存信号

(Address Lock Enable , AL E) ,地址总线 A15 ( P2. 7) 。控

制总线和地址线通过 CPLD 的全局输入信号引脚输入 ,包

括全局时钟 Globle Clk 、全局清零输入 Global Clear 、全局

使能输入 Global OE、特定输入 Ded. Input 。这些全局信号

与 CPLD 里面的每一个单元相连 ,当用外部的时钟触发

时 ,用这些信号比用普通管脚速度快 ,保证信号到每个宏

单元的延时相同并且延时最短 。

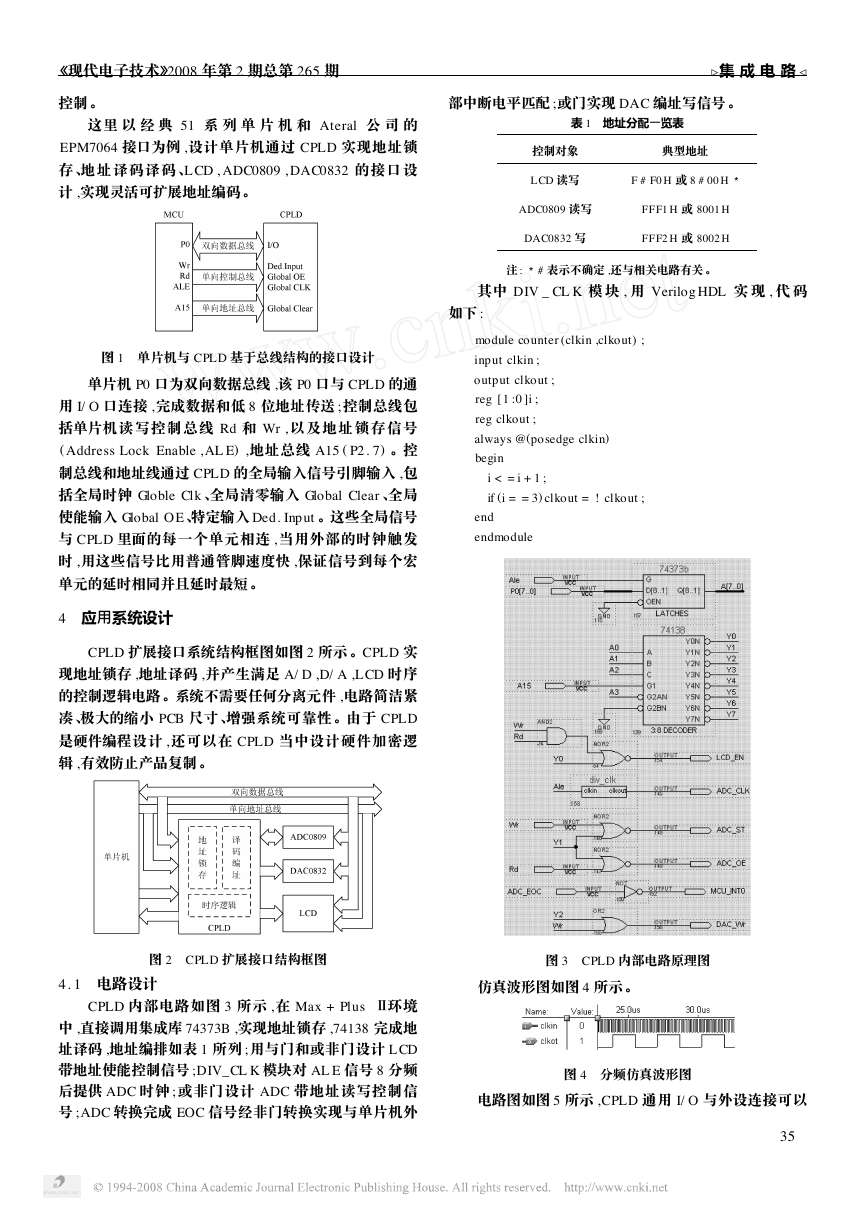

4 应用系统设计

CPLD 扩展接口系统结构框图如图 2 所示 。CPLD 实

现地址锁存 ,地址译码 ,并产生满足 A/ D ,D/ A ,L CD 时序

的控制逻辑电路。系统不需要任何分离元件 ,电路简洁紧

凑 、极大的缩小 PCB 尺寸 、增强系统可靠性。由于 CPLD

是硬件编程设计 ,还可以在 CPLD 当中设计硬件加密逻

辑 ,有效防止产品复制 。

图 2 CPLD 扩展接口结构框图

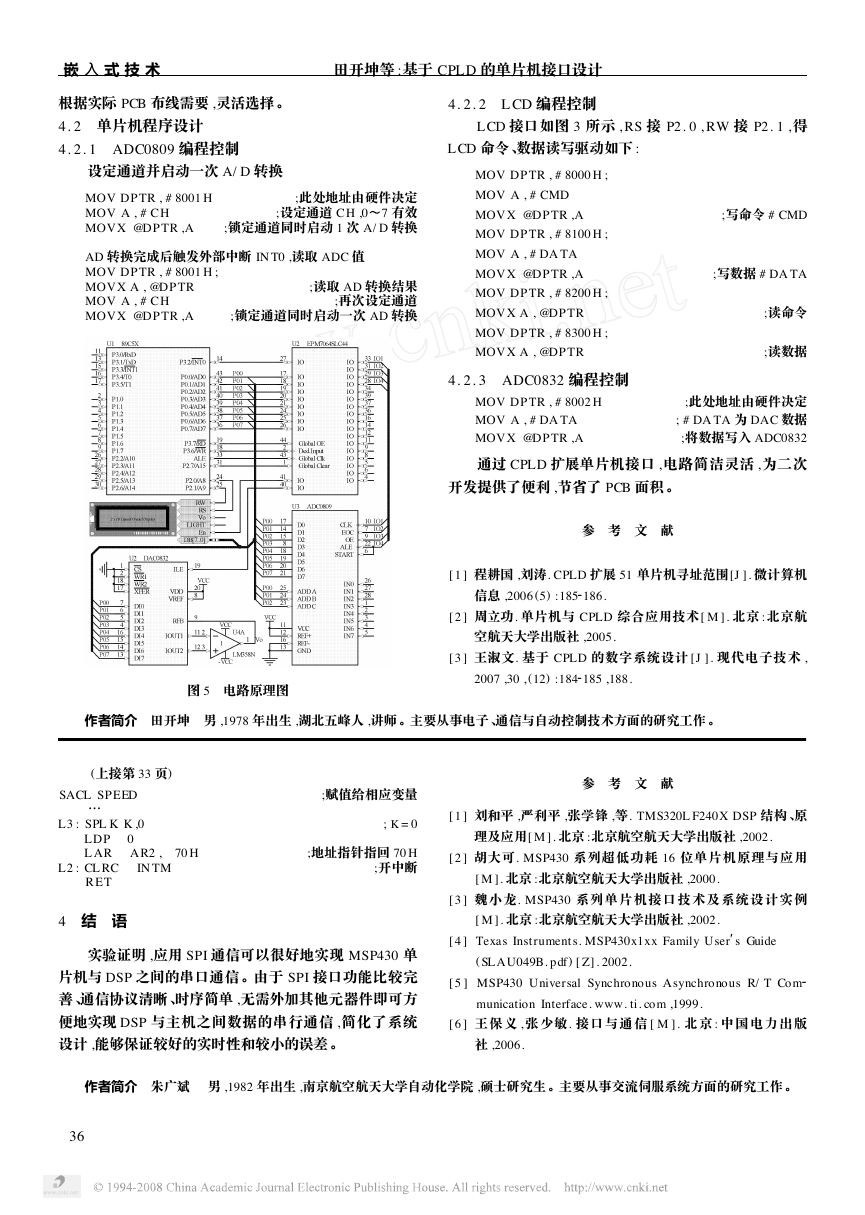

4. 1 电路设计

CPLD 内部电路如图 3 所示 ,在 Max + Plus Ⅱ环境

中 ,直接调用集成库 74373B ,实现地址锁存 ,74138 完成地

址译码 ,地址编排如表 1 所列 ;用与门和或非门设计 L CD

带地址使能控制信号 ;DIV_CL K 模块对 AL E 信号 8 分频

后提供 ADC 时钟 ; 或非门设计 ADC 带地址读写控制信

号 ;ADC 转换完成 EOC 信号经非门转换实现与单片机外

图 3 CPLD 内部电路原理图

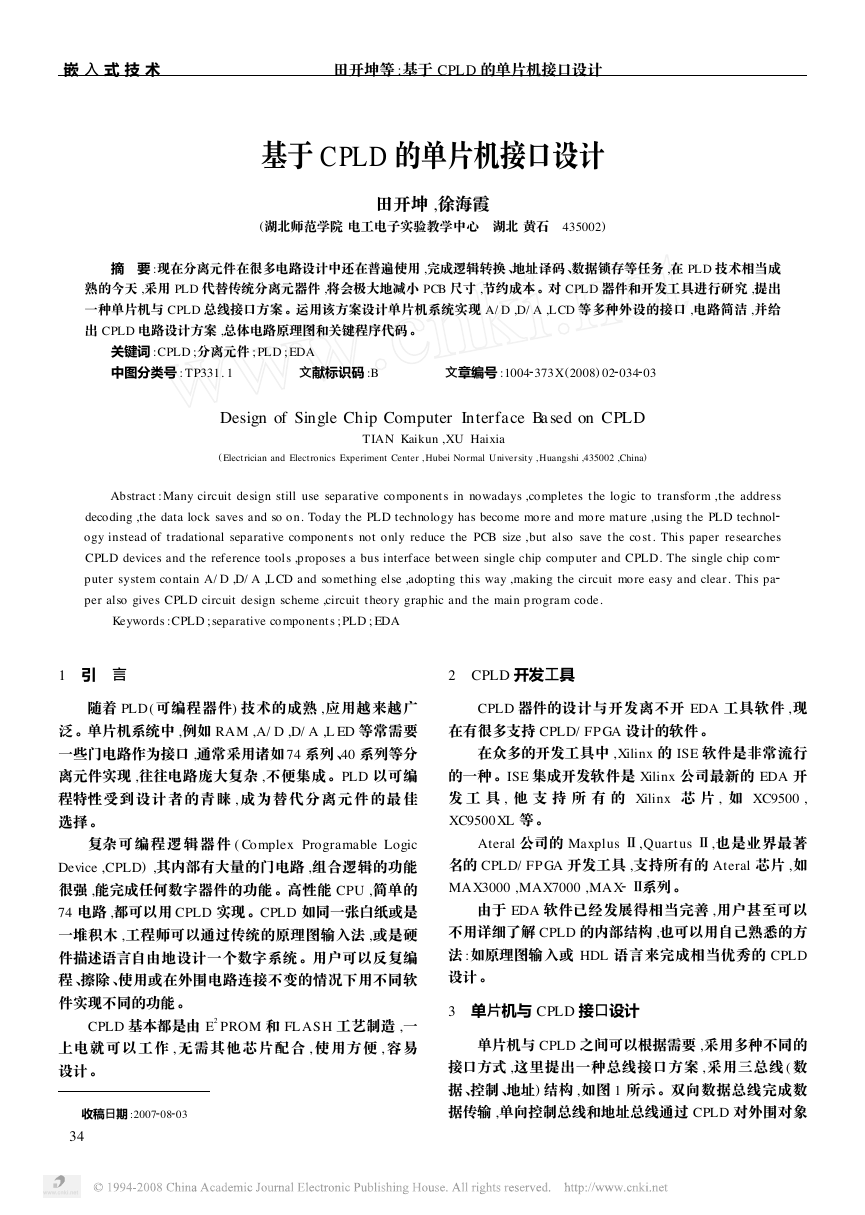

仿真波形图如图 4 所示。

图 4 分频仿真波形图

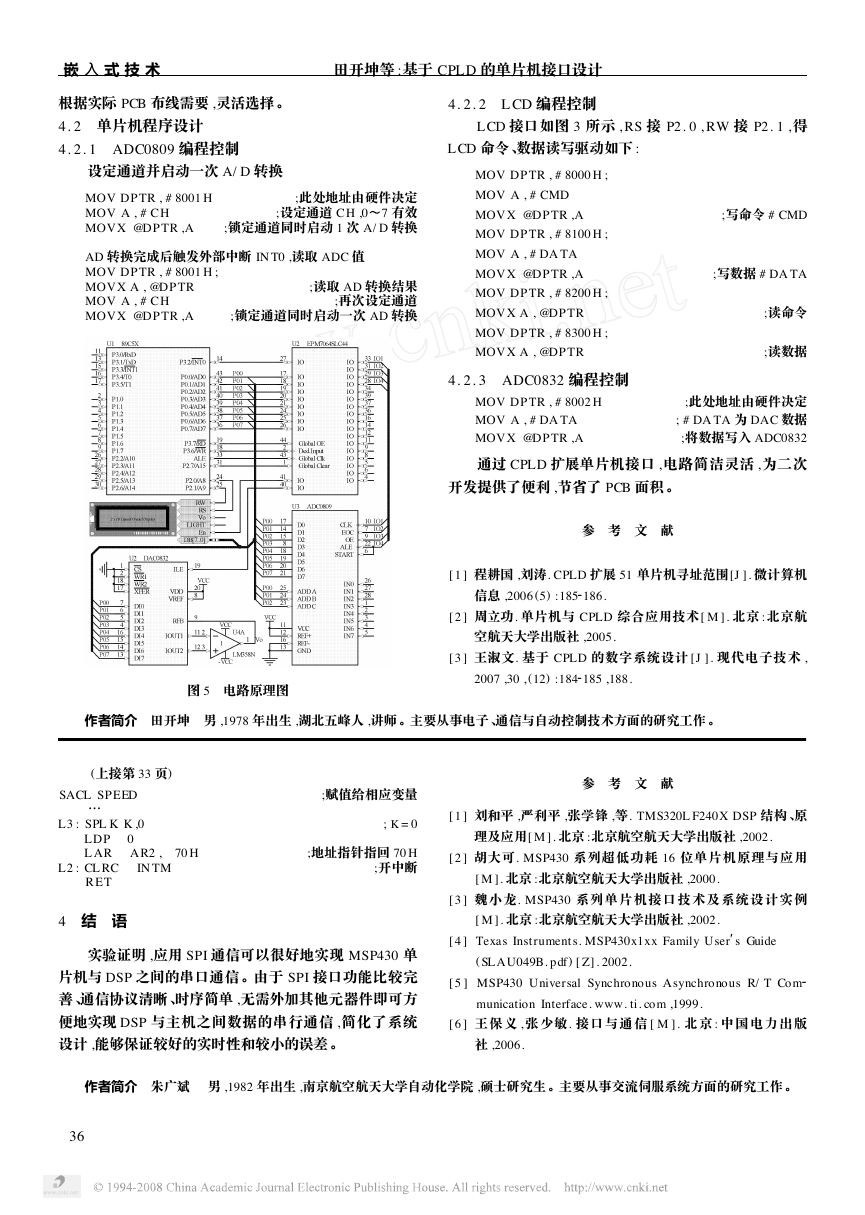

电路图如图 5 所示 ,CPLD 通用 I/ O 与外设连接可以

53

�

2

根据实际 PCB 布线需要 ,灵活选择。

4. 2 单片机程序设计

4. 2. 1 ADC0809 编程控制

设定通道并启动一次 A/ D 转换

MOV DP TR , # 8001 H

MOV A , # C H

MOVX @DP TR ,A

;此处地址由硬件决定

;设定通道 C H ,0~7 有效

;锁定通道同时启动 1 次 A/ D 转换

AD 转换完成后触发外部中断 IN T0 ,读取 ADC 值

MOV DP TR , # 8001 H ;

MOVX A , @DP TR

MOV A , # C H

MOVX @DP TR ,A

;读取 AD 转换结果

;再次设定通道

;锁定通道同时启动一次 AD 转换

图 5 电路原理图

L CD 接口如图 3 所示 , RS 接 P2. 0 , RW 接 P2. 1 ,得

L CD 命令、数据读写驱动如下 :

MOV DP TR , # 8000 H ;

MOV A , # CMD

MOVX @DP TR ,A

MOV DP TR , # 8100 H ;

MOV A , # DA TA

MOVX @DP TR ,A

MOV DP TR , # 8200 H ;

MOVX A , @DP TR

MOV DP TR , # 8300 H ;

MOVX A , @DP TR

;写命令 # CMD

;写数据 # DA TA

;读命令

;读数据

4. 2. 3 ADC0832 编程控制

MOV DP TR , # 8002 H

MOV A , # DA TA

MOVX @DP TR ,A

;此处地址由硬件决定

; # DA TA 为 DAC 数据

;将数据写入 ADC0832

通过 CPLD 扩展单片机接口 ,电路简洁灵活 ,为二次

开发提供了便利 ,节省了 PCB 面积 。

参 考 文 献

[ 1 ] 程耕国 ,刘涛. CPLD 扩展 51 单片机寻址范围[J ]. 微计算机

信息 ,2006 (5) :185

186.

[ 2 ] 周立功. 单片机与 CPLD 综合应用技术 [ M ]. 北京 :北京航

空航天大学出版社 ,2005.

[ 3 ] 王淑文. 基于 CPLD 的数字系统设计 [J ]. 现代电子技术 ,

2007 ,30 , (12) :184

185 ,188.

嵌 入 式 技 术

田开坤等 :基于 CPLD 的单片机接口设计

4. 2. 2 L CD 编程控制

作者简介 田开坤 男 ,1978 年出生 ,湖北五峰人 ,讲师 。主要从事电子 、通信与自动控制技术方面的研究工作 。

(上接第 33 页)

SACL SPEED

…

L3 : SPL K K ,0

LDP 0

L AR AR2 , 70 H

L2 : CL RC IN TM

;赋值给相应变量

; K = 0

;地址指针指回 70 H

;开中断

RET

4 结 语

实验证明 ,应用 SPI 通信可以很好地实现 MSP430 单

片机与 DSP 之间的串口通信 。由于 SPI 接口功能比较完

善 、通信协议清晰 、时序简单 ,无需外加其他元器件即可方

便地实现 DSP 与主机之间数据的串行通信 ,简化了系统

设计 ,能够保证较好的实时性和较小的误差 。

参 考 文 献

[ 1 ] 刘和平 ,严利平 ,张学锋 ,等. TMS320L F240X DSP 结构 、原

理及应用[ M ]. 北京 :北京航空航天大学出版社 ,2002.

[ 2 ] 胡大可. MSP430 系列超低功耗 16 位单片机原理与应用

[ M ]. 北京 :北京航空航天大学出版社 ,2000.

[ 3 ] 魏小龙. MSP430 系列单片机接口技术及系统设计实例

[ M ]. 北京 :北京航空航天大学出版社 ,2002.

[ 4 ] Texas Instrument s. MSP430x1xx Family User′s Guide

(SL AU049B. pdf) [ Z]. 2002.

[ 5 ] MSP430 Universal Synchronous Asynchronous R/ T Com

munication Interface. www. ti. com ,1999.

[ 6 ] 王保义 , 张少敏. 接口与通信 [ M ]. 北 京 : 中 国 电 力 出 版

社 ,2006.

作者简介 朱广斌 男 ,1982 年出生 ,南京航空航天大学自动化学院 ,硕士研究生 。主要从事交流伺服系统方面的研究工作 。

63

�