1. 问题描述

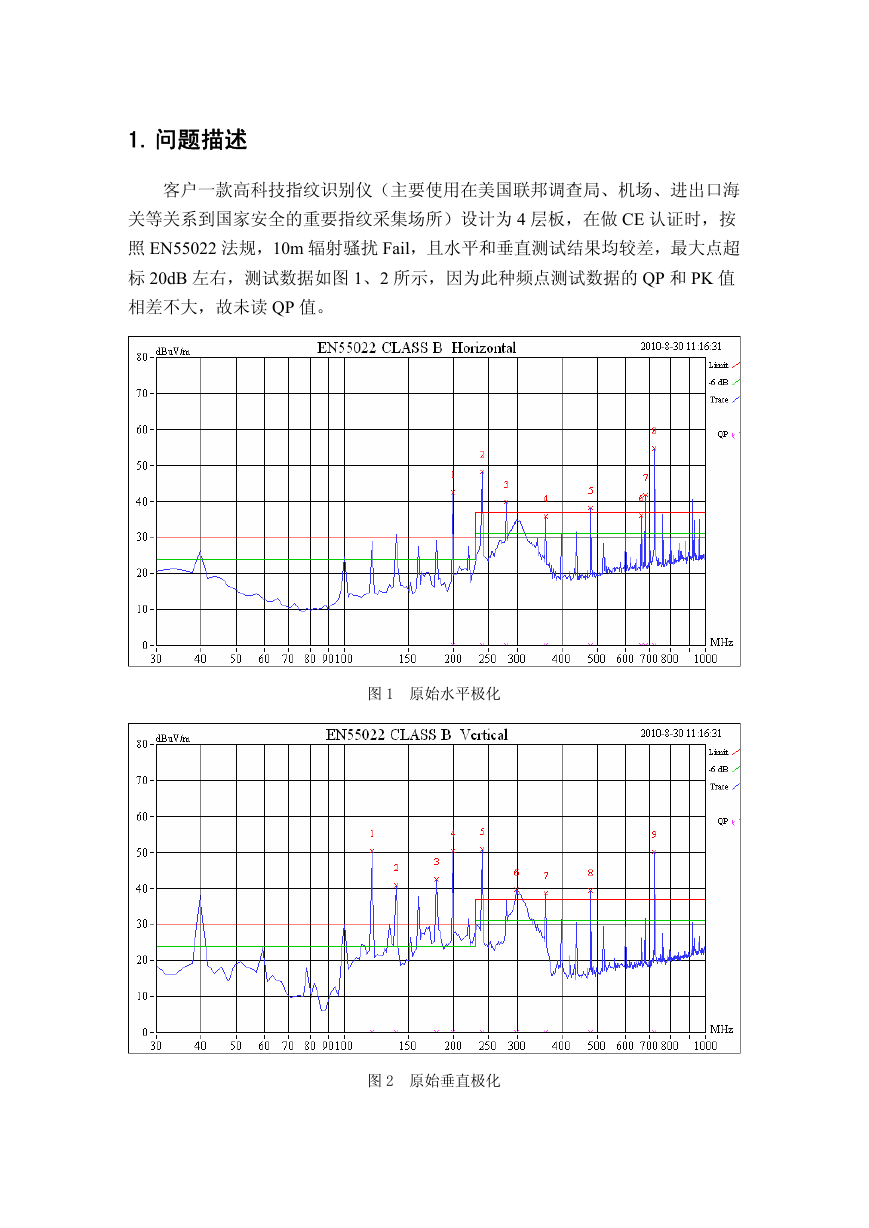

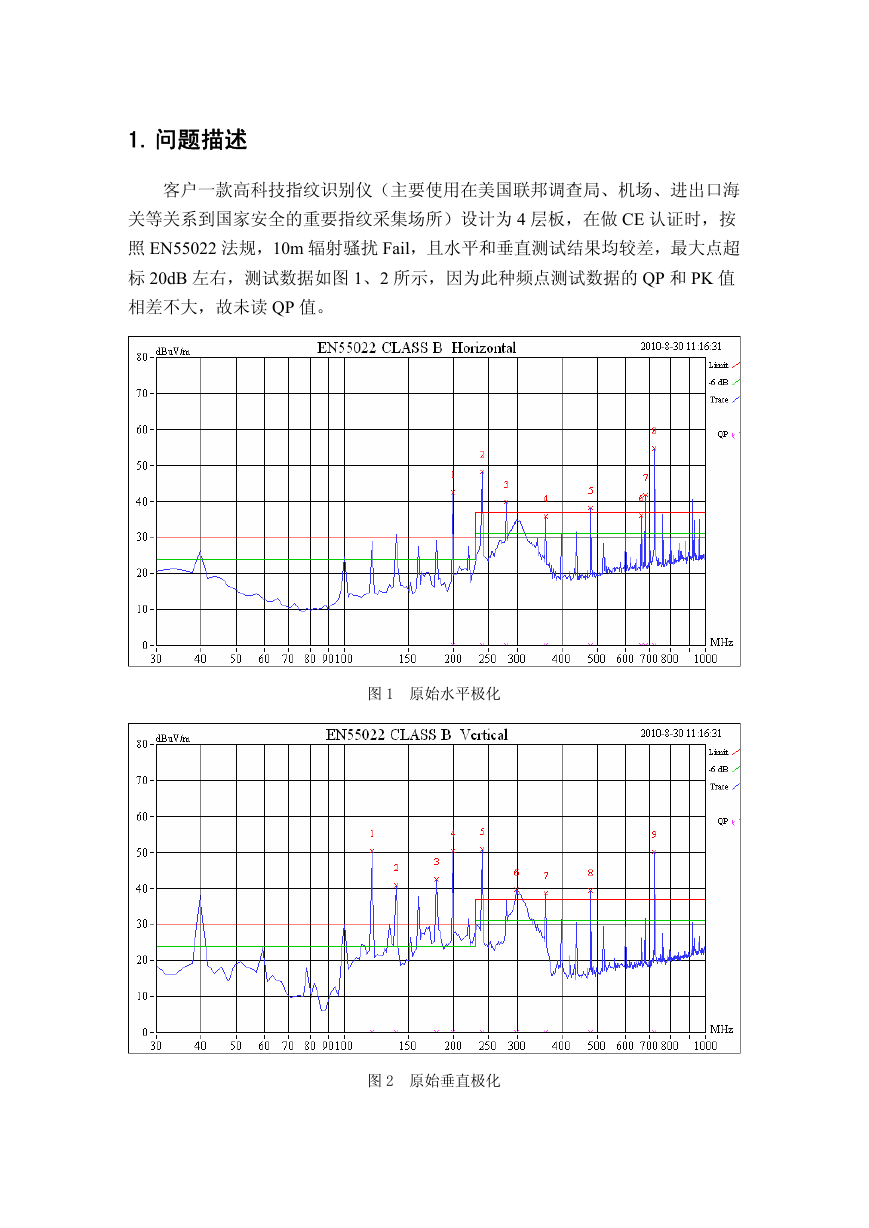

客户一款高科技指纹识别仪(主要使用在美国联邦调查局、机场、进出口海

关等关系到国家安全的重要指纹采集场所)设计为 4 层板,在做 CE 认证时,按

照 EN55022 法规,10m 辐射骚扰 Fail,且水平和垂直测试结果均较差,最大点超

标 20dB 左右,测试数据如图 1、2 所示,因为此种频点测试数据的 QP 和 PK 值

相差不大,故未读 QP 值。

图 1 原始水平极化

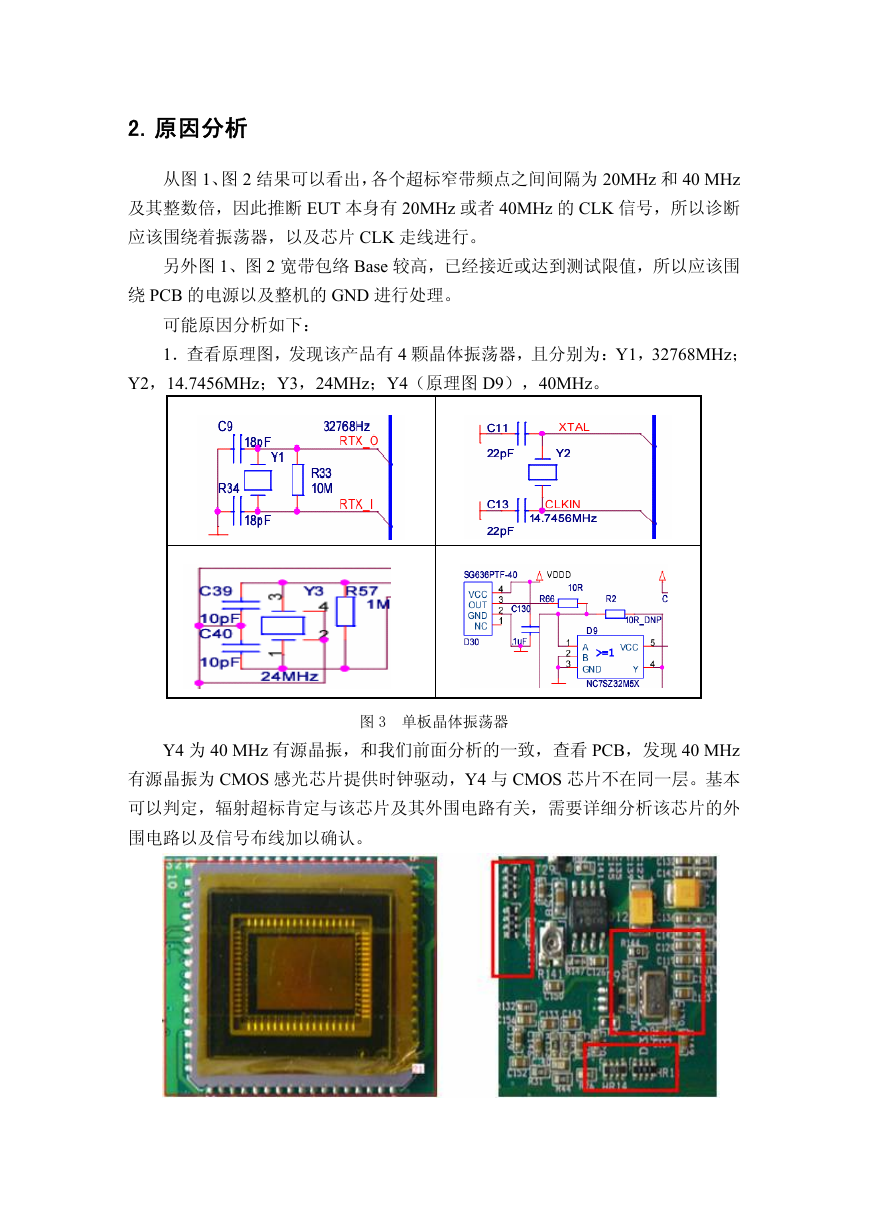

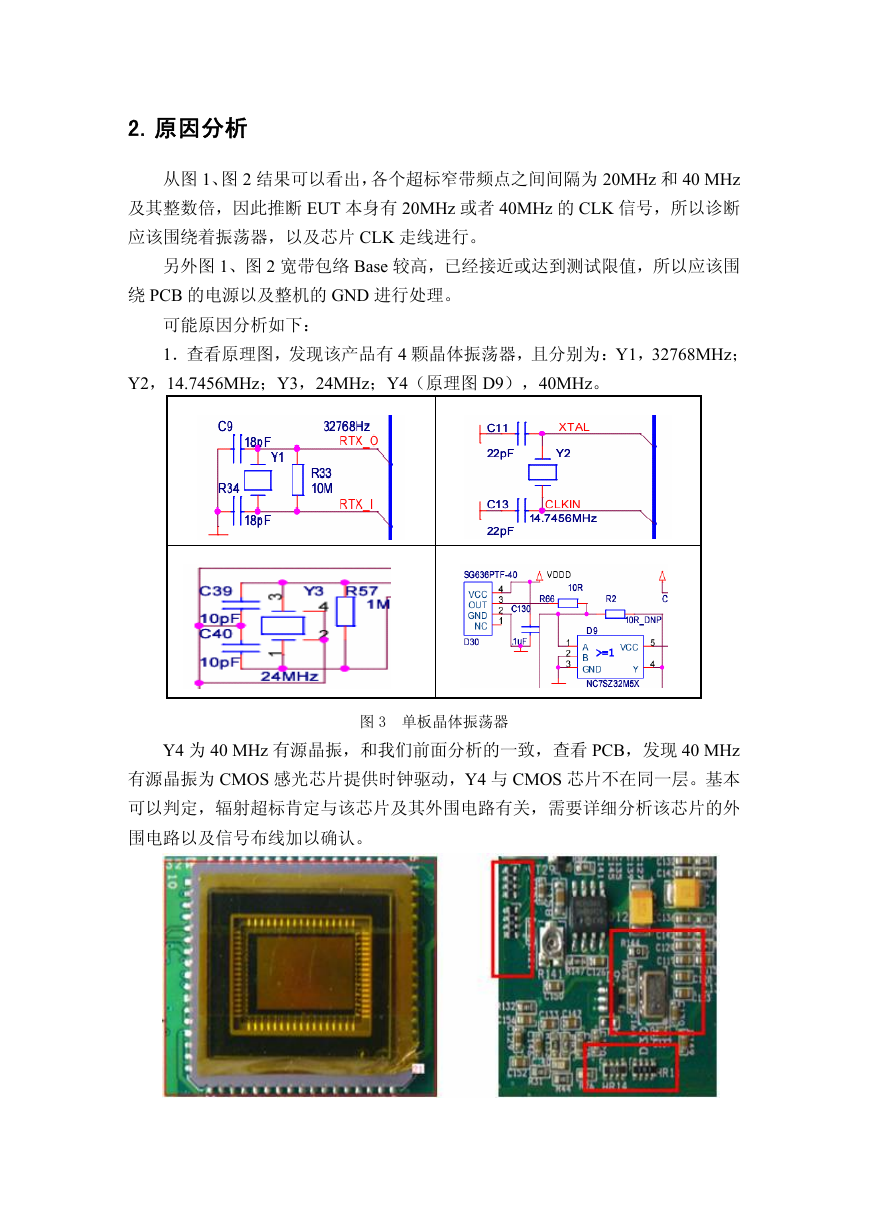

图 2 原始垂直极化

�

2. 原因分析

从图 1、图 2 结果可以看出,各个超标窄带频点之间间隔为 20MHz 和 40 MHz

及其整数倍,因此推断 EUT 本身有 20MHz 或者 40MHz 的 CLK 信号,所以诊断

应该围绕着振荡器,以及芯片 CLK 走线进行。

另外图 1、图 2 宽带包络 Base 较高,已经接近或达到测试限值,所以应该围

绕 PCB 的电源以及整机的 GND 进行处理。

可能原因分析如下:

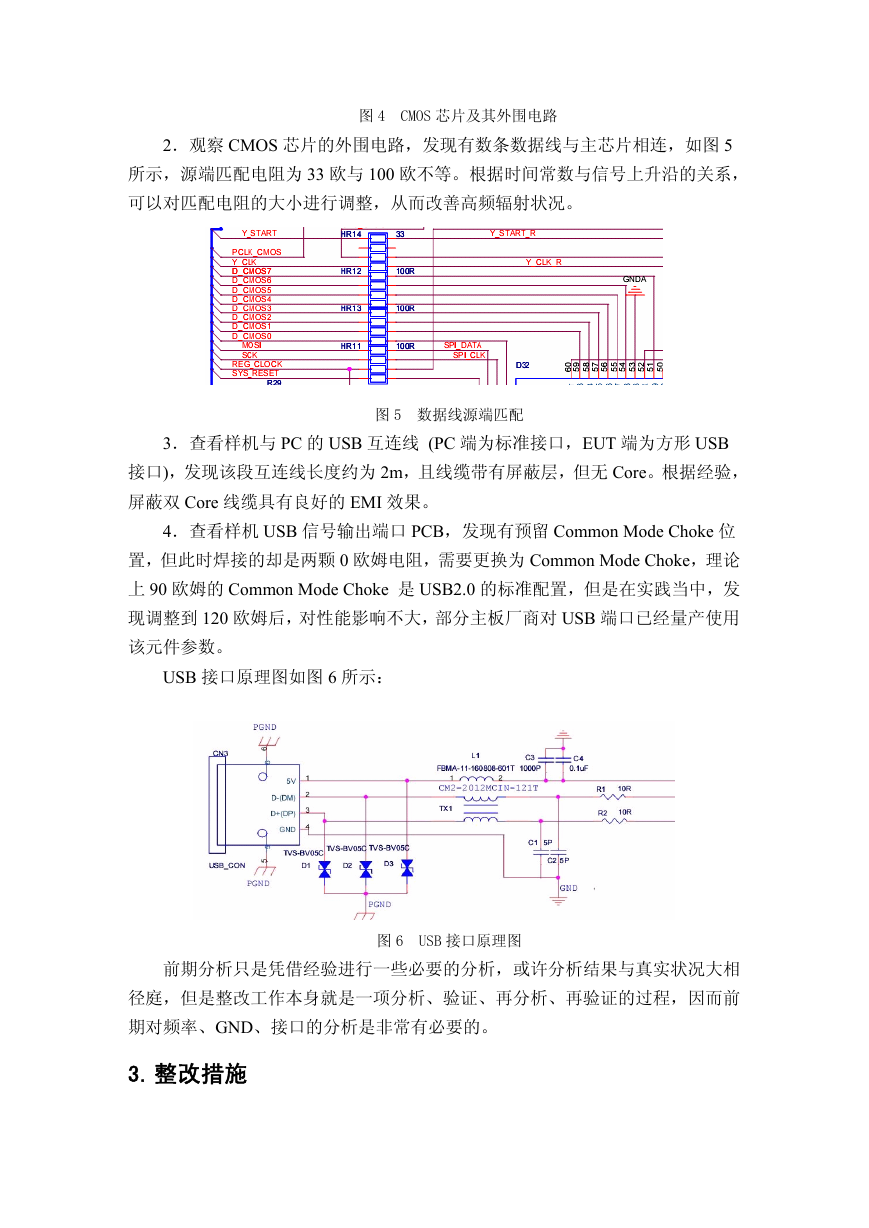

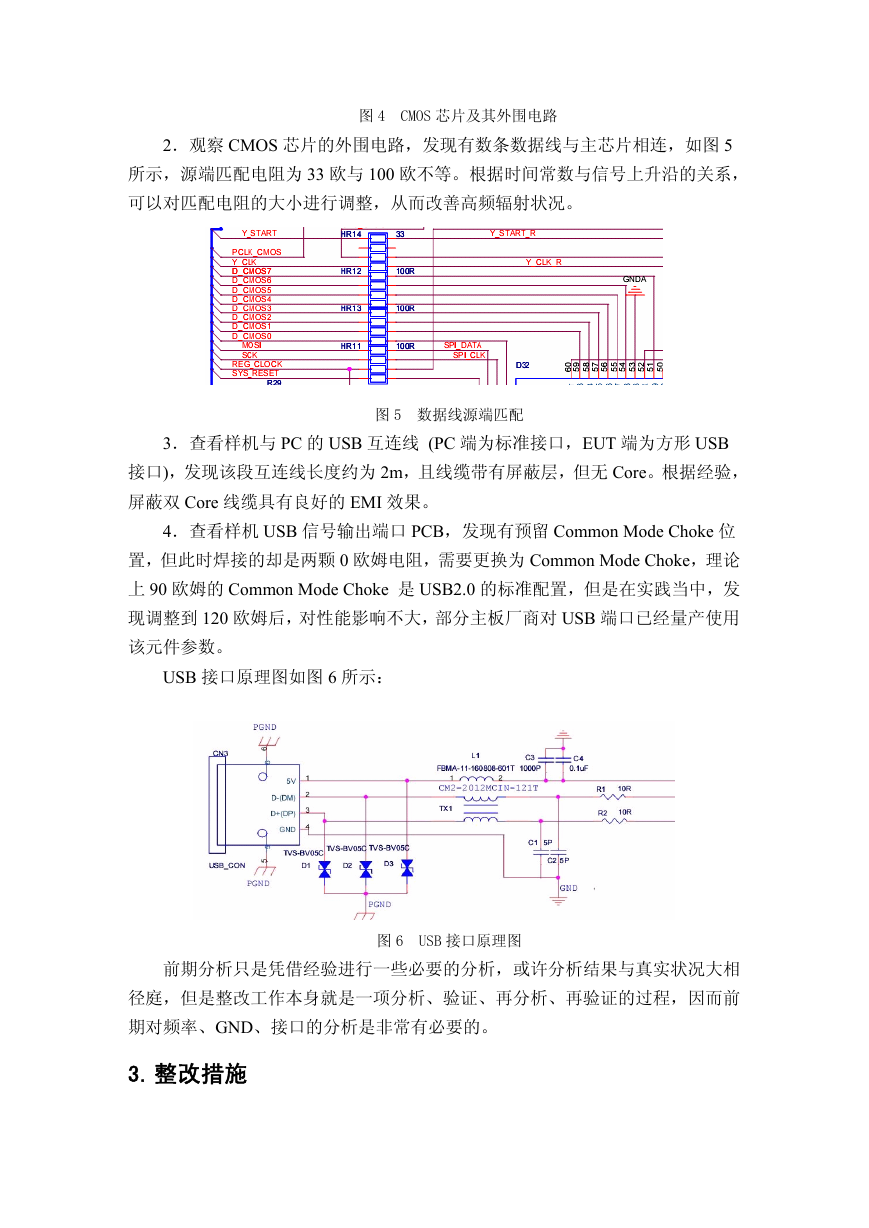

1.查看原理图,发现该产品有 4 颗晶体振荡器,且分别为:Y1,32768MHz;

Y2,14.7456MHz;Y3,24MHz;Y4(原理图 D9),40MHz。

图 3 单板晶体振荡器

Y4 为 40 MHz 有源晶振,和我们前面分析的一致,查看 PCB,发现 40 MHz

有源晶振为 CMOS 感光芯片提供时钟驱动,Y4 与 CMOS 芯片不在同一层。基本

可以判定,辐射超标肯定与该芯片及其外围电路有关,需要详细分析该芯片的外

围电路以及信号布线加以确认。

�

图 4 CMOS 芯片及其外围电路

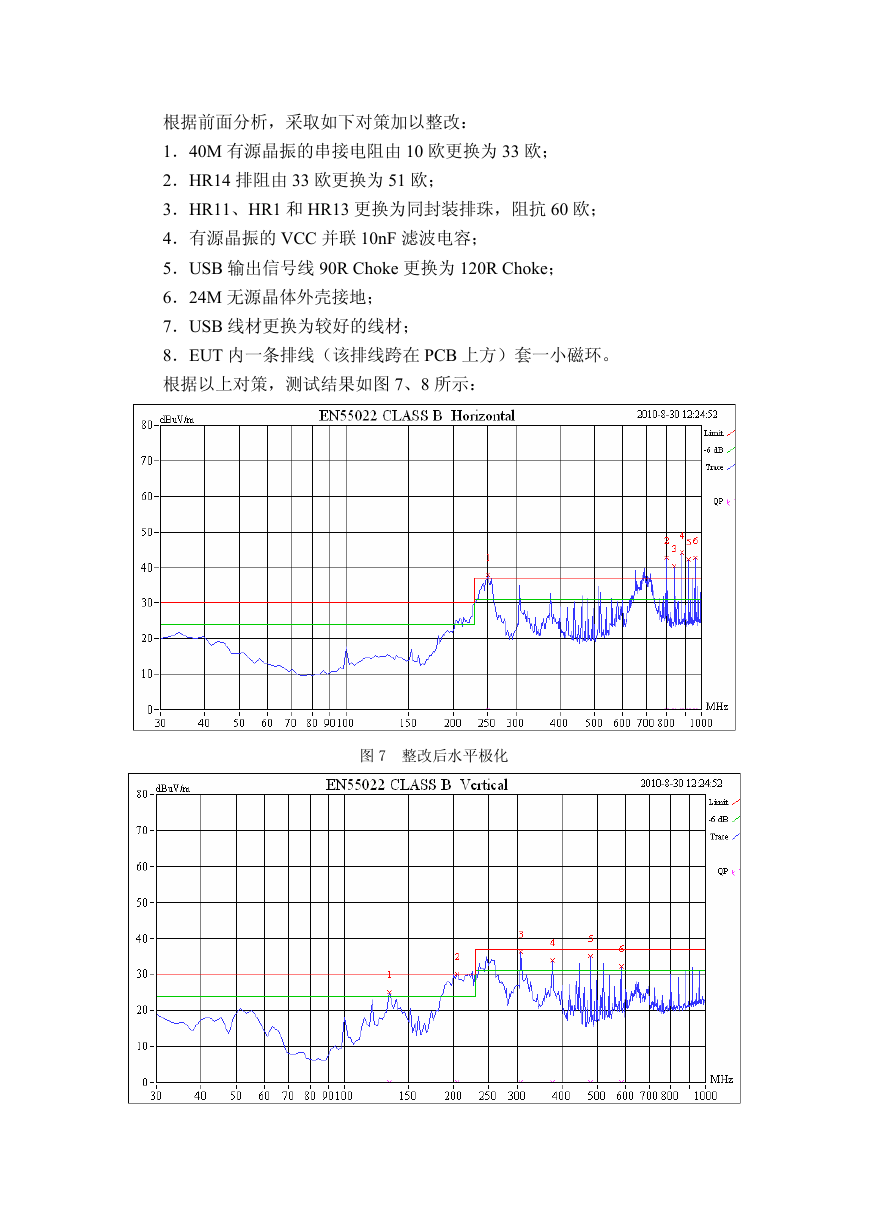

2.观察 CMOS 芯片的外围电路,发现有数条数据线与主芯片相连,如图 5

所示,源端匹配电阻为 33 欧与 100 欧不等。根据时间常数与信号上升沿的关系,

可以对匹配电阻的大小进行调整,从而改善高频辐射状况。

图 5 数据线源端匹配

3.查看样机与 PC 的 USB 互连线 (PC 端为标准接口,EUT 端为方形 USB

接口),发现该段互连线长度约为 2m,且线缆带有屏蔽层,但无 Core。根据经验,

屏蔽双 Core 线缆具有良好的 EMI 效果。

4.查看样机 USB 信号输出端口 PCB,发现有预留 Common Mode Choke 位

置,但此时焊接的却是两颗 0 欧姆电阻,需要更换为 Common Mode Choke,理论

上 90 欧姆的 Common Mode Choke 是 USB2.0 的标准配置,但是在实践当中,发

现调整到 120 欧姆后,对性能影响不大,部分主板厂商对 USB 端口已经量产使用

该元件参数。

USB 接口原理图如图 6 所示:

图 6 USB 接口原理图

前期分析只是凭借经验进行一些必要的分析,或许分析结果与真实状况大相

径庭,但是整改工作本身就是一项分析、验证、再分析、再验证的过程,因而前

期对频率、GND、接口的分析是非常有必要的。

3. 整改措施

�

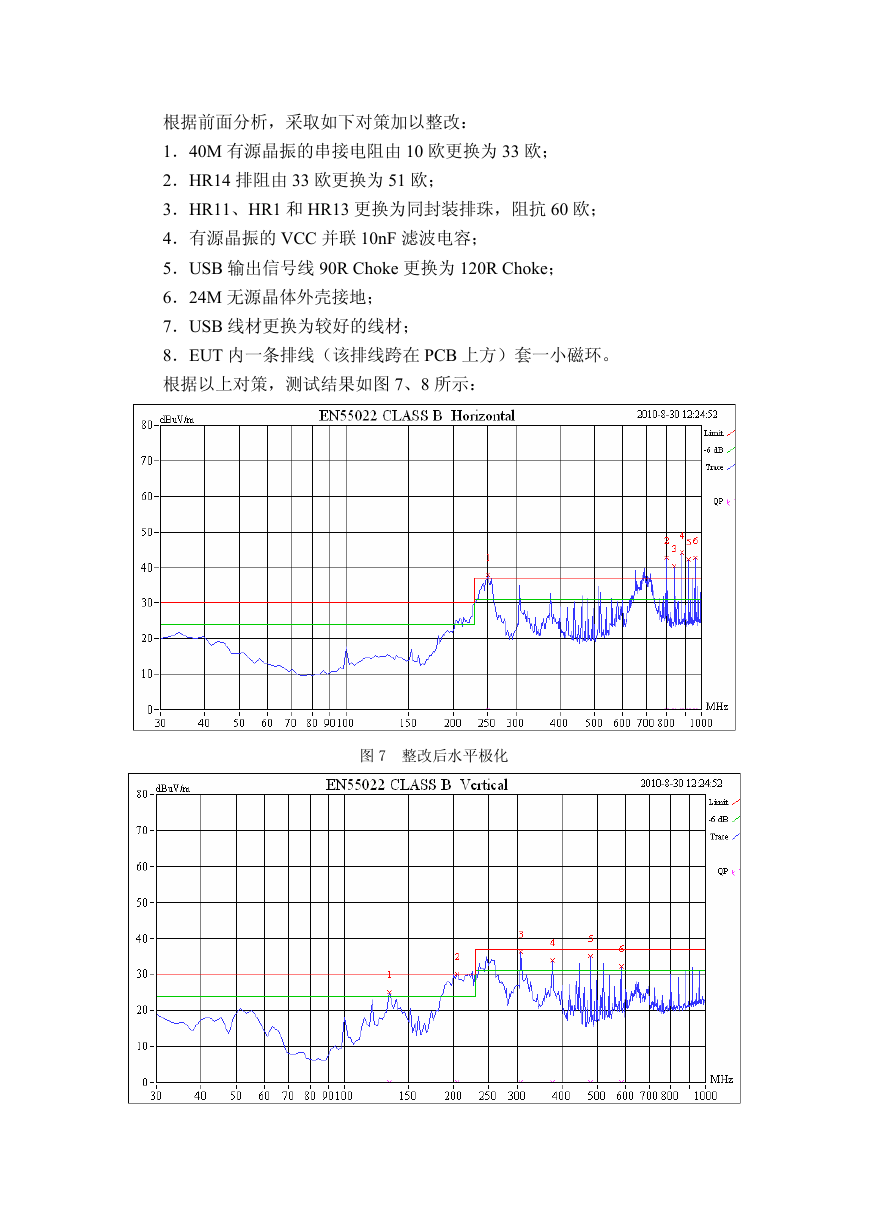

根据前面分析,采取如下对策加以整改:

1.40M 有源晶振的串接电阻由 10 欧更换为 33 欧;

2.HR14 排阻由 33 欧更换为 51 欧;

3.HR11、HR1 和 HR13 更换为同封装排珠,阻抗 60 欧;

4.有源晶振的 VCC 并联 10nF 滤波电容;

5.USB 输出信号线 90R Choke 更换为 120R Choke;

6.24M 无源晶体外壳接地;

7.USB 线材更换为较好的线材;

8.EUT 内一条排线(该排线跨在 PCB 上方)套一小磁环。

根据以上对策,测试结果如图 7、8 所示:

图 7 整改后水平极化

�

图 8 整改后垂直极化

从图 7、8 可以看出,整改之后,测试结果已经有了较大改善。之后继续整改,

加了很多对策进行验证,但是效果微乎其微,无法有效对测试结果进行改善。其

中一个对策是对 CMOS 芯片的引脚进行屏蔽,取得一定效果,测试数据窄带噪声

下降了 4dB 左右,但是考虑到生产等因素,此措施无法实施。

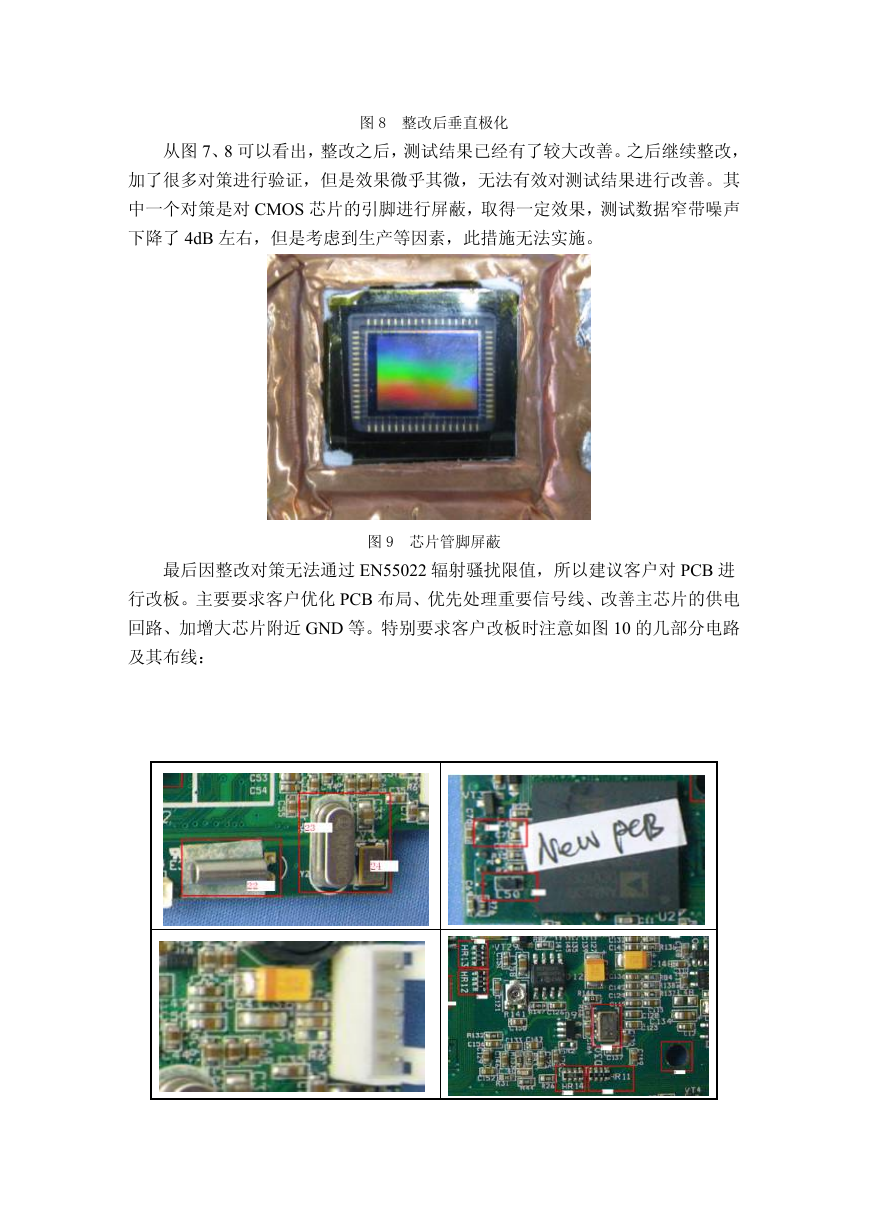

图 9 芯片管脚屏蔽

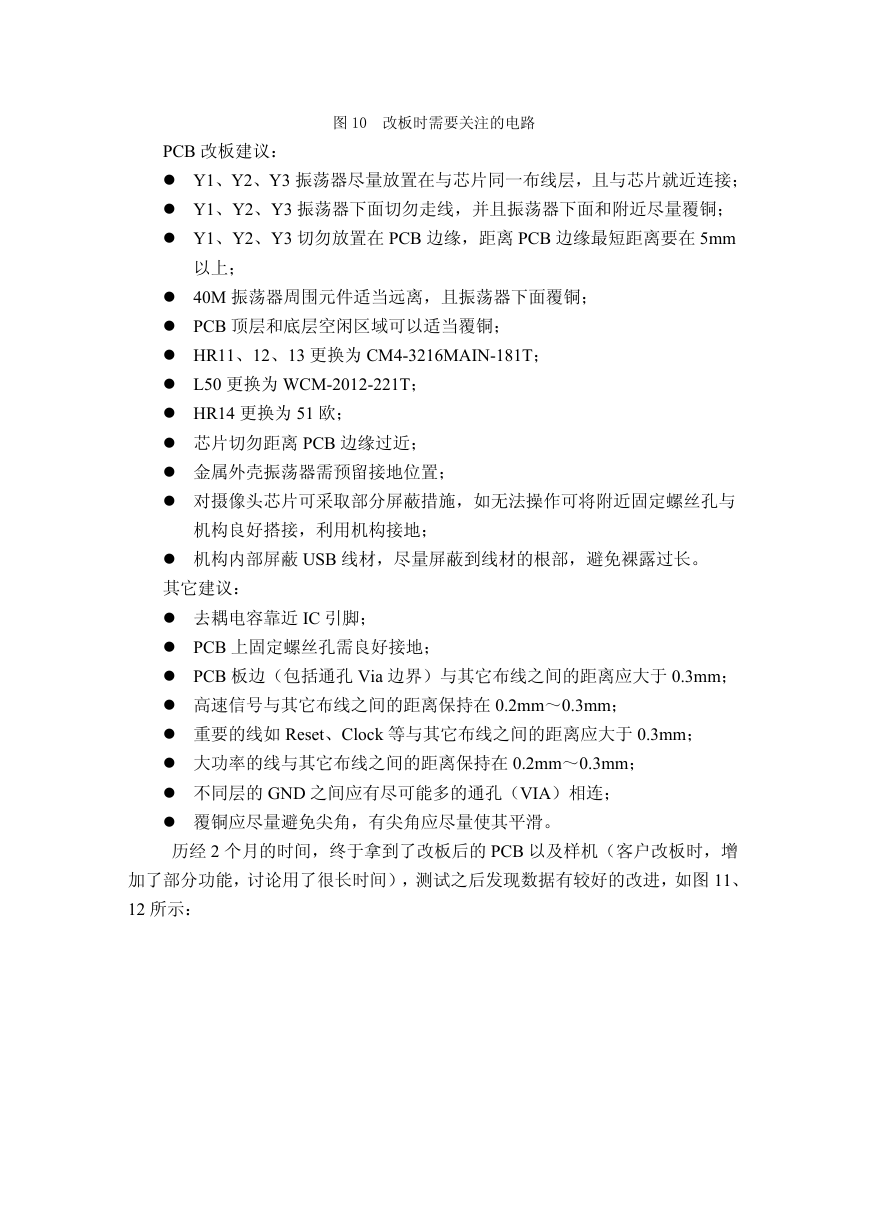

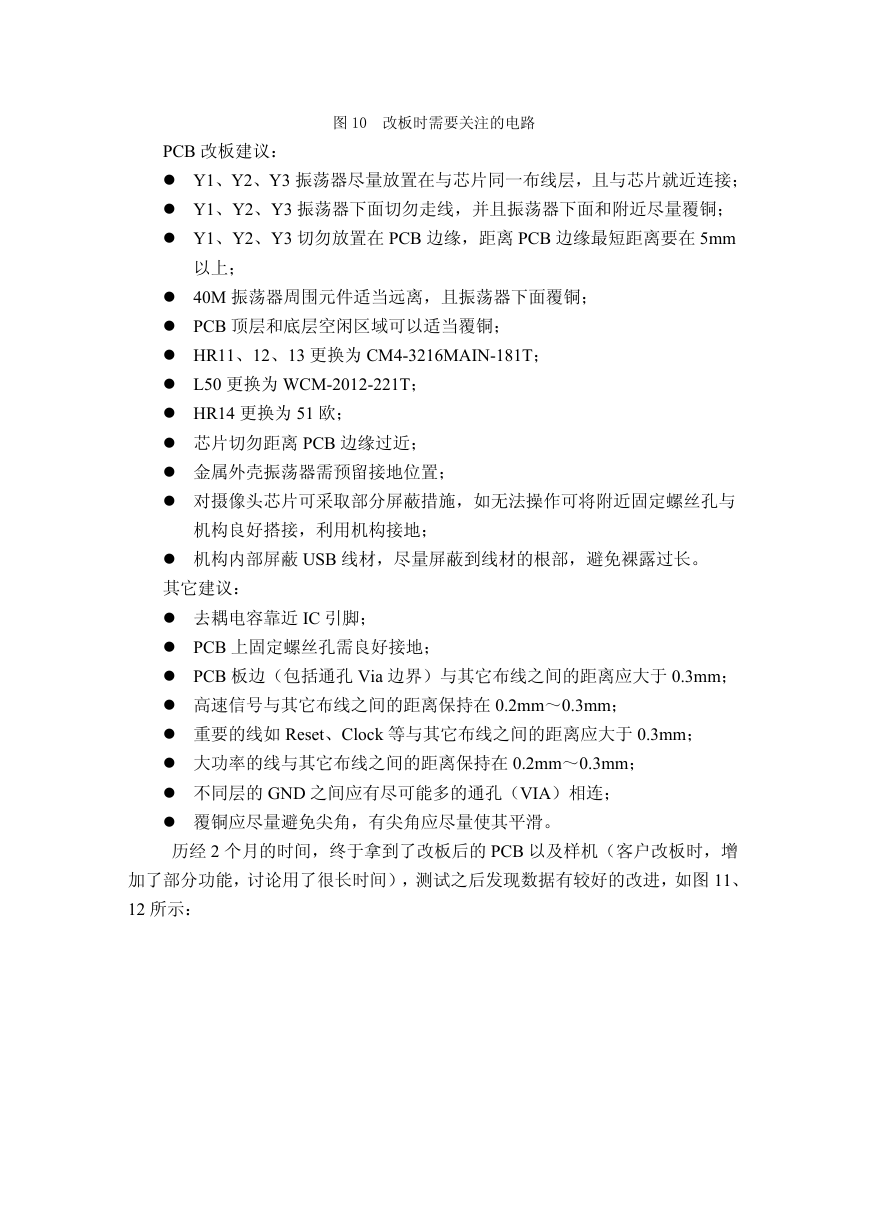

最后因整改对策无法通过 EN55022 辐射骚扰限值,所以建议客户对 PCB 进

行改板。主要要求客户优化 PCB 布局、优先处理重要信号线、改善主芯片的供电

回路、加增大芯片附近 GND 等。特别要求客户改板时注意如图 10 的几部分电路

及其布线:

�

图 10 改板时需要关注的电路

PCB 改板建议:

Y1、Y2、Y3 振荡器尽量放置在与芯片同一布线层,且与芯片就近连接;

Y1、Y2、Y3 振荡器下面切勿走线,并且振荡器下面和附近尽量覆铜;

Y1、Y2、Y3 切勿放置在 PCB 边缘,距离 PCB 边缘最短距离要在 5mm

以上;

40M 振荡器周围元件适当远离,且振荡器下面覆铜;

PCB 顶层和底层空闲区域可以适当覆铜;

HR11、12、13 更换为 CM4-3216MAIN-181T;

L50 更换为 WCM-2012-221T;

HR14 更换为 51 欧;

芯片切勿距离 PCB 边缘过近;

金属外壳振荡器需预留接地位置;

对摄像头芯片可采取部分屏蔽措施,如无法操作可将附近固定螺丝孔与

机构良好搭接,利用机构接地;

机构内部屏蔽 USB 线材,尽量屏蔽到线材的根部,避免裸露过长。

其它建议:

去耦电容靠近 IC 引脚;

PCB 上固定螺丝孔需良好接地;

PCB 板边(包括通孔 Via 边界)与其它布线之间的距离应大于 0.3mm;

高速信号与其它布线之间的距离保持在 0.2mm~0.3mm;

重要的线如 Reset、Clock 等与其它布线之间的距离应大于 0.3mm;

大功率的线与其它布线之间的距离保持在 0.2mm~0.3mm;

不同层的 GND 之间应有尽可能多的通孔(VIA)相连;

覆铜应尽量避免尖角,有尖角应尽量使其平滑。

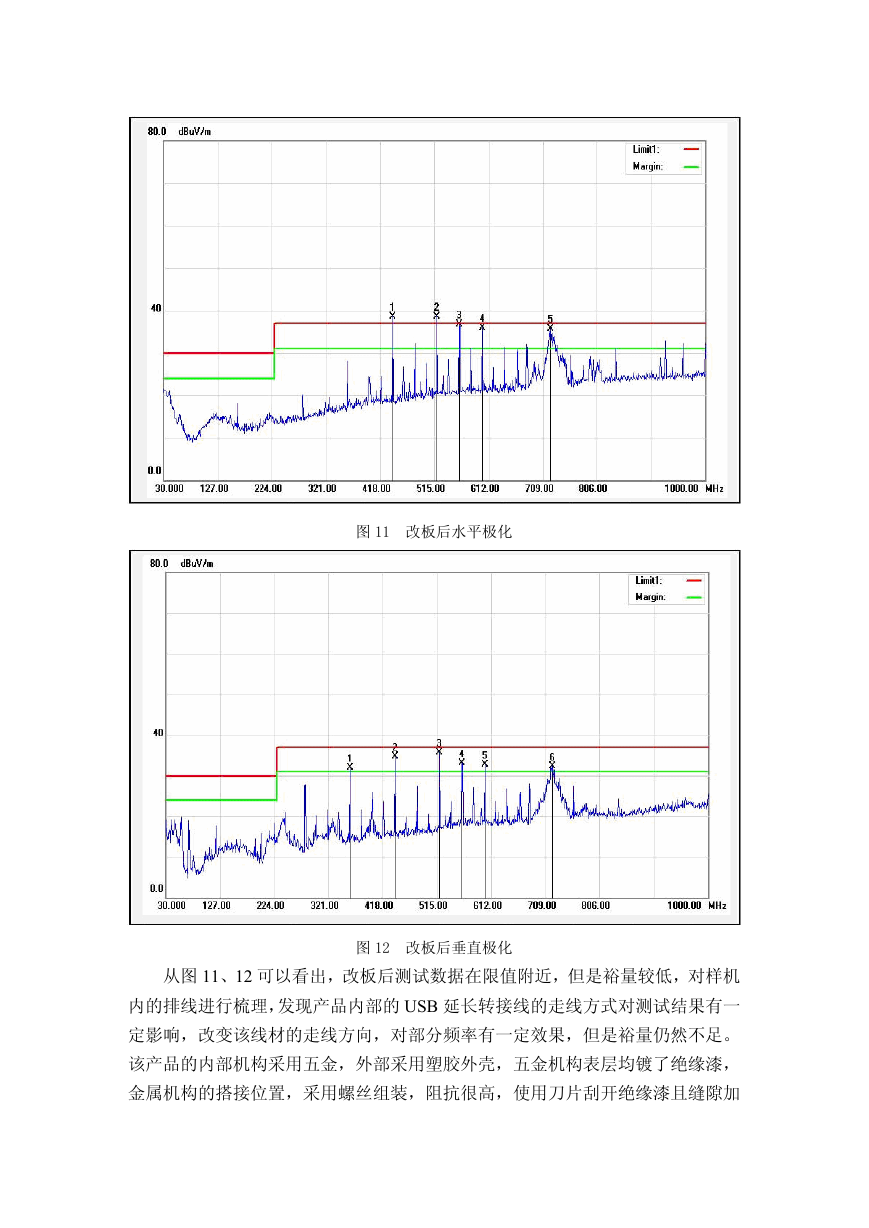

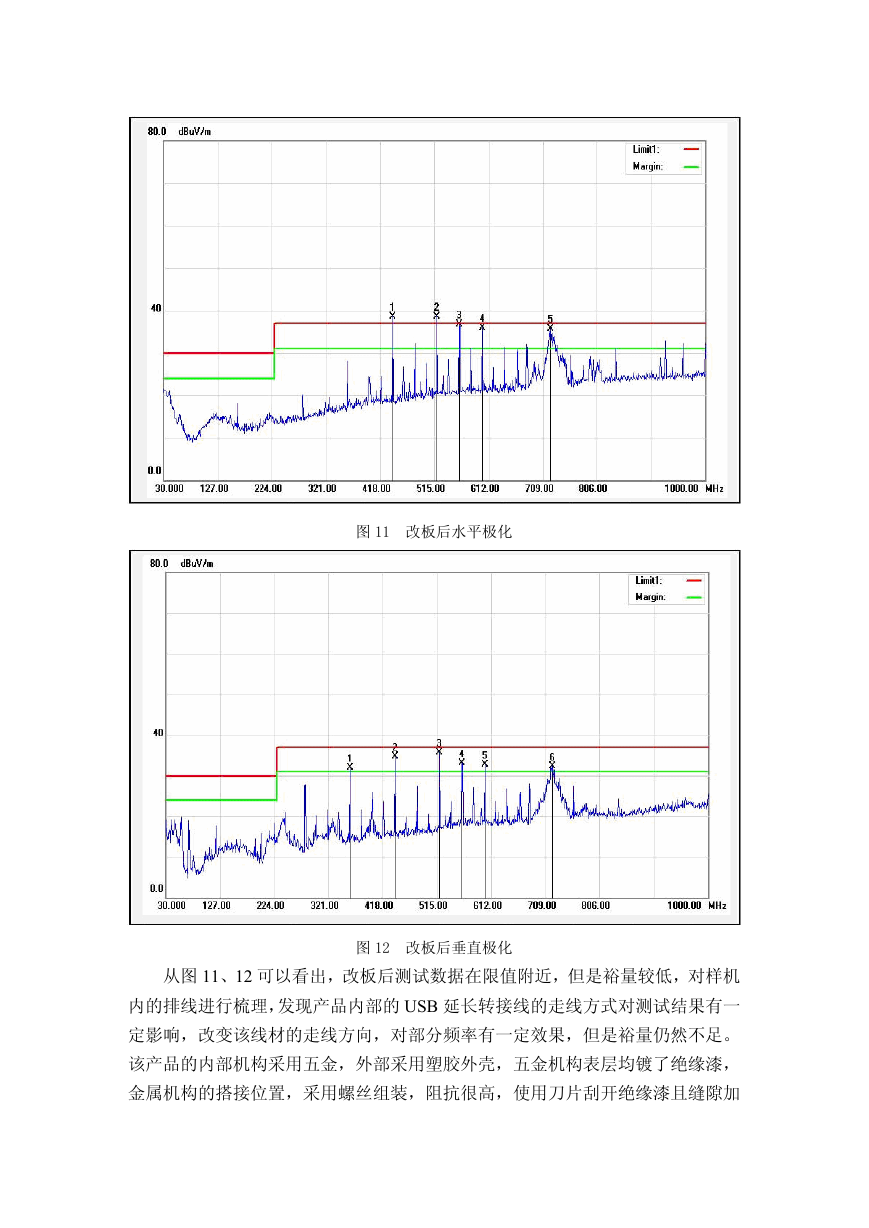

历经 2 个月的时间,终于拿到了改板后的 PCB 以及样机(客户改板时,增

加了部分功能,讨论用了很长时间),测试之后发现数据有较好的改进,如图 11、

12 所示:

�

图 11 改板后水平极化

图 12 改板后垂直极化

从图 11、12 可以看出,改板后测试数据在限值附近,但是裕量较低,对样机

内的排线进行梳理,发现产品内部的 USB 延长转接线的走线方式对测试结果有一

定影响,改变该线材的走线方向,对部分频率有一定效果,但是裕量仍然不足。

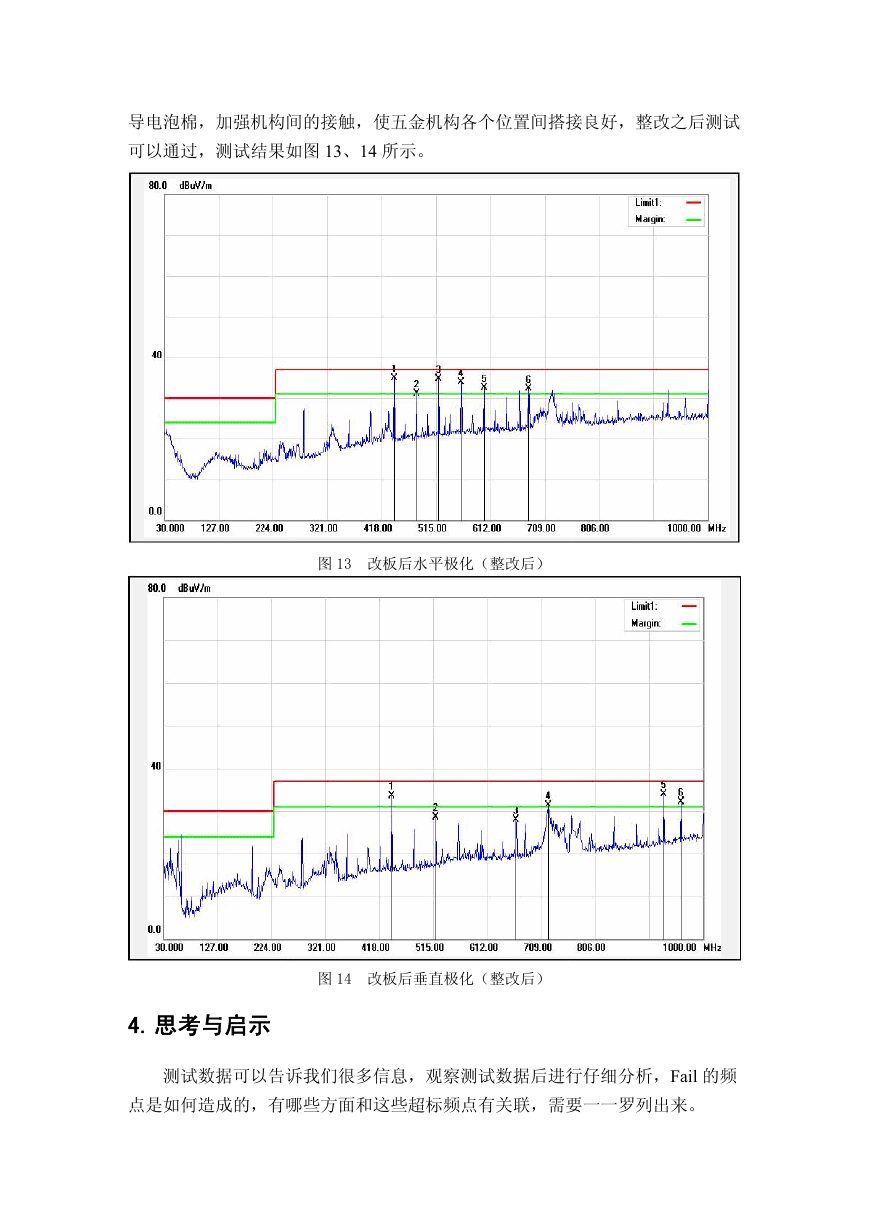

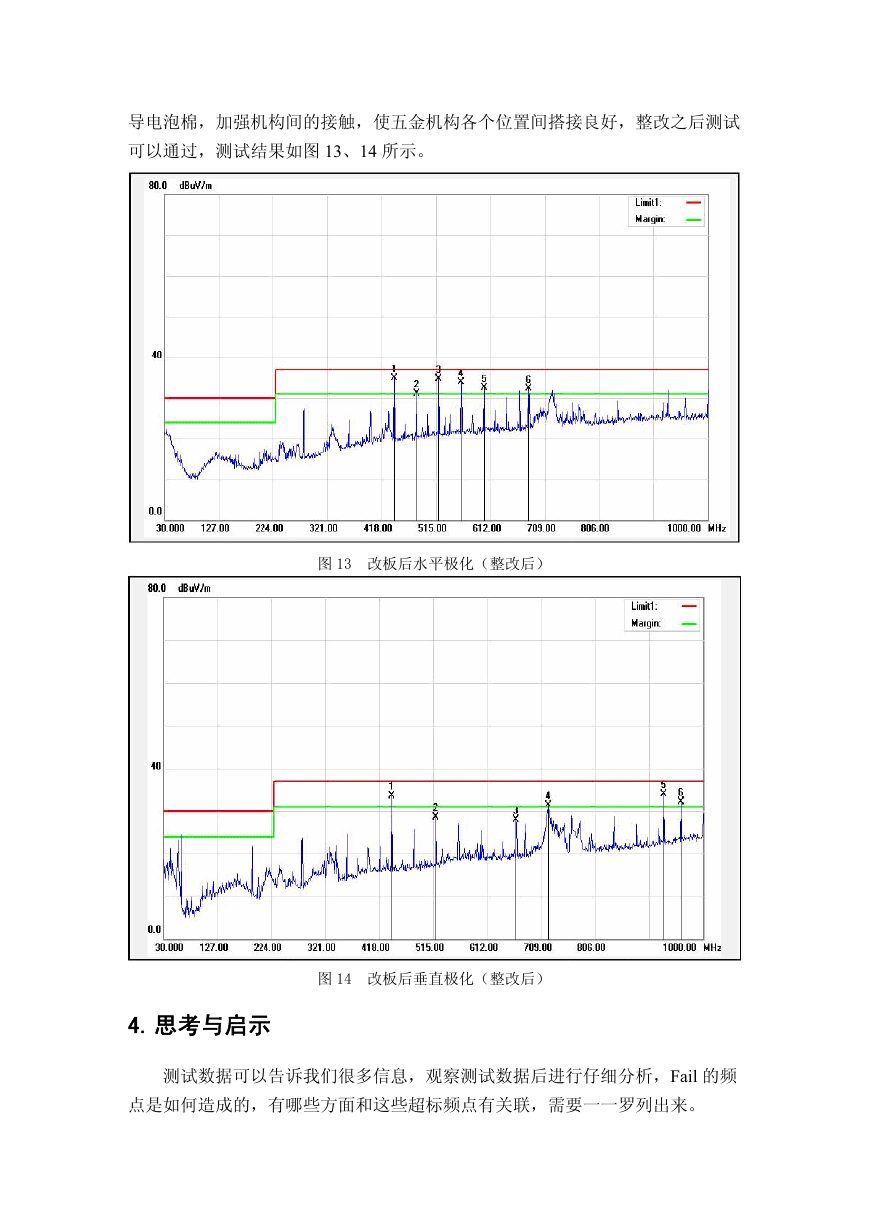

该产品的内部机构采用五金,外部采用塑胶外壳,五金机构表层均镀了绝缘漆,

金属机构的搭接位置,采用螺丝组装,阻抗很高,使用刀片刮开绝缘漆且缝隙加

�

导电泡棉,加强机构间的接触,使五金机构各个位置间搭接良好,整改之后测试

可以通过,测试结果如图 13、14 所示。

图 13 改板后水平极化(整改后)

图 14 改板后垂直极化(整改后)

4. 思考与启示

测试数据可以告诉我们很多信息,观察测试数据后进行仔细分析,Fail 的频

点是如何造成的,有哪些方面和这些超标频点有关联,需要一一罗列出来。

�