2010 正

第 l0期

仪 表 技 术 与

Instrument Technique

2Ol0

No.1O

基 于 FPGA 的 SD —SDI视 频 转 换 接 口 的设 计

(1.中国科学院长春光学精密机械与物理研 究所 ,吉林长春 130033;2.中国科学院研究生院 ,北京 100039)

祁 超 ,魏仲 慧 ,何 昕 ,梁 国龙 一,郭 志 军

摘要 :以 FPGA为主控 芯片,设计一款数 字视 频接 口转换 设备 ,完成 SD—SDI(标 准清晰 度 一串行数 字接 口)视 频到

Camera Link接 口视 频 的 转 换 。 通 过 对摄 像 机 输 出的 ITU—R BT.656格 式 数 据 进 行 采 集 、色彩 空 间 变换 、视 频 去 隔 行 处 理

等 操 作 ,实现 将 SD —SDI接 口传 输 的 隔行 显 示 的 视 频 采 用 Camera Link接 口方 式逐 行 输 出 。整 个 系统 设 计 灵 活 ,集 成 度

高 ,以较 少 的硬 件 资 源 完成 了高质 量 的视 频接 口转 换 。

关 键 词 :串行 数 字接 口 ;去 隔行 ;乒乓 缓 存 ;视 频 转 换

中 图 分 类 号 :TN941.1

文 献 标 识 码 :B

文 章 编 号 :1002—1841(2010)10—0063—03

Design of SD — SDI Video Conversion Interface Based on FPGA

(1.Changchun Institute of Optics,Fine Mechanics and Physics,Chinese Academy of Sciences,Changchun 130033,China;

QI Chao 一,WEI Zhong—hui ,HE Xin’,LIANG Guo—long 一,GUO Zhi-jun ’!

2.Graduate School of Chinese Academy of Sciences,Beijing 100039,China)

A bstract:Based on the host chip of FPGA ,this paper designed digital video conversion equipment,and completed the eonver—

sion from video with SD — SDI interface to camera link interface.After collecting the ITU—R BT.656 form at data from the camera,

convening the color space,de—interlacing and other operation,circuit implemented the transmission of interlaced—scan video with SD

— SDI interface to progressive video with camera link interface.W ith much flexibility,high integration and less hardware resources,

the whole system completed a high—quality video conversion.

Key words:serial digital interface;de—interlacing;ping—pong operation;video conversion

1 视 频 格 式 简 介

1.1 SDI接 口视 频 格 式

上 SD—SDI有 效 视 频 ,经 过 补 偿 后 的 SD —SDI视 频 流 连 同视 频

有 效 标 识 信 号 一 起 进 入 解 串器 GSI560A.

串行数字 接 口(Serial Digital Interface,SDI)是 由美 国 电影

电视工程师协会 (SMPTE)制定 的,用单根 同轴 电缆 来 串行传 输

无压缩 的视/音 频数 据 的一 种 接 口,传输 的视 频 符合 ITU—R

BT.656标 准 。

SD—SDI(Standard Definition SDI,标准清 晰度 SDI),支持 的

串行 数 据 传 输 率 有 143 Mbit/s、177 Mbit/s、270 Mbit/s及 360

Mbit/s.通常提到的 SD—SDI均 指 目前使 用最 多 的 270 Mbit/s

传输标 准 ,视频 格式 为 720×480i/576i,场频 50 fps,数 据 采用

Y/Cb/Cr色 彩 空 间 4:2:2分 量 编 码 。 主 要 用 于 数 字 广 播 演 播

室环境 下传输标 准清 晰度数字 电视 信号 (SDTV)。

1.2 Camera Link接 口传 输 协 议

Camera Link是一种适合数字 图像 信号在相 机 和图像采 集

卡间传输 的接 口协议 。其标准 由美 国 National Semiconductor公

司基于其 Channel Link技术 ,联 合数 家工业相 机及采集 卡制 造

商 共同制定 。Camera Link接 口协议 以 LVDS(低压 差分 信 号)

信 号来完成相机 和图像采集卡 的数 据传输 和通信 ,并定义有 标

准 的接 口器 件 。

2 系 统 方 案设 计

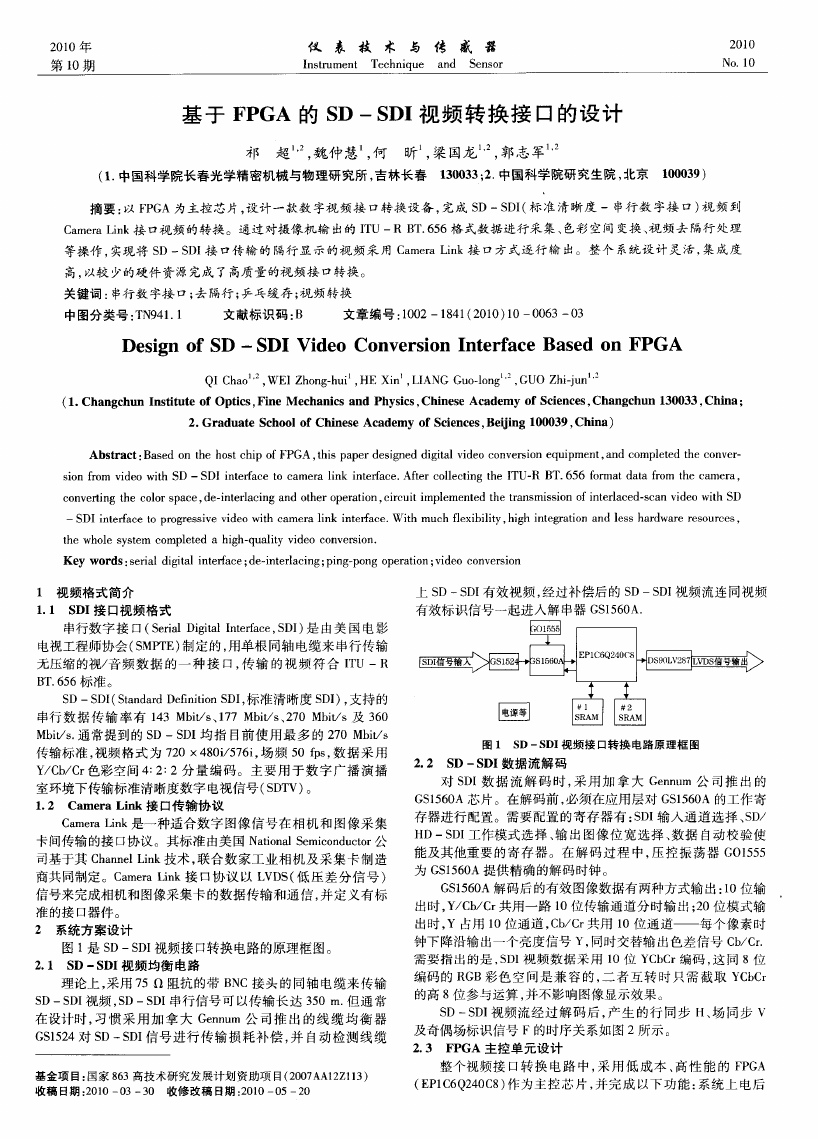

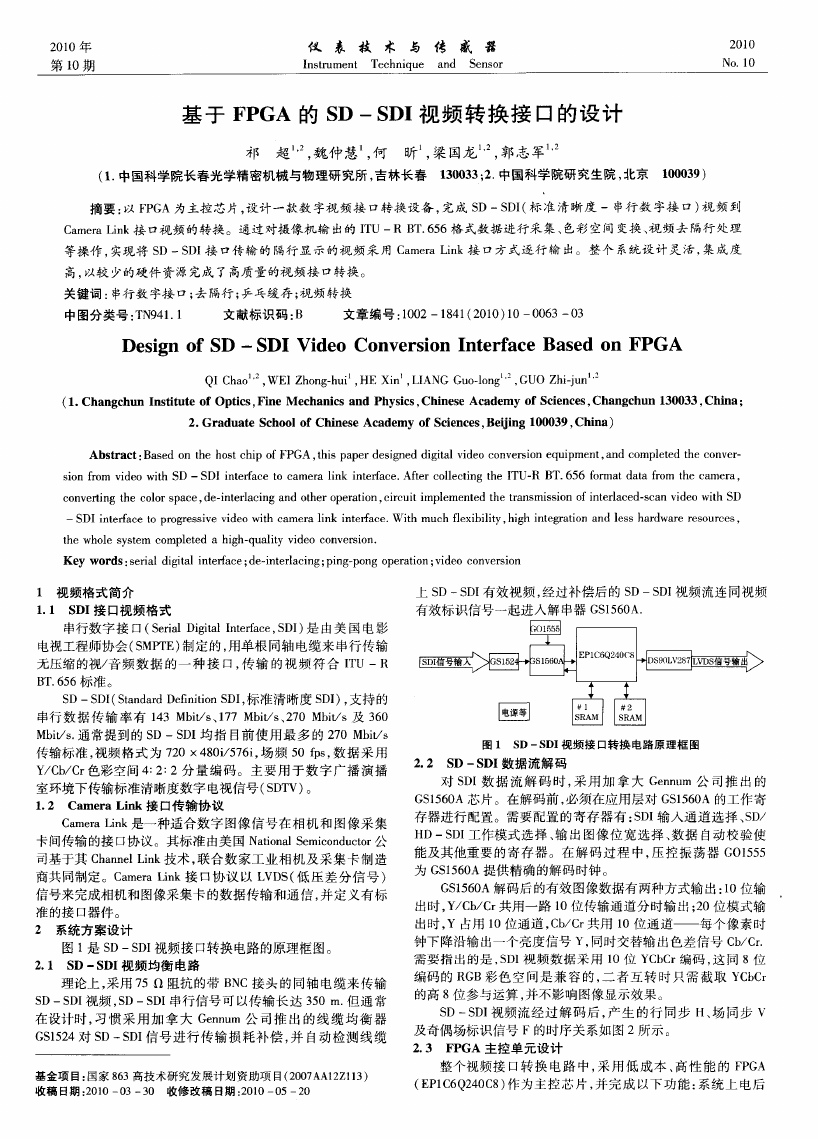

图 1是 SD—SDI视频接 口转换 电路 的原理框 图。

2.1 SD —SDI视 频 均衡 电路

理 论 上 ,采 用 75 n 阻 抗 的 带 BNC接 头 的 同 轴 电 缆 来 传 输

SD—SDI视频 ,SD—SDI串行信号可 以传输长 达 350 m.但通 常

在设计时 ,习 惯采 用 加 拿 大 Gennum公 司推 出 的线 缆 均衡 器

GS1524对 SD—SDI信号 进行 传输 损耗 补偿 ,并 自动检测 线 缆

基 金 项 目 :国家 863高 技 术研 究 发展 计 划 资 助 项 目(2007AAI2Z113)

收 稿 日期 :2010—03—30 收 修 改 稿 日期 :2010—05—20

图 1 SD —SDI视 频 接 口 转 换 电 路 原理 框 图

2.2 SD —SDI数 据 流 解 码

对 SDI数 据 流 解 码 时 ,采 用 加 拿 大 Gennum 公 司 推 出 的

GS1560A芯 片。在解码前 ,必须在应用层对 GS1560A的工 作寄

存 器 进 行 配 置 。需 要 配置 的 寄 存 器 有 :SDI输 入 通 道 选 择 、SD/

HD—SDI工作模式选择 、输 出图像位 宽选择 、数 据 自动校验 使

能及其他重要 的寄存 器 。在 解码 过程 中 ,压控 振荡 器 G01555

为 GSI560A提供精确 的解码 时钟 。

GS1560A解码后 的有 效图像数 据有 两种方式输出 :10位输

出时 ,Y/Cb/Cr共 用 一 路 10位 传 输 通 道 分 时 输 出 ;20位 模 式 输

出时 ,Y 占用 10位 通 道 ,Cb/Cr共 用 10位 通 道 —— 每 个 像 素 时

钟下降沿输 出一个亮度信号 Y,同时交替输 出色差 信号 Cb/Cr.

需 要 指 出的 是 ,SD1视 频 数 据 采 用 10位 YCbCr编 码 ,这 同 8位

编 码 的 RGB彩 色 空 间 是 兼 容 的 ,二 者 互 转 时 只 需 截 取 YCbCr

的高 8位参与运算 ,并不影 响图像显示效果 。

SD—SDI视 频 流 经 过 解 码 后 ,产 生 的行 同 步 H、场 同 步 V

及 奇偶 场 标 识 信 号 F的 时 序关 系 如 图 2所 示 。

2.3 FPGA 主 控 单 元 设 计

整个视频接 口转换 电路 中 ,采用 低 成本 、高性 能 的 FPGA

(EP1C6Q240C8)作 为 主 控 芯 片 ,并 完 成 以 下 功 能 :系 统 上 电 后

�

Instrum ent Technique and Sensor

0et.2010

场

场

行同步 H

F=l时 .传 输 的 是 奇 场 (奇 数 行 ),反 之为 偶 场 (偶 数 行 );V=l时 .为 场 消

隐状 态,反 之为场有效状态 ;H:1时,为行 消隐状态 .反之为行有效状态

图 2 SD —SDI视 频解 码 后 的 同步 时 序 图

首 先 完 成 对 GS1560A工 作 寄存 器 的 配 置 ;完 成 对 视 频 数 据 的 色

彩空 间转换及对 SRAM 的乒乓缓存控制 ;完 成对 SD—SDI视频

的去隔行处理 、产 生 Camera Link接 口协议的同步信号及 LVDS

发 送 模 块 时 序 控 制 。

图 3是 在 FPGA 内 部设 计 的各 功 能模 块 框 图 。

数 ,因 此运 算结 果 需 将 负 数 取 为 0,超 过 255 的正 数 取 为 255。

这样做虽然会引入误差 ,但并 不影 响图像显示效果 。

2.3.3 SRAM 乒 乓缓 存 控 制单 元

该模块 的任 务是 协 调 两个 SRAM 的读 写操 作 ,在 第一 块

SRAM 被写入 数 据 的 同时 ,第 二 块 SDRAM 被 读 出数 据 以供

LVDS发送模块 发送 。当第一块 SRAM 存入完整 的一 帧图像数

据 (包括 奇 、偶 两 场 )后 ,两块 SRAM 交 换 读 写操 作 ,第 一 块

SRAM 由被写人数据转变为被读 出数据 ,第二 块 SRAM 由被读

出数据转变为被写人数据 ,当第二块 SRAM 存入完整 的一帧图

像数据 (包 括奇 、偶两场 )后 ,再 次切换两块 SRAM 的读写操 作 ,

如此循环 。乒乓缓存控 制模块 利用 了奇 偶场标 识信号 F及 同

步信号 V来完成对两个 SRAM控制器 的读写状态 的切换。

2.3.4 SD—SDI视 频 去 隔行 处 理 及 Camera Link视 频 时序 控 制

为了同传统 的模拟 电视兼 容 ,SDI接 口在传输 数字视 频时

也采用分奇/偶 场传输 ,即一帧 图像先传输所有 的奇数行 f即奇

数场 ),然后传输所有 的偶数行 (即偶 数场 ),依 次循环 。因此 ,

当分场传输 的视频 同计算机显示 器 、平板 电视等逐行 扫描的显

示设备接 口时,必须 完成视 频 的去隔行 处理 ,即将奇 偶场 合并

成 一帧 完整 的 图像 后 才能输 出,否 则无 法完成 正确 的图像显

刀 。

设计 中 ,采用 在 乒乓 操 作时 跳跃 式 读取 SRAM 来 完 成对

SDI视频 的去隔行处理 。如 图 4所示 ,在 奇场数 据存储 区读取

第 2N+1行 (N =0,1,2… )数 据 后 ,跳 跃 到 偶 场 数 据 存 储 区 读

取第 2N+2行 的数据 ,然后再返 回奇场 数据存储 区读取第 2N

+3行数据 ,接着再跳 跃到偶 场数据 存储 区读 取第 2N+4行数

据 ,如此循环 ,直至读完一帧图像 数据 。

解 串器 GS1560A对外提供 一个 SPI(Serial Peripheral Inter—

face)总线控制接 口,通 过 SPI接 口,主机对 GS1560A 内部 的工

作寄存器进行设置 ,从而完成 对其 工作模式 的选择 。

在配置 GS1560A工作 寄存 器时 ,FPGA首先写入 1个 16位

的命令字 (即 GS1560A的寄存器地址 )到 SDIN引脚 ,然后 紧跟

着写入 1个 16位 的控制 字 (即设置 相应 寄存器 的状 态值 );所

有对 GS1560A的读 写访 问都 是在 片选 CS=0及 外部提供 的 串

行同步时钟(频率_厂≤6.6 MHz)条件下完成的。

色彩空问 变换 模 块 的作 用 是 将 GS1560A解 码 器输 出 的

YCbCr值转换成对应 的 RGB值。 由于 ITU—R BT.656数据 流

采用 4:2:2的 YCbCr数 据格式 ,即相邻两个像素点 的色差分量

复用同一个 cb、cr值 ,因此 在 色 彩空 间 变换 时 ,必须 先 将 Y/

Cb/Cr由4:2:2变为 4:4:4的格式 ,使每个 像素 的 Y/Cb/Cr值

独立开来 ,然后再转换成独立 的 RGB值。转换公式 如下 :

由于 电路仅通过简单 的存储控 制 ,避免 了复杂 的去 隔行算

法处理 ,使得 FPGA硬件资源的消耗达到了最小化。

去隔行处理完成 了视频 以 Camera Link接 口传输要求 的数

据组织方式 ,为使 SD—SDI视频通过 Camera Link接 13输 出,还

必须产生符合该 协议要 求 的帧 同步信 号 Frame和行 同步信 号

Line,这些信 号是 由 GS1560A输 出的奇/偶 场标识 F、场 同步 V

图 4 SDI视 频 的去 隔 行 处 理 示 意 图

-

179. 45

由于 在 FPGA 中进 行 浮 点 运 算 比较 困难 ,因 此 需 将 上 式 中

的各 个 系 数 变 换 成 整 数 后 再 进 行 运 算 ,方 法 是 先 将 各 个 系 数 放

大 1 024倍 ,得 出最 后 的 R、G、B 结 果 后 再 除 以 1 024,如 式 (2)

[ Rj× 。24=【1 02 0 1—4 3s6 Jl Y:?】+[- ;1 83 :7 6 ]

(2)

设 计 时 ,调 用 Mega Core中 的 IP核 ALTMULT_ADD 来 完 成

Y/Cb/Cr的乘加运算 ,得 到的结 果加 上常 数项 后右移 10位 完

成除法 运算 ,得到最后的 RGB值 。由于 R、G、B均为 8位 ,取值

范围为 0到 255,而运算过程 可能会生成 负数和超过 255的正

及 行 同 步 H来 控 制产 生 的 。

3 方 案 验 证 及 实 验 结 果

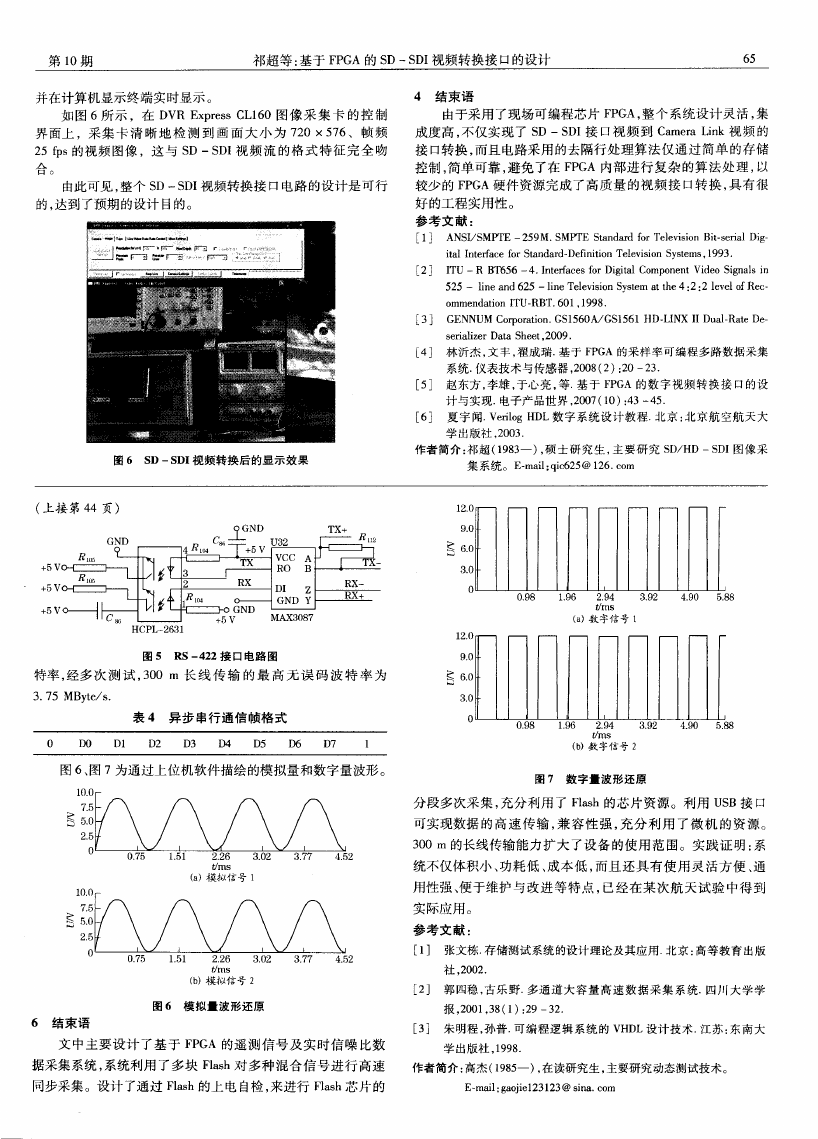

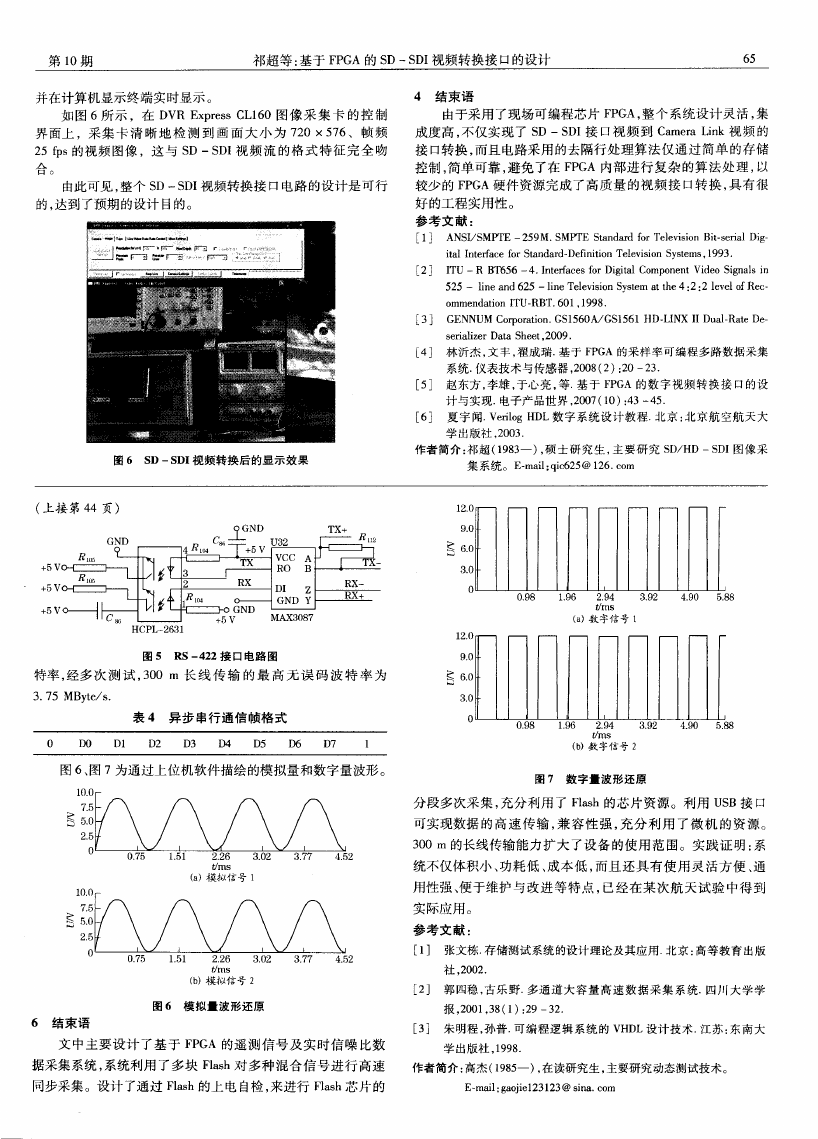

系 统 方 案 的 验 证 方 法 如 图 5所 示 。

器 蓬星

= = = >

LVDS流

机

图 5 方 案 验证 方 法示 意 图

采用 DSR一6000PL型摄像机采集现实景物 ,相机输 出符合

ITU—R BT.656协议 的 SD—SDI视频 流经 同轴 电缆传 输 至视

频转换 电路 ;在将 SDI串行 视频 数据 转换 为 Camera Link接 口

视频后 ,由 Camera Link线 缆将之传输 至 Pc机上 的图像 采集卡

DVR Express CL160,由采集卡完成对 Cam era Link视频 的采集

�

第 10期

祁超等 :基 于 FPGA的 SD—SDI视频转换接 口的设计

65

并在计算机显示终端实时显示 。

4 结 束 语

如 图 6所 示 ,在 DVR Express CL160图像 采 集 卡 的控 制

界 面上 ,采 集 卡 清 晰 地 检 测 到 画 面 大 小 为 720×576、 帧 频

25 fps的视频 图像 ,这 与 SD—SDI视频 流 的格式 特征 完 全 吻

由于 采 用 了现 场 可 编程 芯 片 FPGA,整 个 系 统 设 计 灵 活 ,集

成度高 ,不仅 实现了 SD—SDI接 口视频 到 Camera Link视频 的

接 口转换 ,而且电路采用的去隔行处 理算法 仅通过简单 的存储

合 。

由此 可 见 ,整个 SD—SDI视 频 转 换 接 口电 路 的 设 计 是 可 行

的 ,达 到 了 预期 的设 计 目的 。

图 6 SD —SDI视 频 转 换 后 的 显 示 效 果

(上 接 第 44页 )

0

l05 L一 [

— J —— --1

—

L

+5V

—

—

+5V

+5V

—

l∞

【

I l

. . . 一

C

2

广 —

RX

= 二二 ]_O

V

VCC A RO B

DI

Z

GND Y

MAX3087

图 5 RS一422接 口 电路 图

特率 ,经多 次测 试 ,300 m 长 线 传 输 的最 高 无 误 码 波 特 率 为

3.75 M Byte/s.

表 4 异 步 串行 通 信 帧 格 式

0

DO D1

D2 D3 IM D5 D6 D7

1

图 6、图 7为通过上位机软件描绘 的模 拟量和数字量波形 。

控 制 ,简单 可靠 ,避免 了在 FPGA 内部 进行 复杂 的算 法处理 ,以

较少的 FPGA硬件资源完成 了高质量 的视 频接 口转 换 ,具有很

好的工程实用性 。

参 考 文 献 :

[1] ANSUSMPTE一259M.SMF'TE Standard for Television Bit—serial Dig—

ital Interface for Standard—Definition Television Systems,1993.

[2] ITu—R BT656—4.Interfaces for Digital Component Video Signals in

525 一 line and 625一line Television System at the 4:2:2 level of Rec—

ommendation tTU—RBT.601,1998.

[3] GENNUM Corporation.GS1560A/GS1561 ttD·LINX II Dual—Rate De—

serializer Data Sheet,2009.

[4] 林沂杰 ,文 丰,翟成瑞.基于 FPGA的采样 率可编程多路数据采集

系统.仪表技术与传感器 ,2008(2):20—23.

[5] 赵东方 ,李雄 ,于心亮 ,等.基 于 FPGA的数 字视频转 换接 口的设

计与实现.电子产品世界 ,2007(10):43—45.

[6] 夏 宇 闻.Verilog HDL数字 系统 设计教 程.北京 :北 京航空航 天大

学 出 版 社 ,2003.

作 者 简 介 :祁 超 (1983一 ),硕 士 研 究 生 ,主 要 研 究 SD/HD —SDI图像 采

集 系统 。E.mail:qic625@ 126.con

t/Ills

(a)数 字 信 号 1

m s

(b)数 字 信 号 2

图 7 数 字 量 波 形 还 原

l

1O 0

7.6

兰5.0

2.5

O

6 结束 语

0.75

1.51

2.26

t/m s

3.O2

3 77

4 52

(S)模 拟 信 号 1

分 段 多 次 采 集 ,充 分 利 用 了 Flash的 芯 片 资 源 。利 用 USB 接 口

可实现数据 的高 速传 输 ,兼 容性 强 ,充 分利 用 了微 机 的 资源 。

300 in的长线 传输 能力扩 大 了设 备 的使 用范 围。实践证 明 :系

统不仅 体积小 、功 耗低 、成本 低 ,而且 还具 有使 用灵 活方 便 、通

用性强 、便于维护 与改进 等 特点 ,已经 在某次 航天 试验 中得 到

实 际应 用 。

参 考 文 献 :

0.75

1.51

2 26

t/m s

3.O2

3.77

4.52

(b)模 拟 信 号 2

图 6 模 拟 ■ 波 形 还 原

[1] 张文栋 .存储测试 系统 的设计理论及其应用.北 京 :高等教育 出版

社 .2002.

[2] 郭 四稳 ,古乐 野.多 通道 大容量 高速 数据 采集 系统.四川大 学学

报 ,2001,38(1):29—32.

[3] 朱明程 ,孙普.可编 程逻辑 系统的 VHDL设计技 术.江苏 :东 南大

文 中主要设 计 了基于 FPGA的遥测 信号及 实 时信 噪 比数

学 出 版 社 ,1998.

据采集系统 ,系统 利用 了多块 Flash对多 种混合 信 号进行 高速

作者简介 :高杰(1985一 ),在读研 究生 ,主要研究 动态测试技术 。

同步 采 集 。设 计 了 通 过 Flash的 上 电 自检 ,来 进 行 Flash芯 片 的

E—mail:gaojie123123@ sina.con

�