1. Introduction

2. General description

3. Features

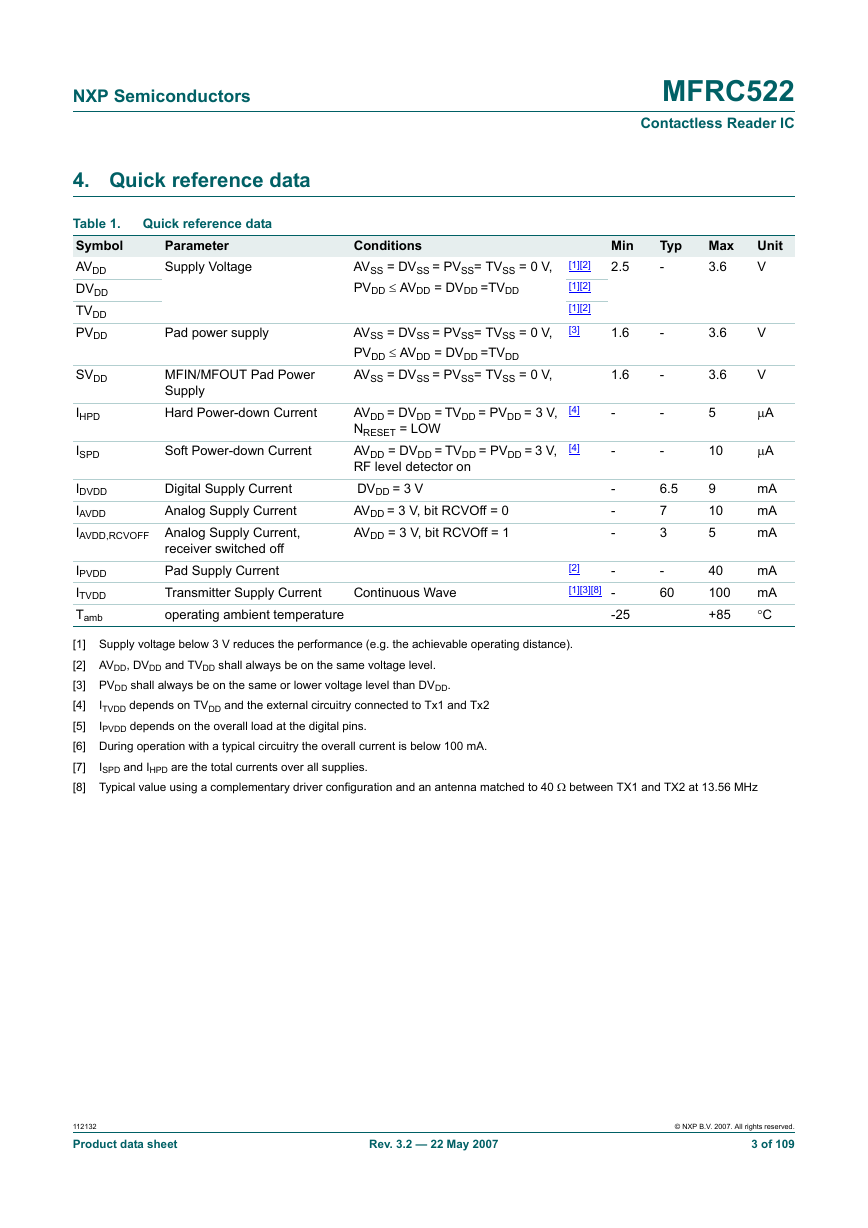

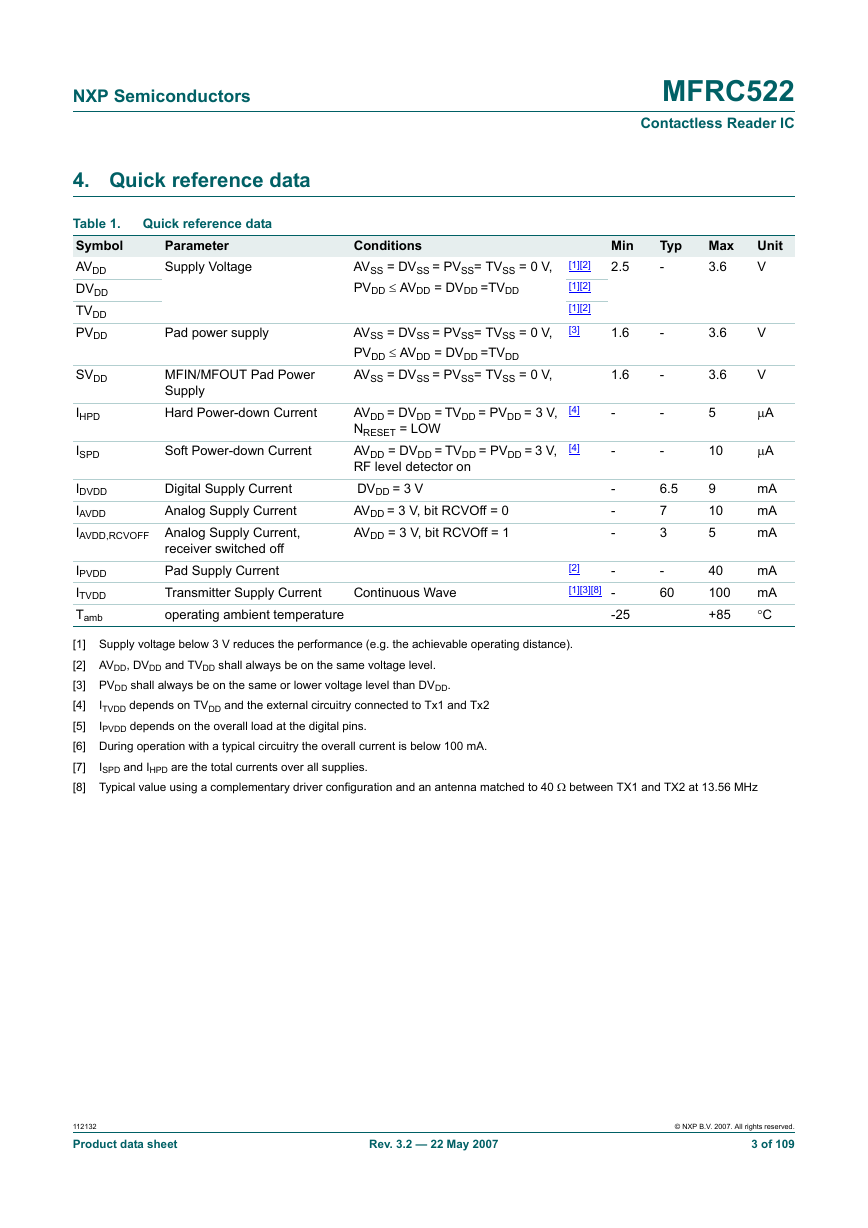

4. Quick reference data

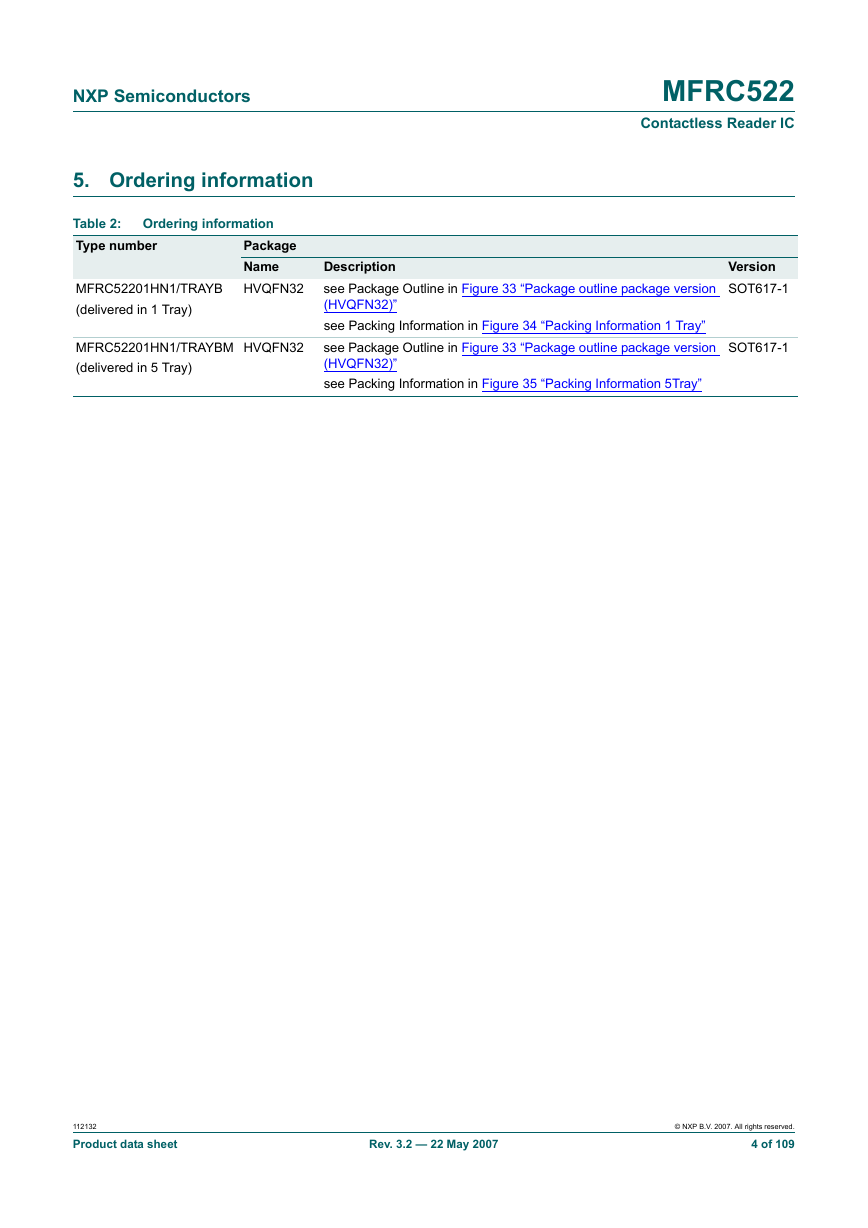

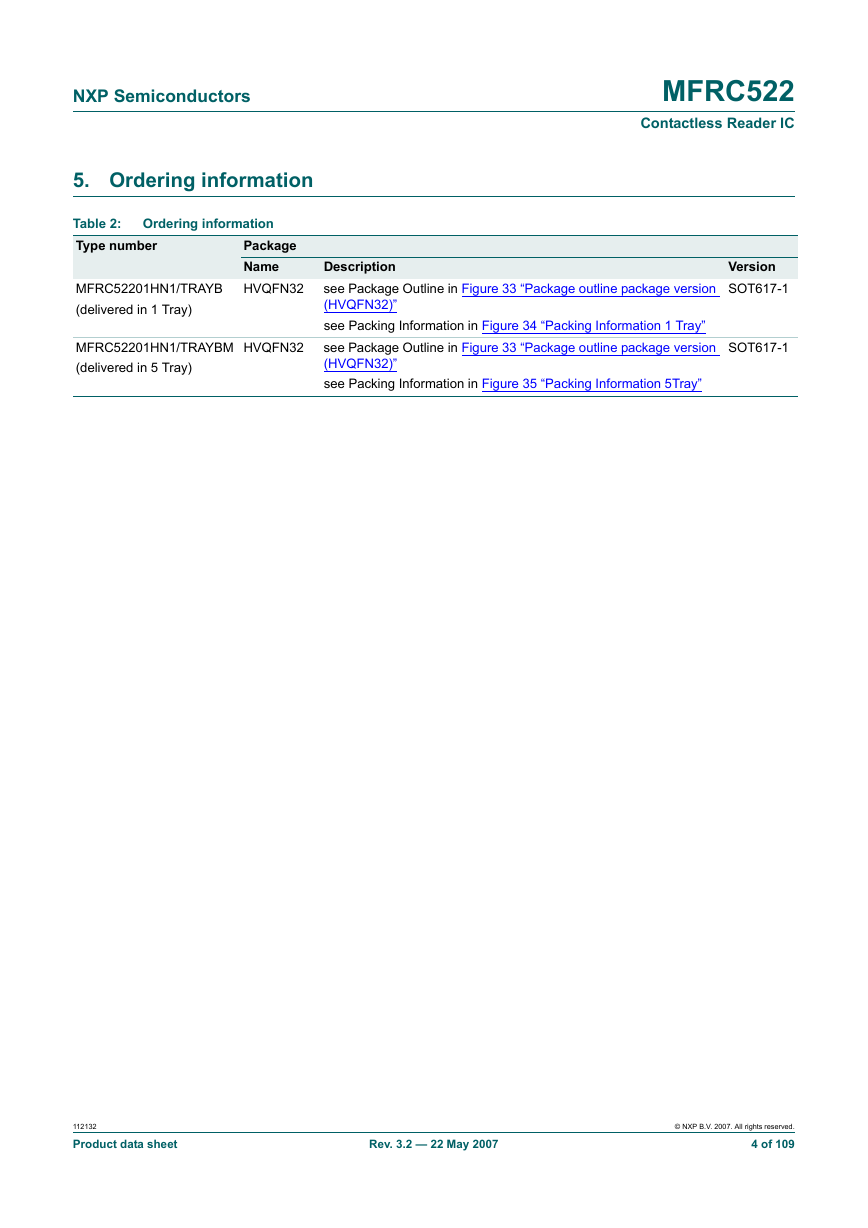

5. Ordering information

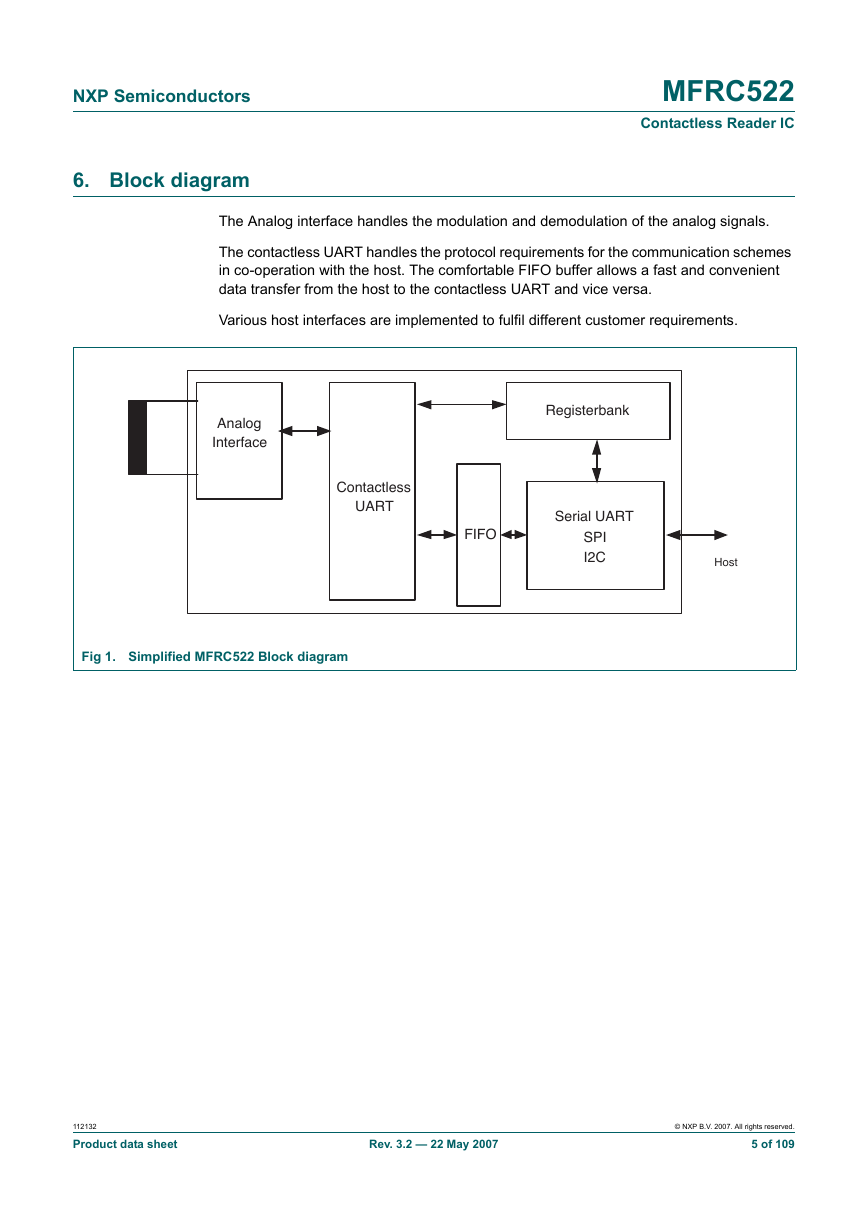

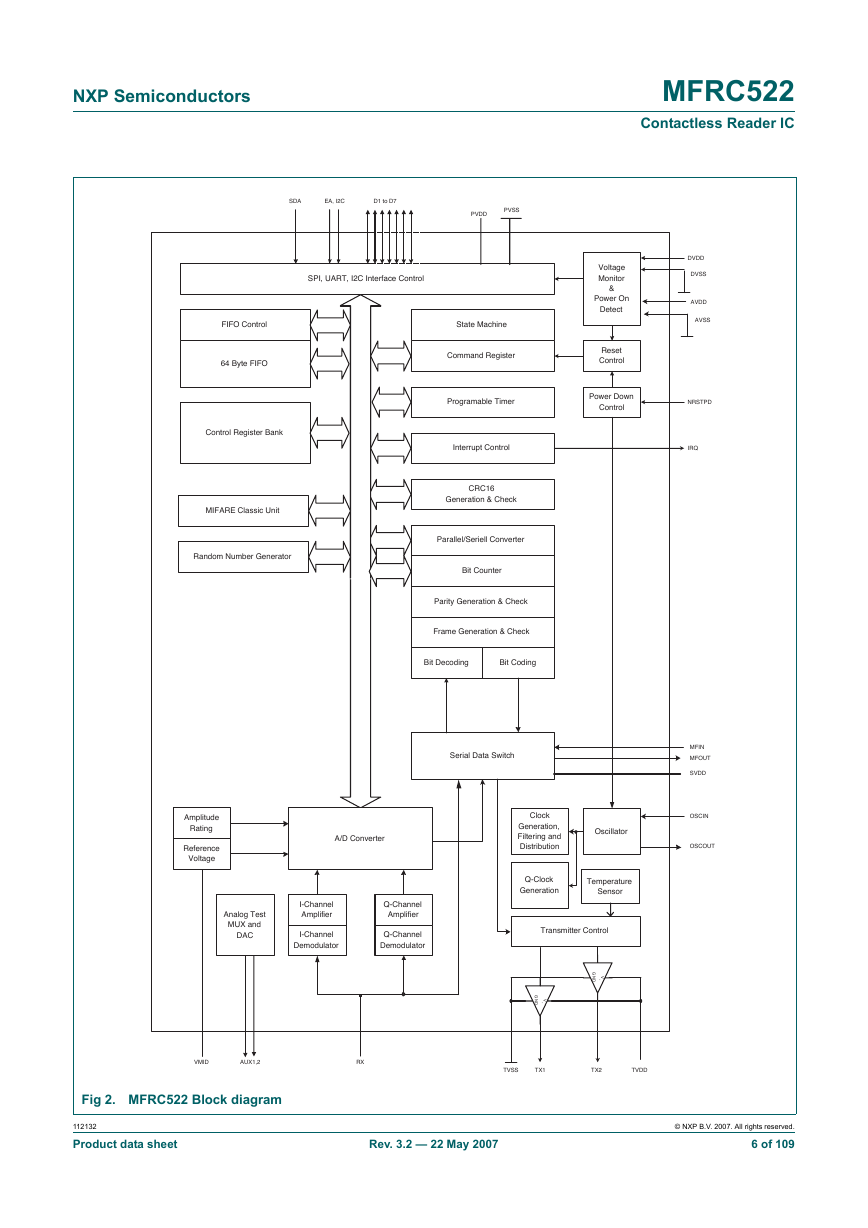

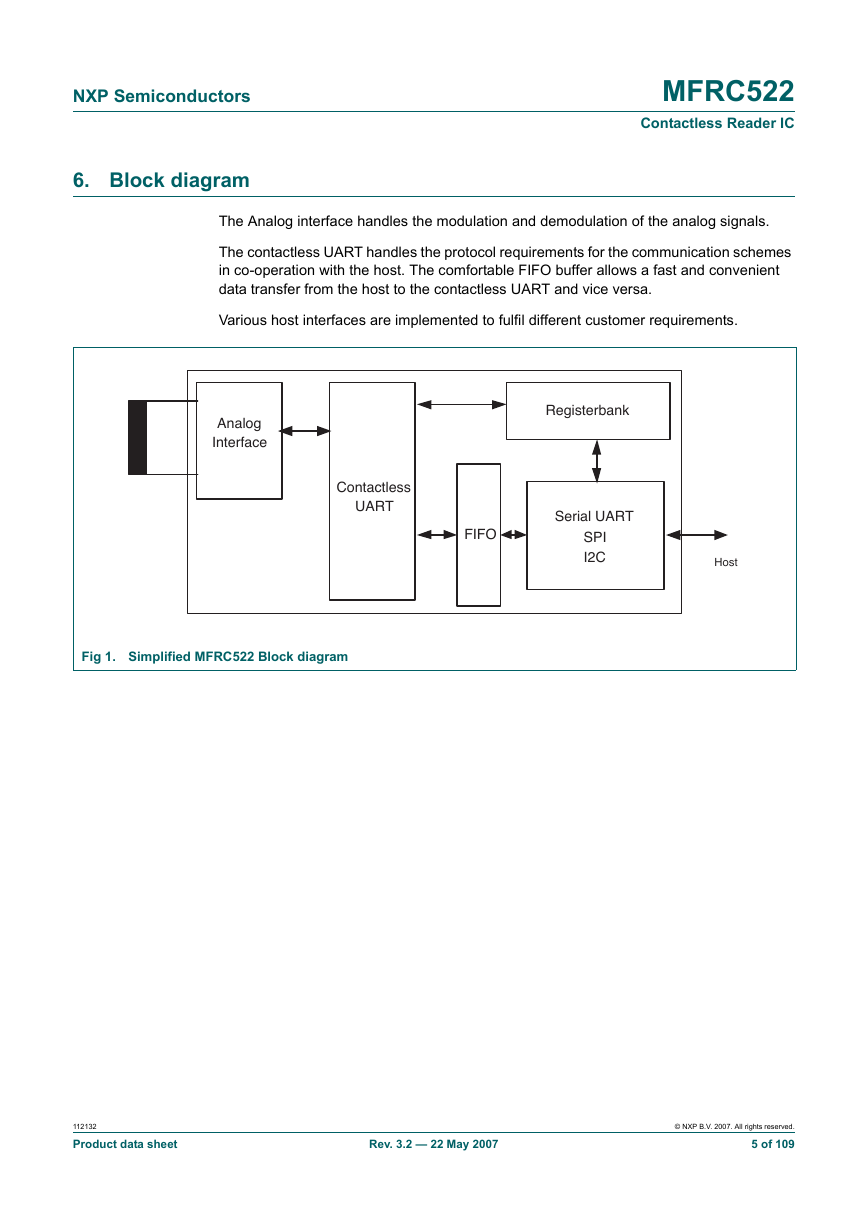

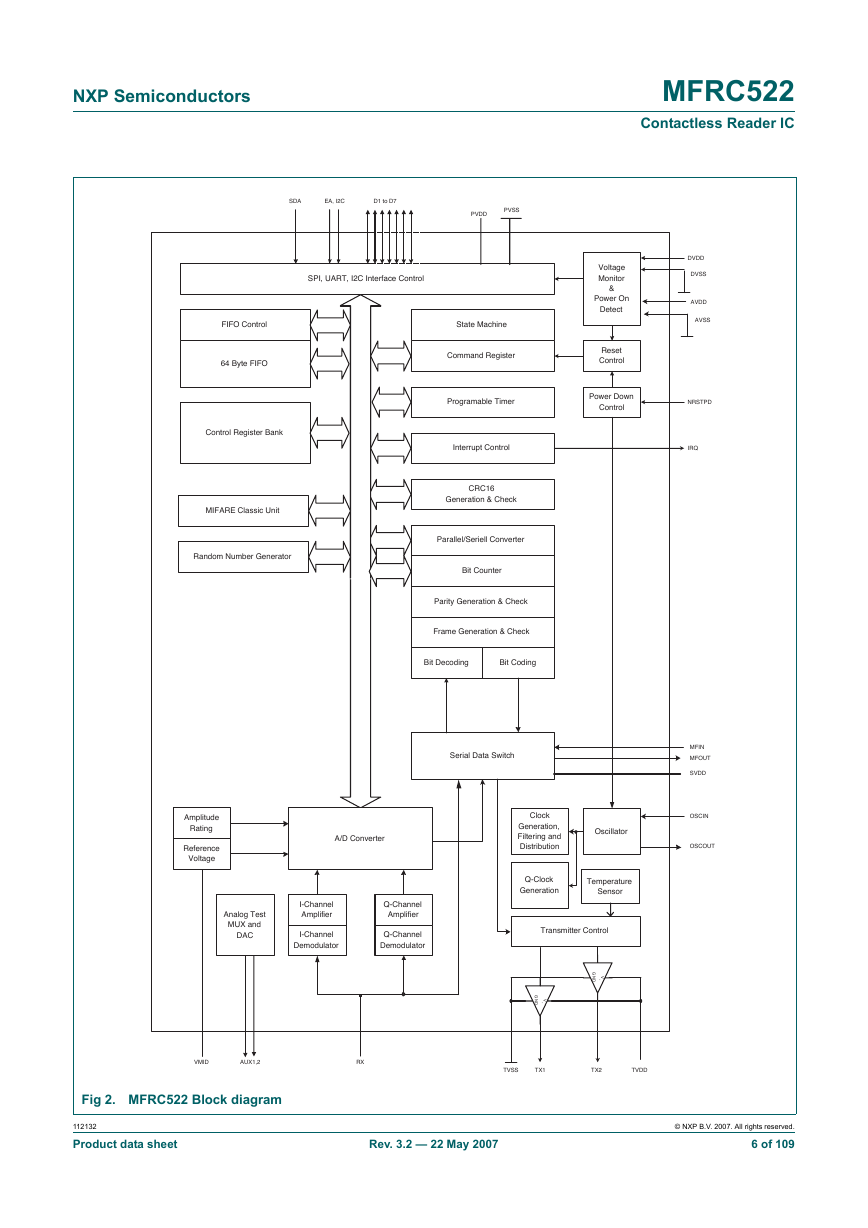

6. Block diagram

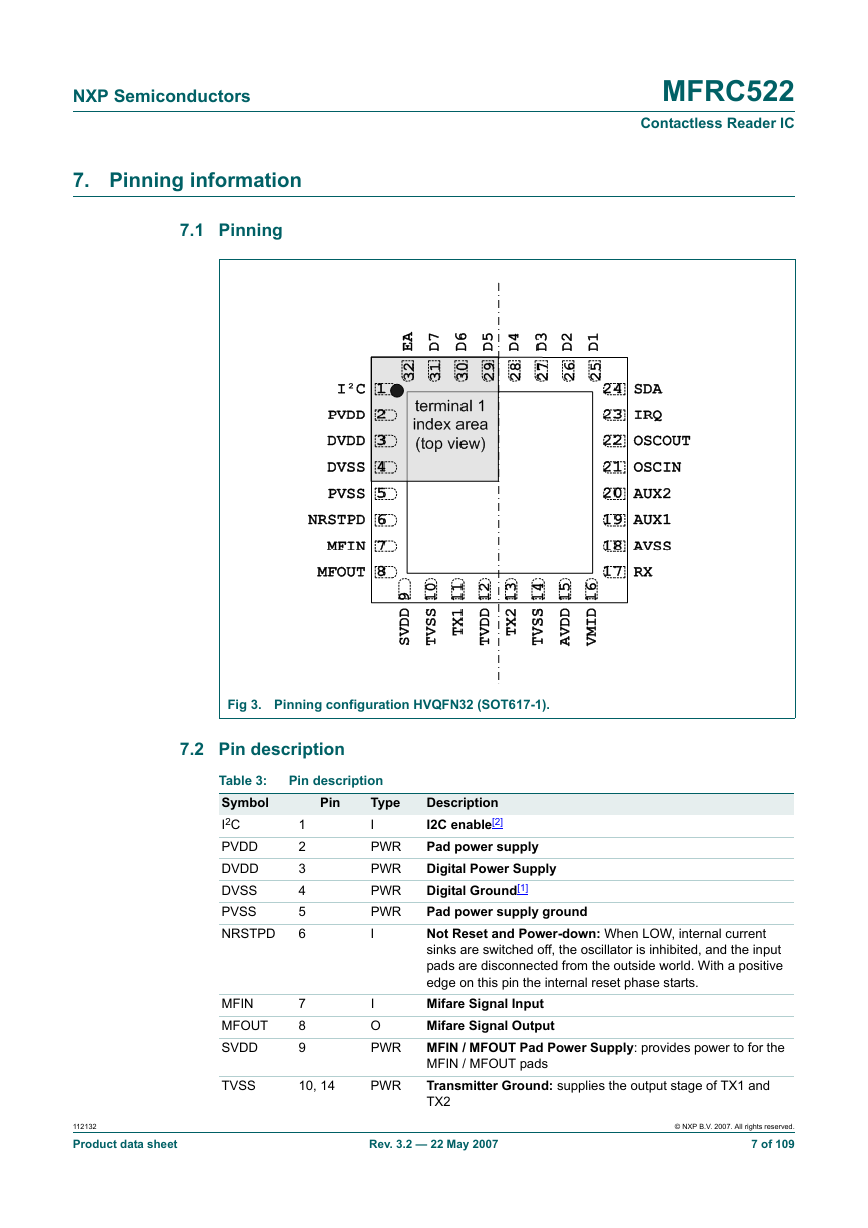

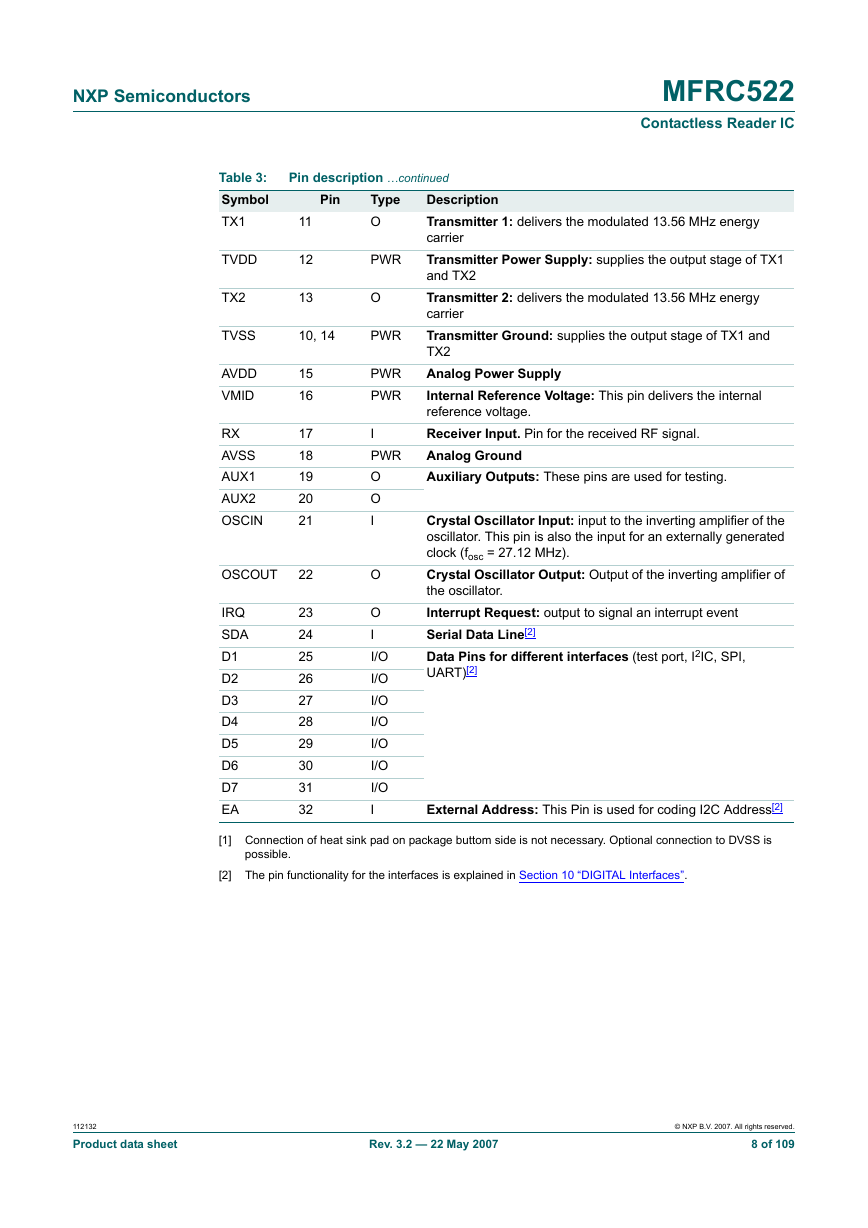

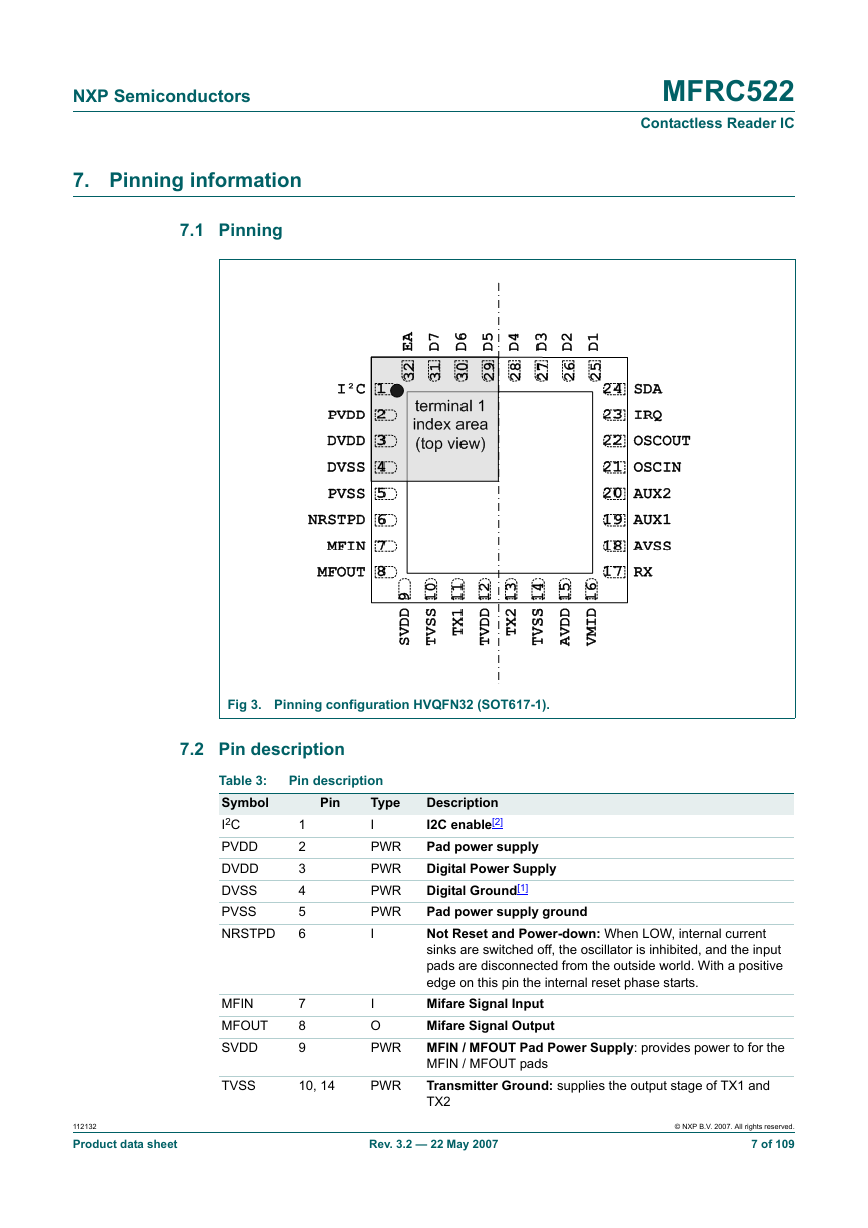

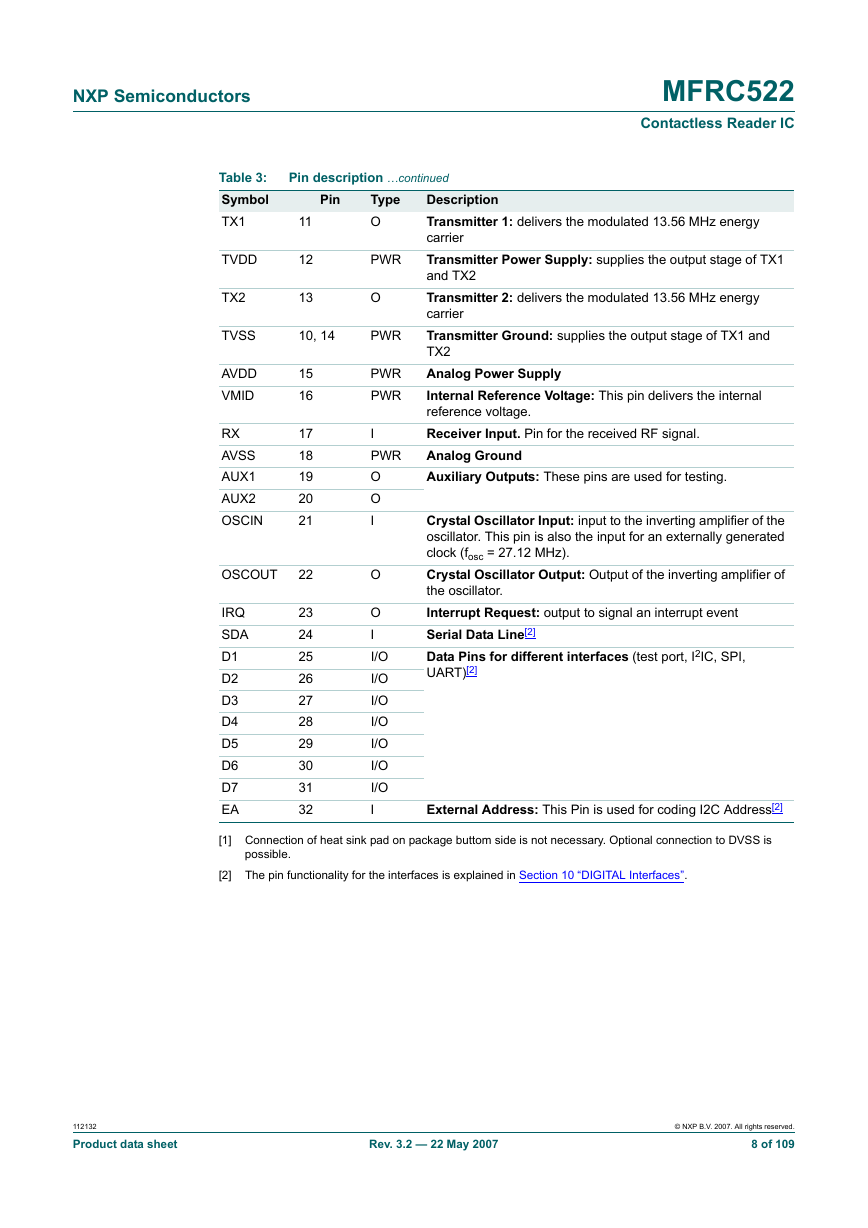

7. Pinning information

7.1 Pinning

7.2 Pin description

8. Functional description

9. MFRC522 Register SET

9.1 MFRC522 Registers Overview

9.1.1 Register Bit Behavior

9.2 Register Description

9.2.1 Page 0: Command and Status

9.2.1.1 Reserved

9.2.1.2 CommandReg

9.2.1.3 CommIEnReg

9.2.1.4 DivIEnReg

9.2.1.5 CommIRqReg

9.2.1.6 DivIRqReg

9.2.1.7 ErrorReg

9.2.1.8 Status1Reg

9.2.1.9 Status2Reg

9.2.1.10 FIFODataReg

9.2.1.11 FIFOLevelReg

9.2.1.12 WaterLevelReg

9.2.1.13 ControlReg

9.2.1.14 BitFramingReg

9.2.1.15 CollReg

9.2.1.16 Reserved

9.2.2 Page 1: Communication

9.2.2.1 Reserved

9.2.2.2 ModeReg

9.2.2.3 TxModeReg

9.2.2.4 RxModeReg

9.2.2.5 TxControlReg

9.2.2.6 TxASKReg

9.2.2.7 TxSelReg

9.2.2.8 RxSelReg

9.2.2.9 RxThresholdReg

9.2.2.10 DemodReg

9.2.2.11 Reserved

9.2.2.12 Reserved

9.2.2.13 MfTxReg

9.2.2.14 MfRxReg

9.2.2.15 Reserved

9.2.2.16 SerialSpeedReg

9.2.3 Page 2: Configuration

9.2.3.1 Reserved

9.2.3.2 CRCResultReg

9.2.3.3 Reserved

9.2.3.4 ModWidthReg

9.2.3.5 Reserved

9.2.3.6 RFCfgReg

9.2.3.7 GsNReg

9.2.3.8 CWGsPReg

9.2.3.9 ModGsPReg

9.2.3.10 TMode Register, TPrescaler Register

9.2.3.11 TReloadReg

9.2.3.12 TCounterValReg

9.2.4 Page 3: Test

9.2.4.1 Reserved

9.2.4.2 TestSel1Reg

9.2.4.3 TestSel2Reg

9.2.4.4 TestPinEnReg

9.2.4.5 TestPinValueReg

9.2.4.6 TestBusReg

9.2.4.7 AutoTestReg

9.2.4.8 VersionReg

9.2.4.9 AnalogTestReg

9.2.4.10 TestDAC1Reg

9.2.4.11 TestDAC2Reg

9.2.4.12 TestADCReg

9.2.4.13 Reserved

10. DIGITAL Interfaces

10.1 Automatic m-Controller Interface Type Detection

10.2 SPI Compatible interface

10.2.1 General

10.2.2 Read data

10.2.3 Write data

10.2.4 Address byte

10.3 UART Interface

10.3.1 Connection to a host

10.3.2 Selection of the transfer speeds

10.3.3 Framing

10.4 I2C Bus Interface

10.4.1 General

10.4.2 Data validity

10.4.3 START and STOP conditions

10.4.4 Byte format

10.4.5 Acknowledge

10.4.6 7-BIT ADDRESSING

10.4.7 Register Write Access

10.4.8 Register Read Access

10.4.9 HS mode

10.4.10 High Speed Transfer

10.4.11 Serial Data transfer Format in HS mode

10.4.12 Switching from F/S to HS mode and Vice Versa

10.4.13 MFRC522 at Lower Speed modes

11. Analog Interface and Contactless UART

11.1 General

11.2 TX Driver

11.3 Serial Data Switch

11.4 MFIN/MFOUT interface support

11.5 CRC co-processor

12. FIFO Buffer

12.1 Overview

12.2 Accessing the FIFO Buffer

12.3 Controlling the FIFO-Buffer

12.4 Status Information about the FIFO-Buffer

13. Timer Unit

14. Interrupt Request System

15. Oscillator Circuitry

16. Power Reduction modes

16.1 Hard Power-down

16.2 Soft Power-down

16.3 Transmitter Power-down

17. Reset and Oscillator Startup Time

17.1 Reset Timing Requirements

17.2 Oscillator Startup Time

18. MFRC522 Command Set

18.1 General Description

18.2 General Behavior

18.3 MFRC522 Commands Overview

18.3.1 MFRC522 Command Description

18.3.1.1 Idle Command

18.3.1.2 Mem Command

18.3.1.3 Generate RandomID Command

18.3.1.4 CalcCRC Command

18.3.1.5 Transmit Command

18.3.1.6 NoCmdChange Command

18.3.1.7 Receive Command

18.3.1.8 Transceive Command

18.3.1.9 MFAuthent Command

18.3.1.10 SoftReset Command

19. Testsignals

19.1 Selftest

19.2 Test bus

19.3 Testsignals at pin AUX

19.3.1 Example: Output TestDAC 1 on AUX1 and TestDAC 2 on AUX2

19.3.2 Example: Output Testsignal Corr1 on AUX1 and MinLevel on AUX2

19.3.3 Example: Output ADC channel I on AUX 1 and ADC channel Q on AUX 2

19.3.4 Example: Output RxActive on AUX 1 and TxActive on AUX 2

19.3.5 Example: Output Rx Data Stream on AUX 1 and AUX 2

19.4 PRBS (Pseudo-Random Binary Sequence)

20. Limiting values

21. Recommended operating conditions

22. Thermal characteristics

23. Characteristics

23.1 Input Pin Characteristics

23.1.1 Input Pin characteristics for pins EA, I2C and NRESET

23.1.2 Input Pin characteristics for pin MFIN

23.1.3 Input/Output Pin characteristics for pins D1, D2, D3, D4, D5, D6 and D7

23.1.4 Input Pin characteristics for pin SDA

23.1.5 Output Pin characteristics for Pin MFOUT

23.1.6 Output Pin characteristics for Pin IRQ

23.1.7 Input Pin characteristics for Pin Rx

23.1.8 Input Pin characteristics for pin OSCIN

23.1.9 Output Pin characteristics for Pins AUX1 and AUX2

23.1.10 Output Pin characteristics for Pins TX1 and TX2

23.2 Current Consumption

23.3 RX Input Voltage Range

23.4 RX Input Sensitivity

23.5 Clock Frequency

23.6 XTAL Oscillator

23.7 Typical 27.12 MHz Crystal Requirements

23.8 Timing for the SPI compatible interface

23.9 I2C Timing

24. Application information

25. Package outline

26. Handling information

27. Packing information

28. Abbreviations

29. References

30. Revision history

31. Legal information

31.1 Data sheet status

31.2 Definitions

31.3 Disclaimers

31.4 Trademarks

32. Contact information

33. Tables

34. Figures

35. Contents