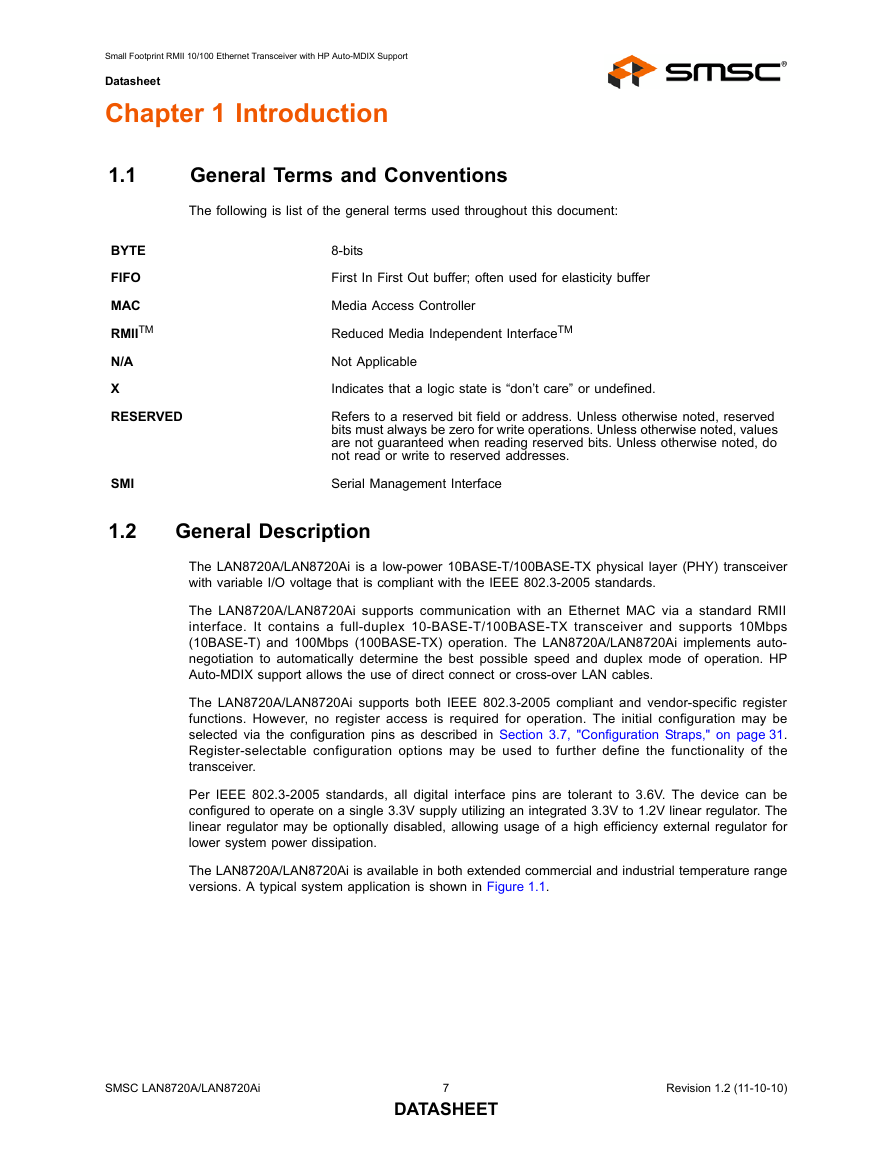

Chapter 1 Introduction

1.1 General Terms and Conventions

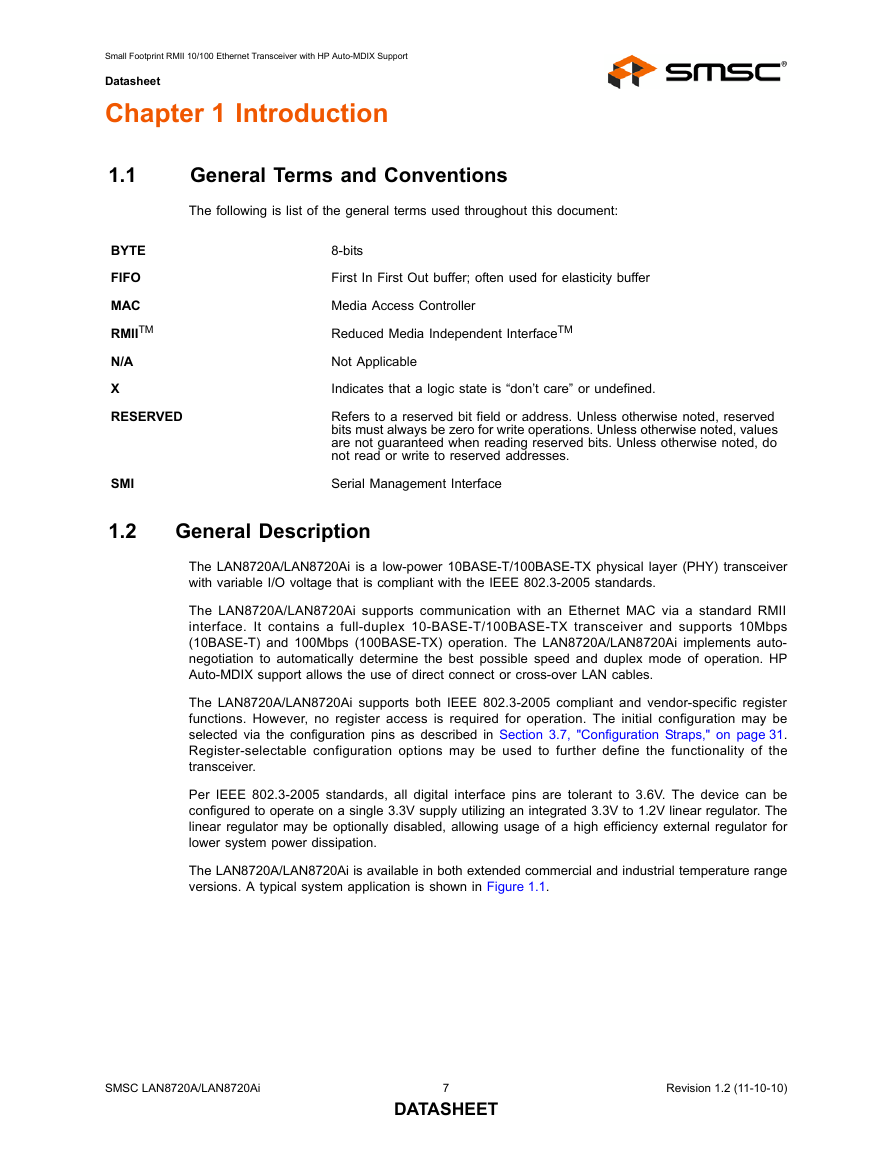

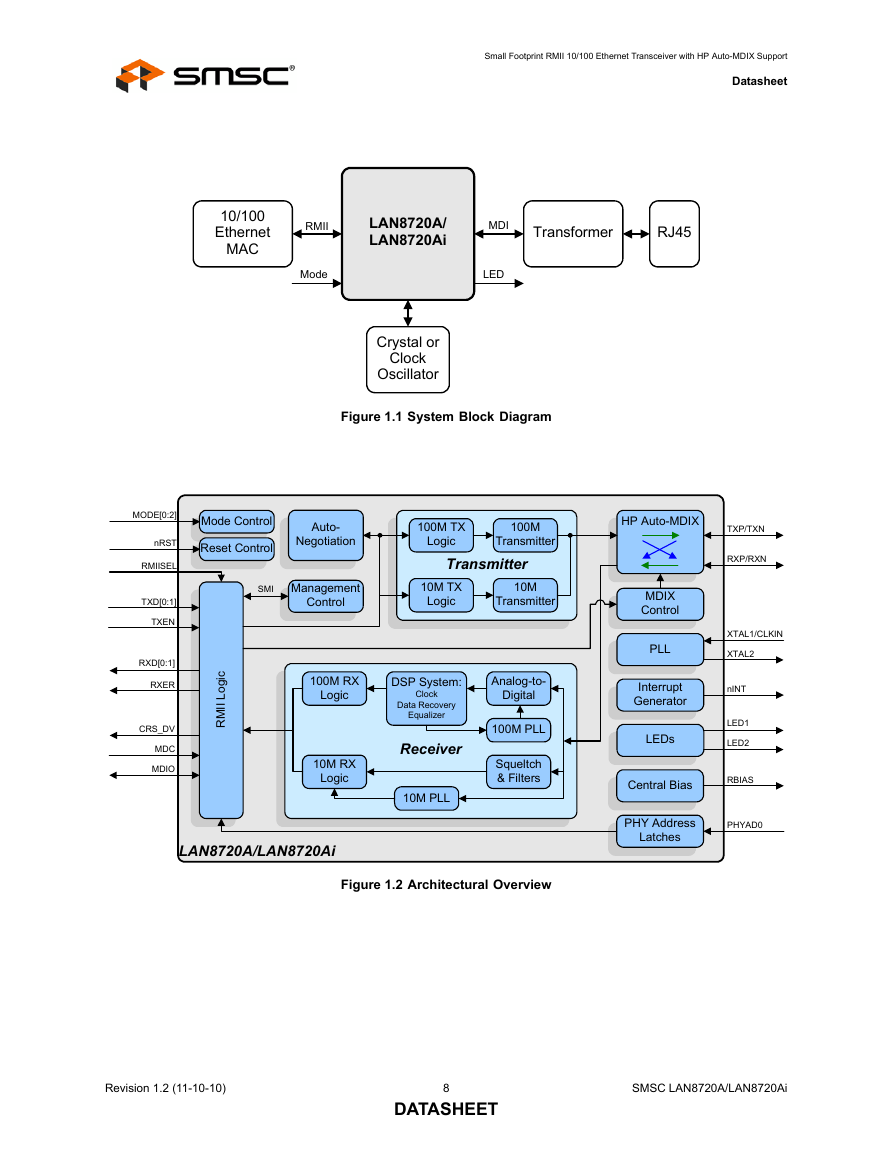

1.2 General Description

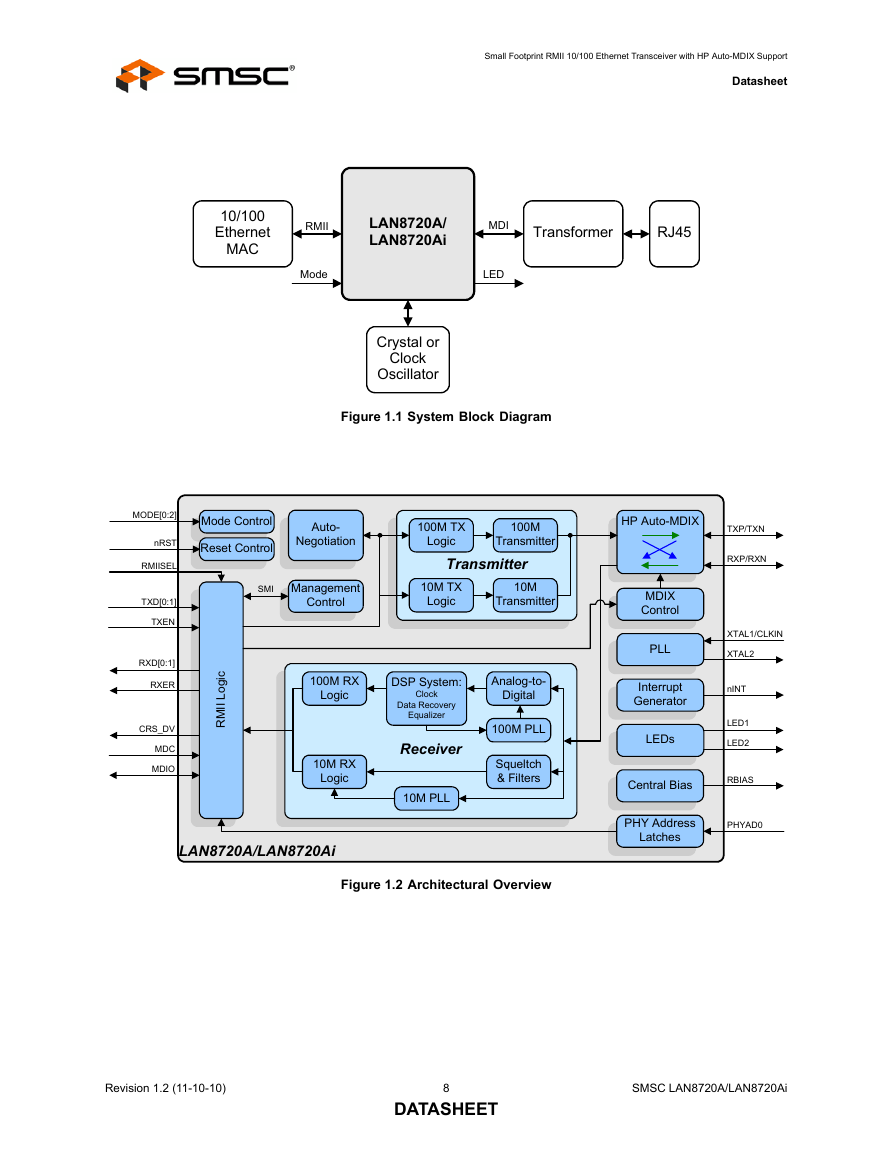

Figure 1.1 System Block Diagram

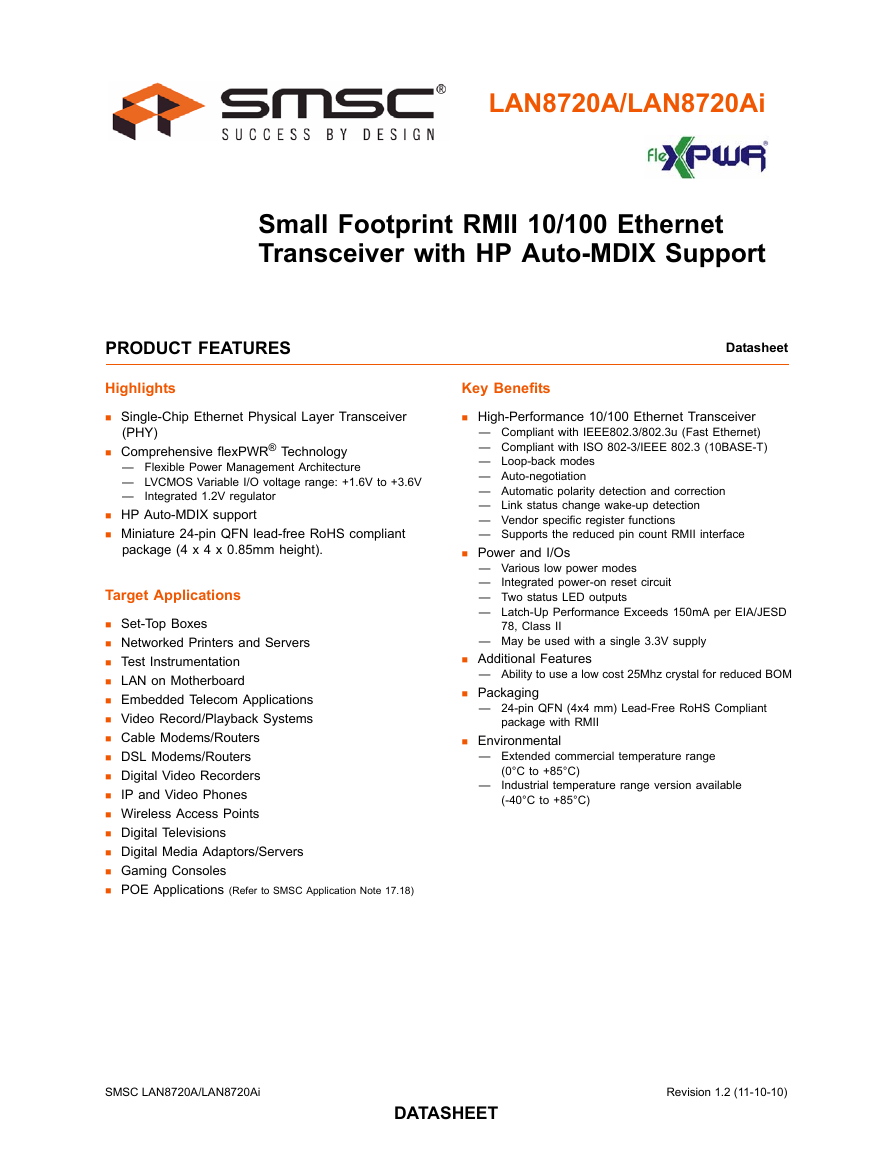

Figure 1.2 Architectural Overview

Chapter 2 Pin Description and Configuration

Figure 2.1 24-QFN Pin Assignments (TOP VIEW)

Table 2.1 RMII Signals

Table 2.2 LED Pins

Table 2.3 Serial Management Interface (SMI) Pins

Table 2.4 Ethernet Pins

Table 2.5 Miscellaneous Pins

Table 2.6 Analog Reference Pins

Table 2.7 Power Pins

2.1 Pin Assignments

Table 2.8 24-QFN Package Pin Assignments

2.2 Buffer Types

Table 2.9 Buffer Types

Chapter 3 Functional Description

3.1 Transceiver

3.1.1 100BASE-TX Transmit

Figure 3.1 100BASE-TX Transmit Data Path

Table 3.1 4B/5B Code Table

3.1.2 100BASE-TX Receive

Figure 3.2 100BASE-TX Receive Data Path

Figure 3.3 Relationship Between Received Data and Specific MII Signals

3.1.3 10BASE-T Transmit

3.1.4 10BASE-T Receive

3.2 Auto-negotiation

3.2.1 Parallel Detection

3.2.2 Restarting Auto-negotiation

3.2.3 Disabling Auto-negotiation

3.2.4 Half vs. Full Duplex

3.3 HP Auto-MDIX Support

Figure 3.4 Direct Cable Connection vs. Cross-over Cable Connection

3.4 MAC Interface

3.4.1 RMII

3.5 Serial Management Interface (SMI)

Figure 3.5 MDIO Timing and Frame Structure - READ Cycle

Figure 3.6 MDIO Timing and Frame Structure - WRITE Cycle

3.6 Interrupt Management

3.6.1 Primary Interrupt System

Table 3.2 Interrupt Management Table

3.6.2 Alternate Interrupt System

Table 3.3 Alternative Interrupt System Management Table

3.7 Configuration Straps

3.7.1 PHYAD[0]: PHY Address Configuration

3.7.2 MODE[2:0]: Mode Configuration

Table 3.4 MODE[2:0] Bus

Table 3.5 Pin Names for Mode Bits

3.7.3 REGOFF: Internal +1.2V Regulator Configuration

3.7.4 nINTSEL: nINT/REFCLKO Configuration

Table 3.6 nINTSEL Configuration

Figure 3.7 External 50MHz clock sources the REF_CLK

Figure 3.8 Sourcing REF_CLK from a 25MHz Crystal

Figure 3.9 Sourcing REF_CLK from External 25MHz Source

3.8 Miscellaneous Functions

3.8.1 LEDs

Figure 3.10 LED1/REGOFF Polarity Configuration

Figure 3.11 LED2/nINTSEL Polarity Configuration

3.8.2 Variable Voltage I/O

3.8.3 Power-Down Modes

3.8.4 Isolate Mode

3.8.5 Resets

3.8.6 Carrier Sense

3.8.7 Link Integrity Test

3.8.8 Loopback Operation

Figure 3.12 Near-end Loopback Block Diagram

Figure 3.13 Far Loopback Block Diagram

Figure 3.14 Connector Loopback Block Diagram

3.9 Application Diagrams

3.9.1 Simplified System Level Application Diagram

Figure 3.15 Simplified System Level Application Diagram

3.9.2 Power Supply Diagram (1.2V Supplied by Internal Regulator)

Figure 3.16 Power Supply Diagram (1.2V Supplied by Internal Regulator)

3.9.3 Power Supply Diagram (1.2V Supplied by External Source)

Figure 3.17 Power Supply Diagram (1.2V Supplied by External Source)

3.9.4 Twisted-Pair Interface Diagram (Single Power Supply)

Figure 3.18 Twisted-Pair Interface Diagram (Single Power Supply)

3.9.5 Twisted-Pair Interface Diagram (Dual Power Supplies)

Figure 3.19 Twisted-Pair Interface Diagram (Dual Power Supplies)

Chapter 4 Register Descriptions

4.1 Register Nomenclature

Table 4.1 Register Bit Types

4.2 Control and Status Registers

Table 4.2 SMI Register Map

4.2.1 Basic Control Register

4.2.2 Basic Status Register

4.2.3 PHY Identifier 1 Register

4.2.4 PHY Identifier 2 Register

4.2.5 Auto Negotiation Advertisement Register

4.2.6 Auto Negotiation Link Partner Ability Register

4.2.7 Auto Negotiation Expansion Register

4.2.8 Mode Control/Status Register

4.2.9 Special Modes Register

4.2.10 Symbol Error Counter Register

4.2.11 Special Control/Status Indications Register

4.2.12 Interrupt Source Flag Register

4.2.13 Interrupt Mask Register

4.2.14 PHY Special Control/Status Register

Chapter 5 Operational Characteristics

5.1 Absolute Maximum Ratings*

5.2 Operating Conditions**

5.3 Power Consumption

5.3.1 REF_CLK In Mode

Table 5.1 Device Only Current Consumption and Power Dissipation (REF_CLK In Mode)

5.3.2 REF_CLK Out Mode

Table 5.2 Device Only Current Consumption and Power Dissipation (REF_CLK Out Mode)

5.4 DC Specifications

Table 5.3 Non-Variable I/O Buffer Characteristics

Table 5.4 Variable I/O Buffer Characteristics

Table 5.5 100BASE-TX Transceiver Characteristics

Table 5.6 10BASE-T Transceiver Characteristics

5.5 AC Specifications

5.5.1 Equivalent Test Load

Figure 5.1 Output Equivalent Test Load

5.5.2 Power Sequence Timing

Figure 5.2 Power Sequence Timing

Table 5.7 Power Sequence Timing Values

5.5.3 Power-On nRST & Configuration Strap Timing

Figure 5.3 Power-On nRST & Configuration Strap Timing

Table 5.8 Power-On nRST & Configuration Strap Timing Values

5.5.4 RMII Interface Timing

Figure 5.4 RMII Timing (REF_CLK Out Mode)

Table 5.9 RMII Timing Values (REF_CLK Out Mode)

Figure 5.5 RMII Timing (REF_CLK In Mode)

Table 5.10 RMII Timing Values (REF_CLK In Mode)

Table 5.11 RMII CLKIN (REF_CLK) Timing Values

5.5.5 SMI Timing

Figure 5.6 SMI Timing

Table 5.12 SMI Timing Values

5.6 Clock Circuit

Table 5.13 Crystal Specifications

Chapter 6 Package Outline

Chapter 7 Datasheet Revision History

Table 7.1 Customer Revision History