第32卷第1期

2009年2月

电子器件

Chinese Jourmt Of Electron Devic8

v01.32

No.1

Feb.2009

Design of a Acoustic Signals High Speed Acquisition and

Storage System Based on FPGA and SD Card

ZHANG Hong-gang,YUAN Bing-cheng。,XU Yu

(Departmentof Weaponry Engineering,Naval University ofEngineering,Wuhan 430033,China)

Abstract:Aiming at the disadvantage of the acoustic signals,difficult to acquire real-time at present,a de-

sign of high-speed acoustic signals acquisition,large capacity and real—time store system is proposed,which

uses single chip as a controller,SD card as memory,FPGA as high-speed interface between acquisition

and SD card,FAT file system as format of storage.This design has merits of small size,capability of

high-speed and real—time storage,large capacity,high universal ability and expansibility,etc.It has been

successfully applied in noise acquisition of a underwater vehicle.

Key WOl dS:acoustic signal acquisition;high-speed and real-time storage;FPGA;SD card;FAT file system

EEACC:7810;7210G

基于FPGA和SD卡的水声信号高速采集与存储系统设计

张洪刚,苑秉成。,徐 瑜

(海军工程大学兵器工程系,武汉430033)

摘要:针对目前较高频率水声信号数据难于实时获取的局限,提出了一种基于sD卡和FPGA的高速大容量水声信号采集

与实时存储系统设计,设计中采用单片机作为主控单元,SD卡作为存储介质,FPGA作为数据采集和SD卡之间的高速接口,

FAT文件系统作为数据存储形式。该设计具有体积小,可高速实时存储,存储容量大,通用性强,易于扩展升级等特点,已在

某水下航行器辐射噪声信号获取中得到成功运用。

关键词:水声信号采集;大容量实时存储;FPGAfSD卡;FAT文件系统

中图分类号:TP274

文献标识码:A

文章编号:l005—9490(2009)01_0208-05

由于水下的特殊环境,水下目标的探测、定位、

识别等都是以声波为载体的。在对水声信号的研

究,水声设备的研制、调试以及水声设备的陆上仿真

试验等过程中,都需要准确可靠的原始水声信号资

料。一直以来,由于工作环境恶劣、试验成本高、采

集数据难于高速实时存储等不利因素,水声信号的

实时采集较为困难。本文提出了一种基于FPGA

和SD卡的水声信号的高速大容量水声信号采集与

实时存储系统的设计方案,并进行了工程实现。本

设计具有采集速率高(高于1 MHz),存储容量大(2

G,可方便扩展),实时存储,体积小,使用方便(存储

在SD卡的数据可用通用读卡器读出),工作可靠的

特点。目前该系统在某水下航行器的辐射噪声采集

与存储中已得到运用,其合理性和工作可靠性也得

到了很好的验证。

1 系统总体结构与硬件设计

本文设计的数据采集与存储系统的工作环境是

某装备的电子仓,需采集的信号为某水下航行器的

辐射噪声,根据装备信号处理系统和电子仓内安装

的需求,所设计数据采集和存储系统需满足:①单

通道,采集速率不低于1 MHz;②数据实时存储,存

储时间不小于20 min;③小体积,电路板尺寸小于

55 mmX 85 mm;④工作可靠,出现异常情况时能

收稿日期:2008-08-06

作者简介:张洪刚(1980一),男,博士研究生,研究方向为水下目标探测与制导,honggangzhang@126.com!

苑秉成,教授,研究方向为鱼雷自导与武器仿真技术

万方数据

�

第1期

张洪刚,苑秉成等:基于FPGA和SD卡的水声信号高速采集与存储系统设计

209

保证采集的有效数据不丢失。

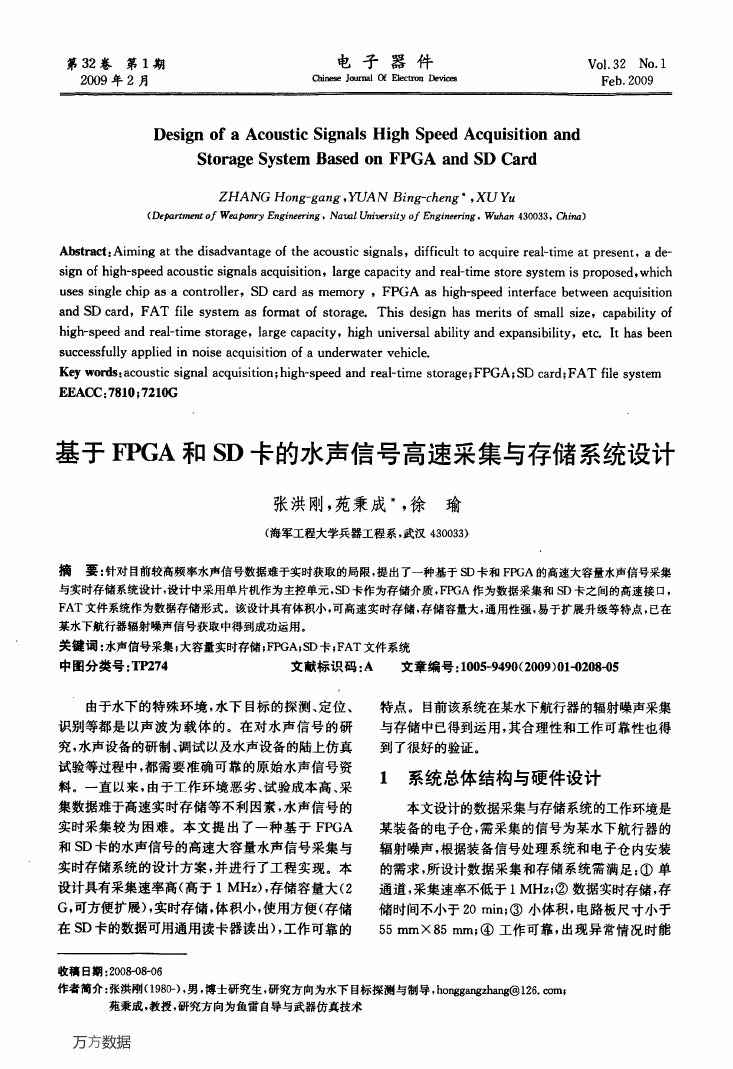

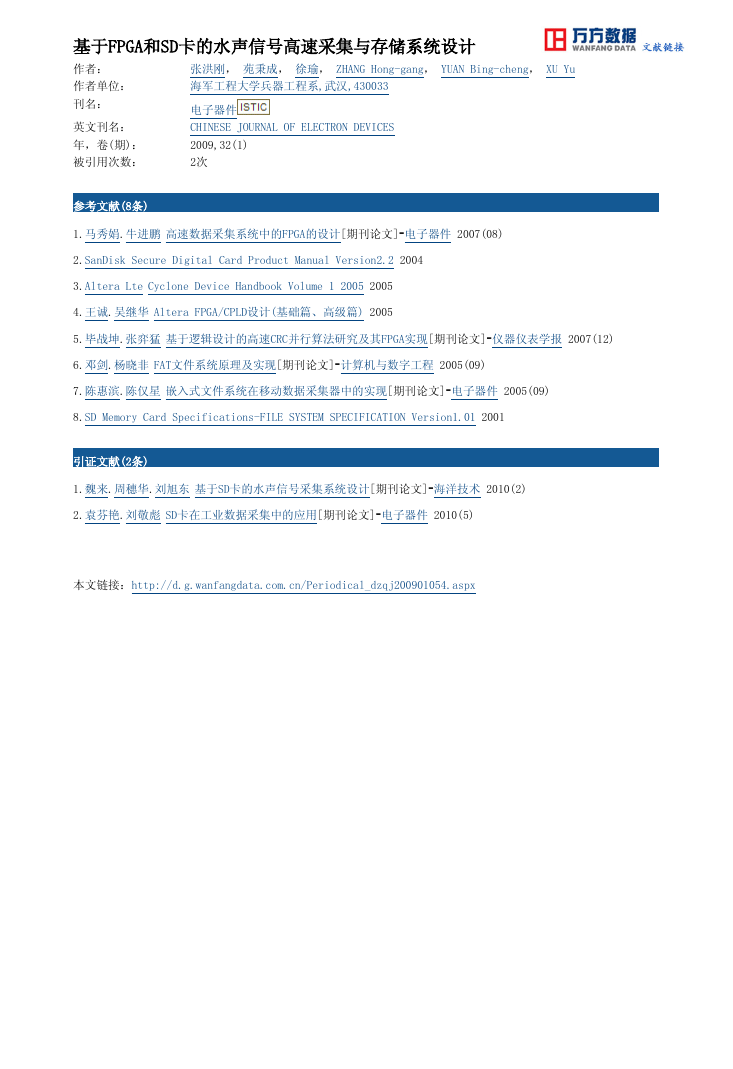

系统的总体结构如图1所示,主要由A/D采集

模块、FPGA接口模块、单片机、门限比较电路以及

SD卡等组成。系统工作电源采用电子仓提供的直

流电源,经隔离、滤波后转换成系统所需的十5 V、

+3.3 V与+1.5 V电源。进入射随的输入信号已

经过了放大和滤波,范围在一5 V~+5 V;单片机

是系统的主控单元,初始化FPGA和SD卡,并在

SD卡中建立FAT文件系统;FPGA对采集数据进

行缓冲和格式转换,使得数据读写满足SD卡的协

议要求L11;由于系统是在水下独立工作,所以设计门

限比较电路,当信号幅度超过门限才启动信号采集

与存储过程。

图1 系统总体结构框图

A/D采集芯片采用TI公司的高速8位CMOS

工艺的模数转换器ADS831,采用单一+5 V供电,

内部带有取样保持电路。ADS831采用流水线结

构,因而采样速率可高达80 MHz。ADS831的可编

程模拟输入范围有1 Vp—p和2 Vp—p两种,因此

信号输入端经过了分压和运放OPA681构成的调

理电路。

单片机采用Cygnal公司的小体积混合信号微

处理器C8051F310,具有兼容8051的高速CIP-51

内核,时钟频率为25 MHz时最高运行速度可达25

MIPS,内部集成有1 280 byte RAM、16 kbyte的

flash存储器、SPI总线接口等。

SD卡是基于快速闪存的新一代存储器,具有体

积小、容量大、数据传输陕、移动灵活、安全性能好等

优点,目前市场上已有16 Gbyte容量,150倍速率

(1倍速率一150 kbyte/s)的SD卡,而体积只有24

mm×32 mm×2.1 mm。这里采用的是Sandisk公

司的133倍速的2 G容量SD卡。

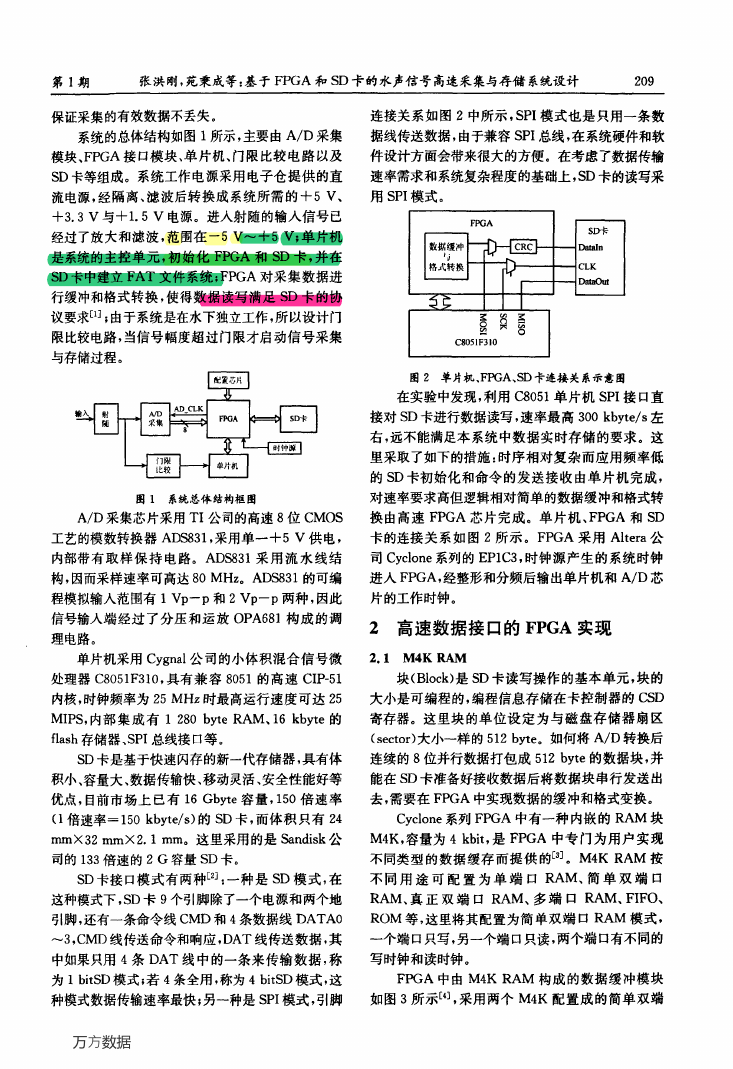

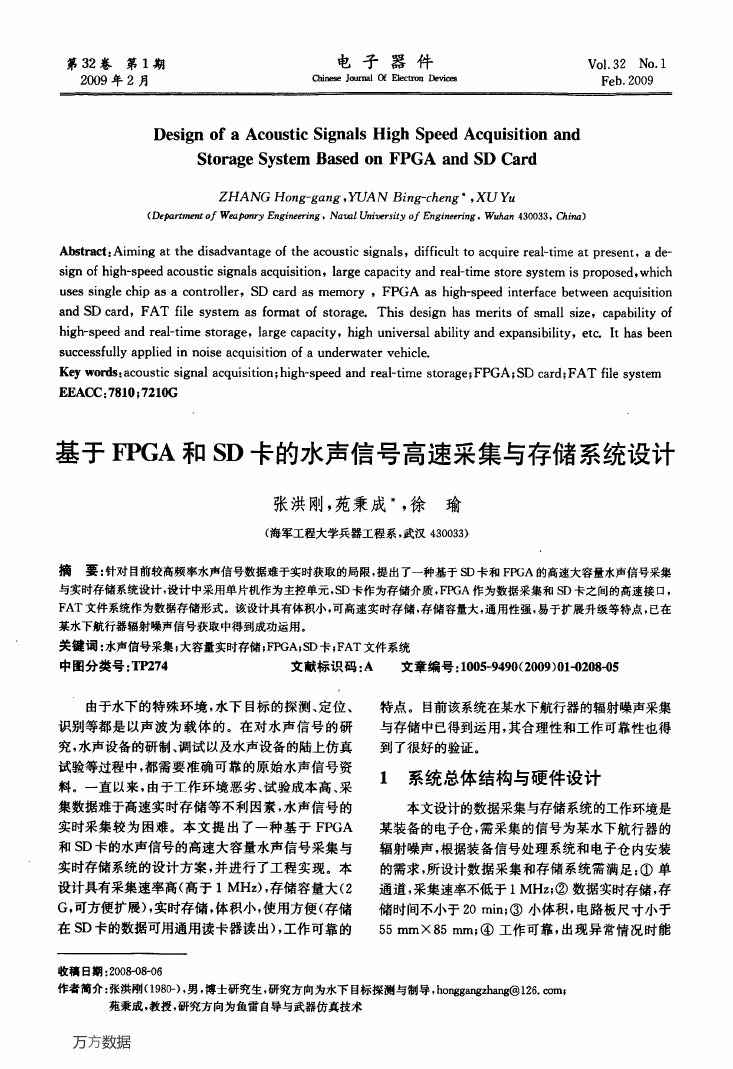

连接关系如图2中所示,SPI模式也是只用一条数

据线传送数据,由于兼容SPI总线,在系统硬件和软

件设计方面会带来很大的方便。在考虑了数据传输

速率需求和系统复杂程度的基础上,SD卡的读写采

用SPI模式。

图2单片机、FPGA、SD卡连接关系示意图

在实验中发现,利用C8051单片机SPI接口直

接对SD卡进行数据读写,速率最高300 kbyte/s左

右,远不能满足本系统中数据实时存储的要求。这

里采取了如下的措施:时序相对复杂而应用频率低

的SD卡初始化和命令的发送接收由单片机完成,

对速率要求高但逻辑相对简单的数据缓冲和格式转

换由高速FPGA芯片完成。单片机、FPGA和SD

卡的连接关系如图2所示。FPGA采用Altera公

司Cyclone系列的EPlC3,时钟源产生的系统时钟

进入FPGA,经整形和分频后输出单片机和A/D芯

片的工作时钟。

2高速数据接口的FPGA实现

2.1 M4K RAM

块(Block)是SD卡读写操作的基本单元,块的

大小是可编程的,编程信息存储在卡控制器的CSD

寄存器。这里块的单位设定为与磁盘存储器扇区

(sector)大小一样的512 byte。如何将A/D转换后

连续的8位并行数据打包成512 byte的数据块,并

能在SD卡准备好接收数据后将数据块串行发送出

去,需要在FPGA中实现数据的缓冲和格式变换。

Cyclone系列FPGA中有一种内嵌的RAM块

M4K,容量为4 kbit,是FPGA中专门为用户实现

不同类型的数据缓存而提供的[3]。M4K RAM按

SD卡接口模式有两种[2]:一种是SD模式,在

不同用途可配置为单端口RAM、简单双端口

这种模式下,SD卡9个引脚除了一个电源和两个地

引脚,还有一条命令线CMD和4条数据线DATA0

~3,CMD线传送命令和响应,DAT线传送数据,其

中如果只用4条DAT线中的一条来传输数据,称

RAM、真正双端口RAM、多端口RAM、FIFO、

ROM等,这里将其配置为简单双端口RAM模式,

一个端口只写,另一个端口只读,两个端口有不同的

写时钟和读时钟。

为1 bitSD模式;若4条全用,称为4 bitSD模式,这

种模式数据传输速率最快;另~种是SPI模式,引脚

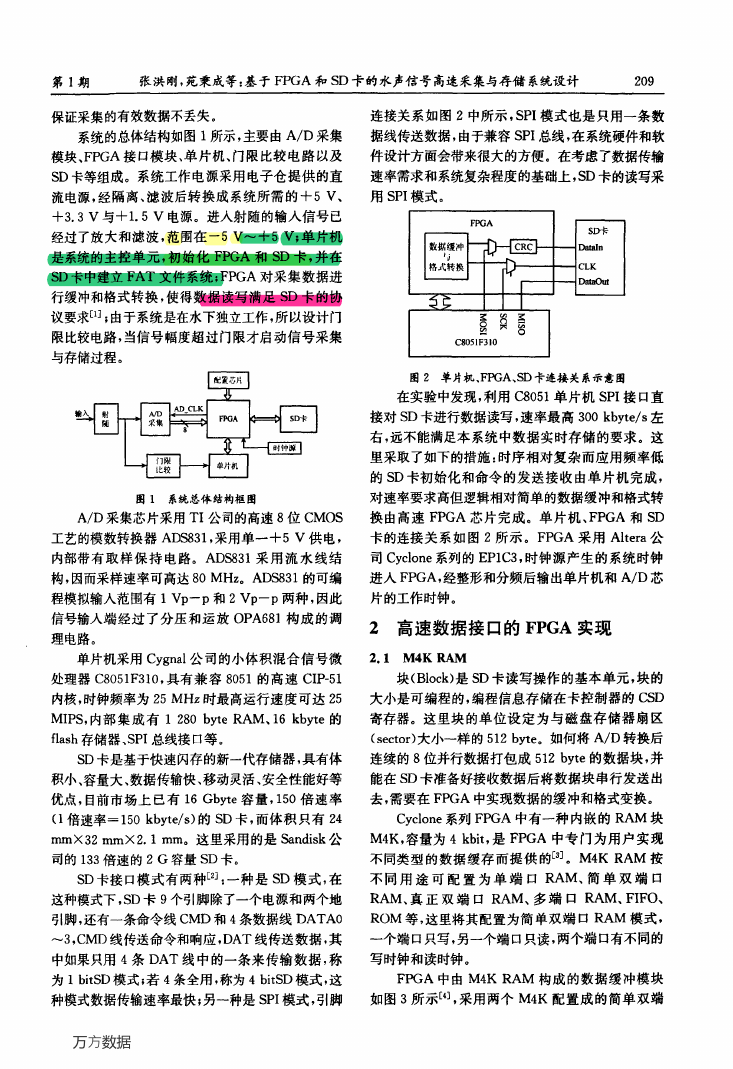

FPGA中由M4K RAM构成的数据缓冲模块

如图3所示[4],采用两个M4K配置成的简单双端

万方数据

�

210

电 子 器件

第32卷

口RAM交替进行数据的读写操作,一个RAM在

进行写操作时,另一个RAM进行读操作。计数器

counter0产生数据写入RAM块的9位地址,dtff

模块相当于将进位标志cout信号延时一个时钟周

期后接T触发器,这样计数器每计数完一个周期输

的wren和rden。512 byte的双端口RAM输入总

线配置为8位,采集来的数据data[-7..o]可以直接

写入RAM,输出总线配置为1位,这样在RAM中

就同时完成了数据的并串转换。计数器counterl

产生读数据的12位地址,写时钟wrclk采用l

出端Q就会翻转一次,恰好交替使能两个RAM块

MHz,读时钟采用20 MHz。

需要注意的是,M4K RAM块是纯同步的

G(z)=z7+z3+1

图3 M4K RAM构成的数据缓冲模块

G(z)=X16+z12+z5+l

CRC7发生器硬件实现原理图如图4所示,图

(1)

(2)

RAM,在RAM块的输入地址、输入数据和读写使

能信号端均有一级输入寄存器,中间是一个纯异步

读写的RAM内核,数据输出端的一级寄存器是可

选的,这里将该寄存器选中。这样在输入端和输出

端的所有信号都会延时一个时钟周期。

2.2 CRC校验

中方块是移位寄存器,data in端每送入一位就进行

一次异或操作和循环移位,最后一位数据移出data

out端后7个寄存器的数据就是计算得到的CRC

校验码。FPGA中CRC7校验模块用VHDI,语言

CRC(Cyclic Redundancy Check,循环冗余校 实现,模块内将校验位经并串转换后附在串行发送

的数据后面。例如当输入数据为“ii0100101”时,经

计算生成的校验位是“1010101”,CRC7模块在Qu一

验)是SD卡应对命令、回复和数据传输过程中SD

总线出错的措施。CRC校验的基本思想是:利用线

性编码理论,串行传送的信息M(z)是一串惫位二 artusIl软件中的波形仿真如图5所示。

进制序列,在它被发送的同时,被一个先选择的“生

成多项式”相除,“生成多项式”长r+l位,相除后得

到,.位的余数就是校验位,它拼接到原k位有效信

息后面,即形成CRC码。CRC码到达接受方时,接

受方的设备一方面接受CRC码,一方面用同样的方

法与“生成多项式”相除,如果正好除尽,表示无信息

差错,接受方去掉CRC码后面的r位校验,收下k

位有效信息;如果不能除尽时,说明有信息的状态位

发生了转变,即传输过程中出错[5]。

SD卡所有的命令和大部分回复的CRC校验称

为CRC7,是采用一个7位的校验码,其生成多项式

如式(1)。SD卡数据线上的CRC校验称为

CRCl6,是采用的16位校验码,生成多项式如式(2)

万方数据

图4

CRC7发生器硬件实现原理图

■-●

y.1Ⅵ

10 I

elk

甘c-rst

口C一●n

d●t●i“

creout

ht●●■^

H

M

H

H

KI

XI

—

一

一

驴

p

口

图5

FPGA中CRC7发生模块仿真波形图

�

第1期

张洪剐,苑秉成等:基于FPGA和SD卡的水声信号高速采集与存储系统设计

211

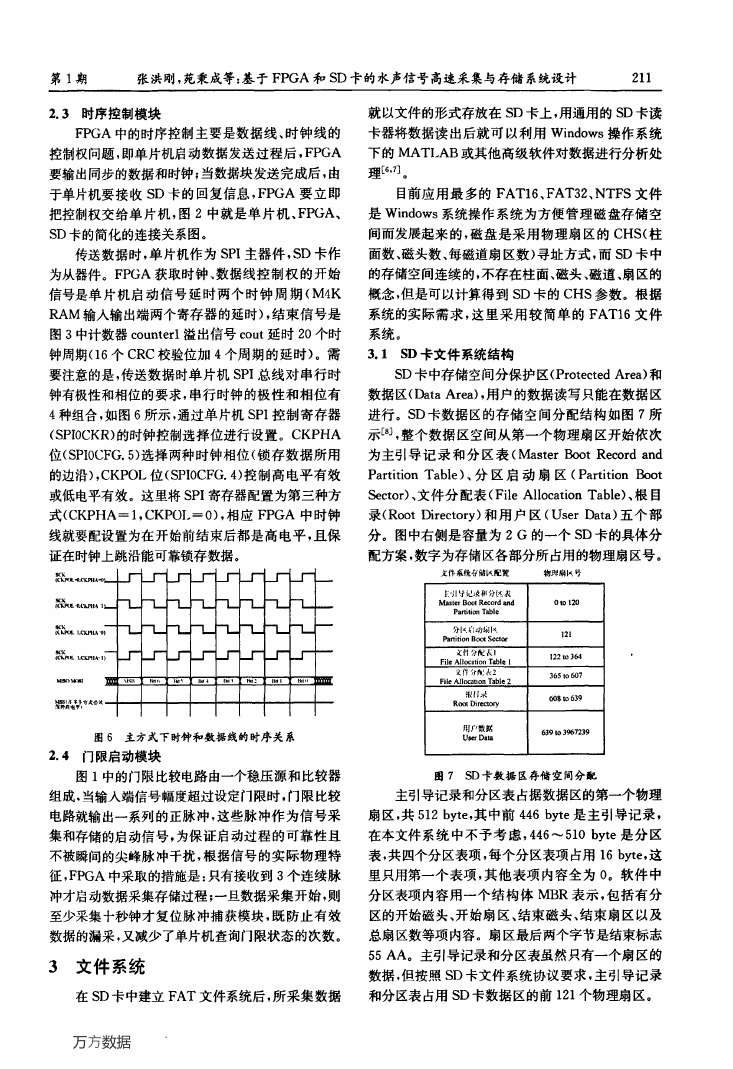

2.3时序控制模块

FPGA中的时序控制主要是数据线、时钟线的

控制权问题,即单片机启动数据发送过程后,FPGA

要输出同步的数据和时钟;当数据块发送完成后,由

于单片机要接收SD卡的回复信息,FPGA要立即

把控制权交给单片机,图2中就是单片机、FPGA、

SD卡的简化的连接关系图。

传送数据时,单片机作为SPI主器件,SD卡作

为从器件。FPGA获取时钟、数据线控制权的开始

信号是单片机启动信号延时两个时钟周期(M4K

RAM输入输出端两个寄存器的延时),结束信号是

图3中计数器counterl溢出信号cout延时20个时

钟周期(16个CRC校验位加4个周期的延时)。需

要注意的是,传送数据时单片机SPI总线对串行时

钟有极性和相位的要求,串行时钟的极性和相位有

4种组合,如图6所示,通过单片机SPI控制寄存器

(SPIOCKR)的时钟控制选择位进行设置。CKPHA

位(SPIocFG.5)选择两种时钟相位(锁存数据所用

的边沿),CKPOL位(sPl0CFG.4)控制高电平有效

或低电平有效。这里将SPI寄存器配置为第三种方

式(CKPHA=1,CKPOI。=o),相应FPGA中时钟

线就要配设置为在开始前结束后都是高电平,且保

证在时钟上跳沿能可靠锁存数据。

__一

_一

__—l

|O;POL吨‘∽IA

1L —L 。1,一 ■L 1L ■Z一 ■L —1

1,- ■L ■L —L 1,- ‘—L ■L 1

j广 jr —广 j广’ J广 —l一。 j■ ...J

、IEn

~‘

hI’ :hI 2:

hl¨1

图6主方式下时钟和数据线的时序关系

2.4门限启动模块

图1中的门限比较电路由一个稳压源和比较器

组成,当输入端信号幅度超过设定门限时,门限比较

电路就输出一系列的正脉冲,这些脉冲作为信号采

集和存储的启动信号,为保证启动过程的可靠性且

不被瞬间的尖峰脉冲干扰,根据信号的实际物理特

征,FPGA中采取的措施是:只有接收到3个连续脉

冲才启动数据采集存储过程;一旦数据采集开始,则

至少采集十秒钟才复位脉冲捕获模块,既防止有效

数据的漏采,又减少了单片机查询门限状态的次数。

3 文件系统

在SD卡中建立FAT文件系统后,所采集数据

万方数据

就以文件的形式存放在SD卡上,用通用的SD卡读

卡器将数据读出后就可以利用Windows操作系统

下的MATI。AB或其他高级软件对数据进行分析处

理[6.7]。

目前应用最多的FATl6、FAT32、NTFS文件

是Windows系统操作系统为方便管理磁盘存储空

间而发展起来的,磁盘是采用物理扇区的CHS(柱

面数、磁头数、每磁道扇区数)寻址方式,而SD卡中

的存储空间连续的,不存在柱面、磁头、磁道、扇区的

概念,但是可以计算得到SD卡的CHS参数。根据

系统的实际需求,这里采用较简单的FATl6文件

系统。

3.1

SD卡文件系统结构

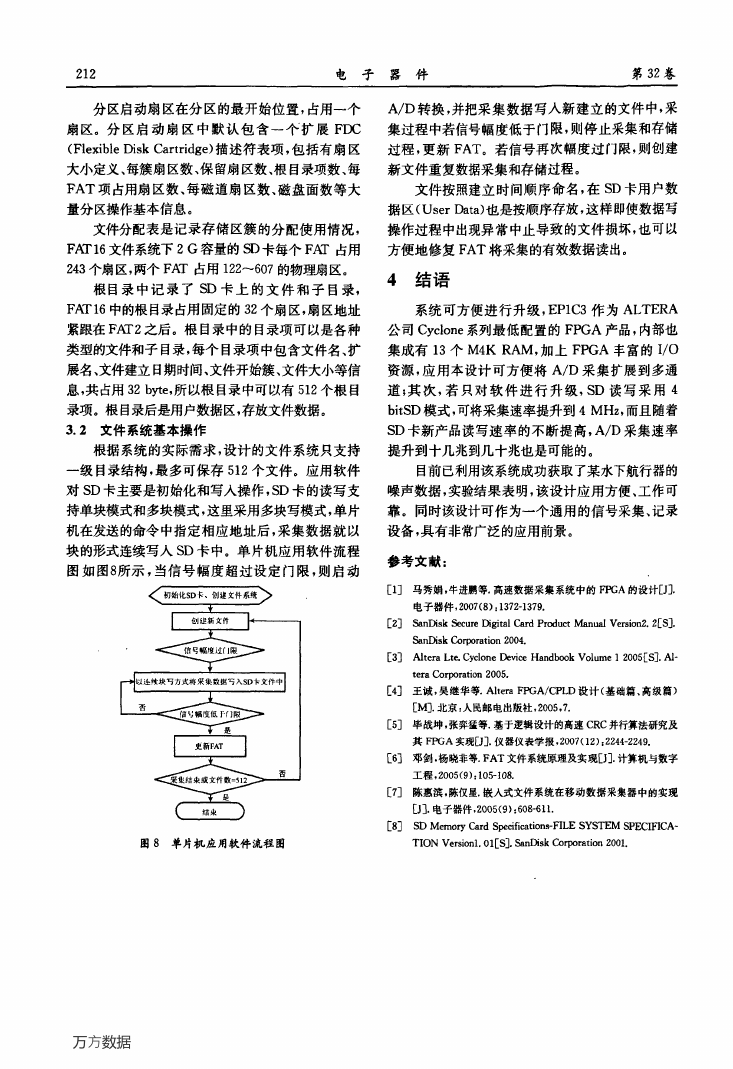

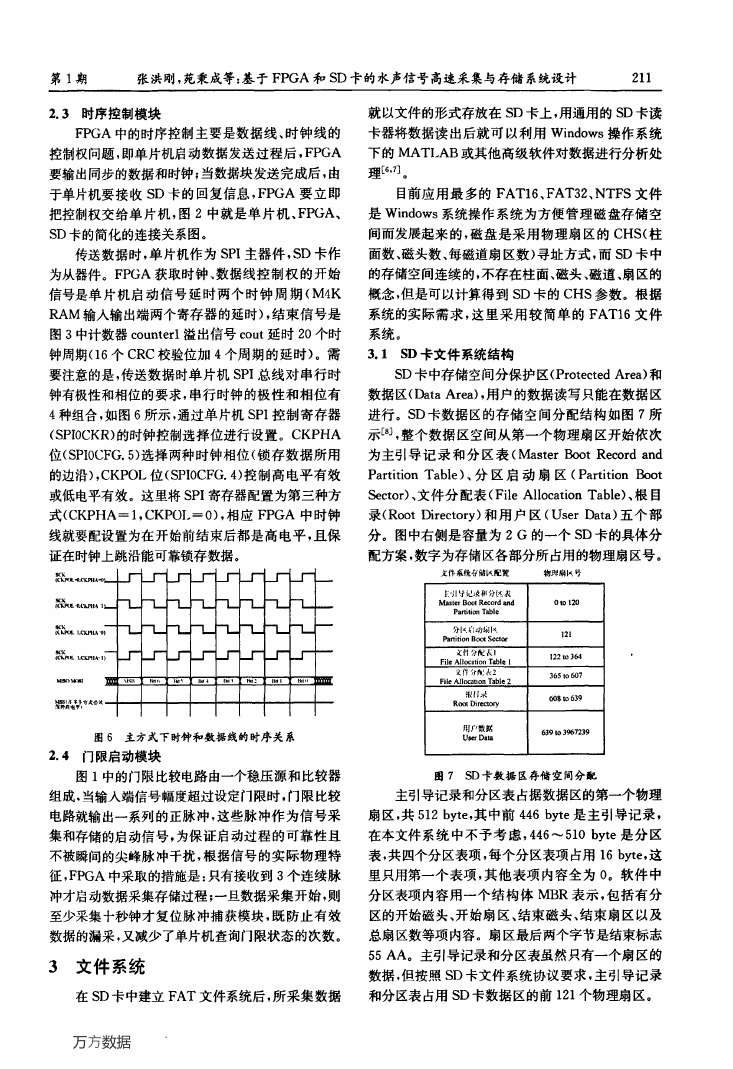

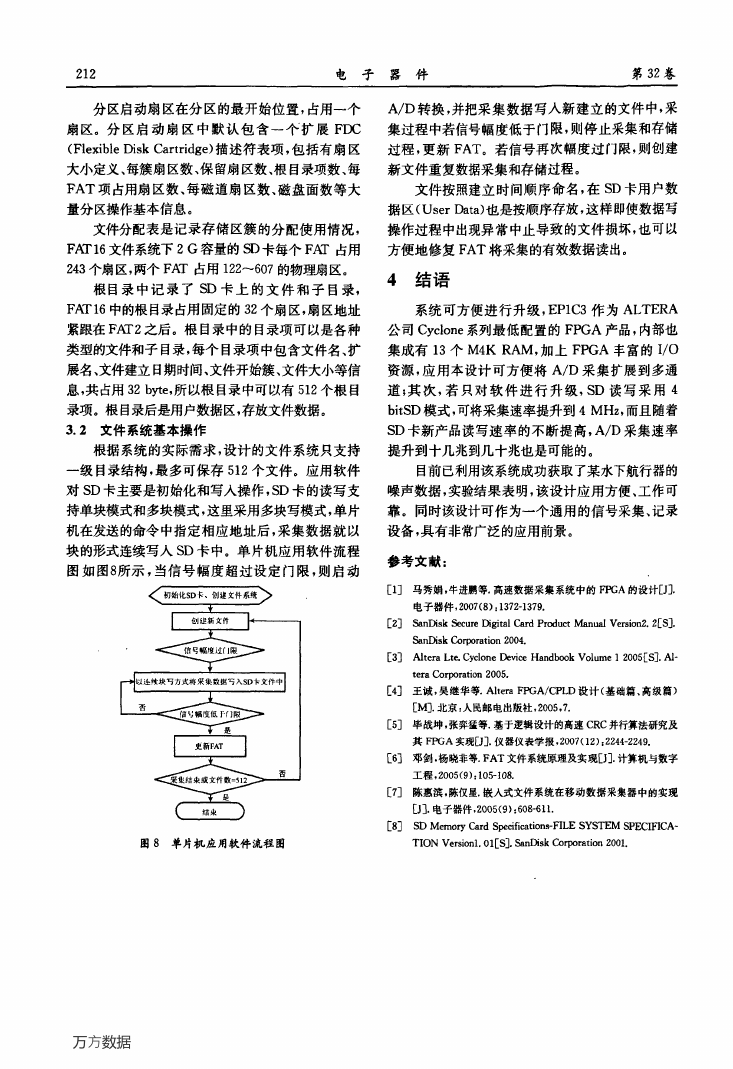

SD卡中存储空间分保护区(Protected Area)和

数据区(Data Area),用户的数据读写只能在数据区

进行。SD卡数据区的存储空间分配结构如图7所

示[8],整个数据区空间从第一个物理扇区开始依次

为主引导记录和分区表(Master Boot Record and

Partition Table)、分区启动扇区(Partition Boot

Sector)、文件分配表(File Allocation Table)、根目

录(Root Directory)和用户区(User Data)五个部

分。图中右侧是容量为2 G的一个SD卡的具体分

配方案,数字为存储区各部分所占用的物理扇区号。

文件系统存储K配甓

物弹扇I^号

扛·;l甘记求和1分随衷

Master Boot Record and

Partition T曲le

分lt启动确k

Partition Boot Sector

Zr}分雕是1

File Allocation 1-曲Ie I

证f’l,,~太2

File AIIocatmn Table 2

般fi采

Root Di脚ry

0tol20

121

12210 364

365 10607

608t0639

用P数据

UwData

639 Io 3967239

图7

SD卡数据区存储空间分配

主引导记录和分区表占据数据区的第一个物理

扇区,共512 byte,其中前446 byte是主引导记录,

在本文件系统中不予考虑,446~510 byte是分区

表,共四个分区表项,每个分区表项占用16 byte,这

里只用第一个表项,其他表项内容全为0。软件中

分区表项内容用一个结构体MBR表示,包括有分

区的开始磁头、开始扇区、结束磁头、结束扇区以及

总扇区数等项内容。扇区最后两个字节是结束标志

55 AA。主引导记录和分区表虽然只有一个扇区的

数据,但按照SD卡文件系统协议要求,主引导记录

和分区表占用SD卡数据区的前121个物理扇区。

�

212

电子 器件

第32卷

分区启动扇区在分区的最开始位置,占用一个

扇区。分区启动扇区中默认包含一个扩展FDC

(Flexible Disk Cartridge)描述符表项,包括有扇区

大小定义、每簇扇区数、保留扇区数、根目录项数、每

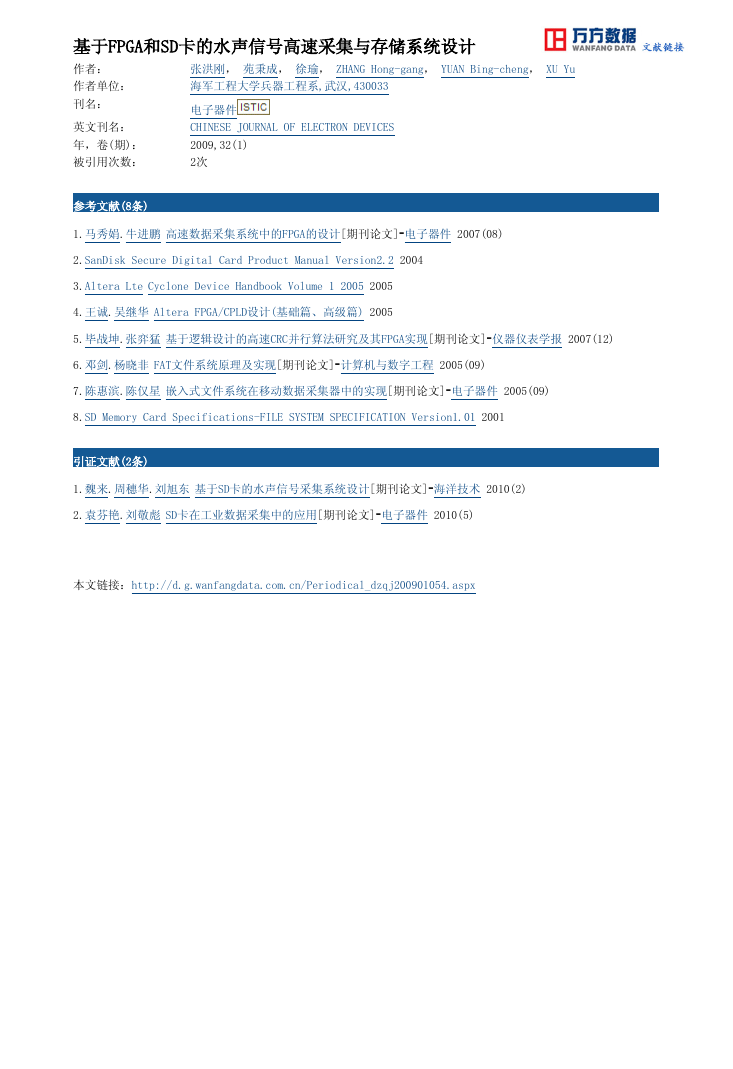

A/D转换,并把采集数据写入新建立的文件中,采

集过程中若信号幅度低于门限,则停止采集和存储

过程,更新FAT。若信号再次幅度过门限,则创建

新文件重复数据采集和存储过程。

FAT项占用扇区数、每磁道扇区数、磁盘面数等大

量分区操作基本信息。

文件按照建立时间顺序命名,在SD卡用户数

据区(User Data)也是按顺序存放,这样即使数据写

文件分配表是记录存储区簇的分配使用情况,

FATl6文件系统下2 G容量的SD卡每个FAT占用

操作过程中出现异常中止导致的文件损坏,也可以

方便地修复FAT将采集的有效数据读出。

243个扇区,两个FAT占用122~607的物理扇区。

根目录中记录了SD卡上的文件和子目录,

4结语

FATl6中的根目录占用固定的32个扇区,扇区地址

系统可方便进行升级,EPlC3作为ALTERA

紧跟在FAT2之后。根目录中的目录项可以是各种

类型的文件和子目录,每个目录项中包含文件名、扩

展名、文件建立日期时间、文件开始簇、文件大小等信

息,共占用32 byte,所以根目录中可以有512个根目

录项。根目录后是用户数据区,存放文件数据。

3.2文件系统基本操作

根据系统的实际需求,设计的文件系统只支持

一级目录结构,最多可保存512个文件。应用软件

对SD卡主要是初始化和写入操作,SD卡的读写支

持单块模式和多块模式,这里采用多块写模式,单片

机在发送的命令中指定相应地址后,采集数据就以

块的形式连续写入SD卡中。单片机应用软件流程

图如图8所示,当信号幅度超过设定门限,则启动

公司Cyclone系列最低配置的FPGA产品,内部也

集成有13个M4K RAM,加上FPGA丰富的I/O

资源,应用本设计可方便将A/D采集扩展到多通

道;其次,若只对软件进行升级,SD读写采用4

bitSD模式,可将采集速率提升到4 MHz,而且随着

SD卡新产品读写速率的不断提高,A/D采集速率

提升到十几兆到几十兆也是可能的。

目前已利用该系统成功获取了某水下航行器的

噪声数据,实验结果表明,该设计应用方便、工作可

靠。同时该设计可作为一个通用的信号采集、记录

设备,具有非常广泛的应用前景。

参考文献:

D3马秀娟,牛进鹏等.高速数据采集系统中的FPGA的设计[J3.

电子器件,2007(8):1372-1379.

[2]SanDisk Secure Digital card Product Manual Version2.2Is].

SanDisk Corporation 2004.

E32

Altera Lte.Cyclone Device Handbook Volume 1 2005[sJ.AI·

tera Corporation 2005.

[4]王诚,吴继华等.Ahera FPGA/CPLD设计(基础篇、高级篇)

[M].北京:人民邮电出版社,2005,7.

[53毕战坤,张弈猛等.基于逻辑设计的高速CRC并行算法研究及

其FPGA实现D].仪器仪表学报,2007(12):2244—2249.

[63邓剑。杨晓非等.FAT文件系统原理及实现[J].计算机与数字

工程,2005(9):105-108.

[7]陈惠滨。陈仅星.嵌入式文件系统在移动数据采集器中的实现

[J].电子器件,2005(9):608-611.

[83

SD Memory card Specifications-FILE SYSTEM SPECIFICA—

图8单片机应用软件流程图

T10N Versionl.01[s3.SanDisk Corporation 2001.

万方数据

�

基于FPGA和SD卡的水声信号高速采集与存储系统设计

作者:

张洪刚, 苑秉成, 徐瑜, ZHANG Hong-gang, YUAN Bing-cheng, XU Yu

作者单位:

刊名:

海军工程大学兵器工程系,武汉,430033

电子器件

英文刊名:

CHINESE JOURNAL OF ELECTRON DEVICES

年,卷(期):

2009,32(1)

2次

被引用次数:

参考文献(8条)

1.马秀娟.牛进鹏 高速数据采集系统中的FPGA的设计[期刊论文]-电子器件 2007(08)

2.SanDisk Secure Digital Card Product Manual Version2.2 2004

3.Altera Lte Cyclone Device Handbook Volume 1 2005 2005

4.王诚.吴继华 Altera FPGA/CPLD设计(基础篇、高级篇) 2005

5.毕战坤.张弈猛 基于逻辑设计的高速CRC并行算法研究及其FPGA实现[期刊论文]-仪器仪表学报 2007(12)

6.邓剑.杨晓非 FAT文件系统原理及实现[期刊论文]-计算机与数字工程 2005(09)

7.陈惠滨.陈仅星 嵌入式文件系统在移动数据采集器中的实现[期刊论文]-电子器件 2005(09)

8.SD Memory Card Specifications-FILE SYSTEM SPECIFICATION Version1.01 2001

引证文献(2条)

1.魏来.周穗华.刘旭东 基于SD卡的水声信号采集系统设计[期刊论文]-海洋技术 2010(2)

2.袁芬艳.刘敬彪 SD卡在工业数据采集中的应用[期刊论文]-电子器件 2010(5)

本文链接:http://d.g.wanfangdata.com.cn/Periodical_dzqj200901054.aspx

�