芯片的识别

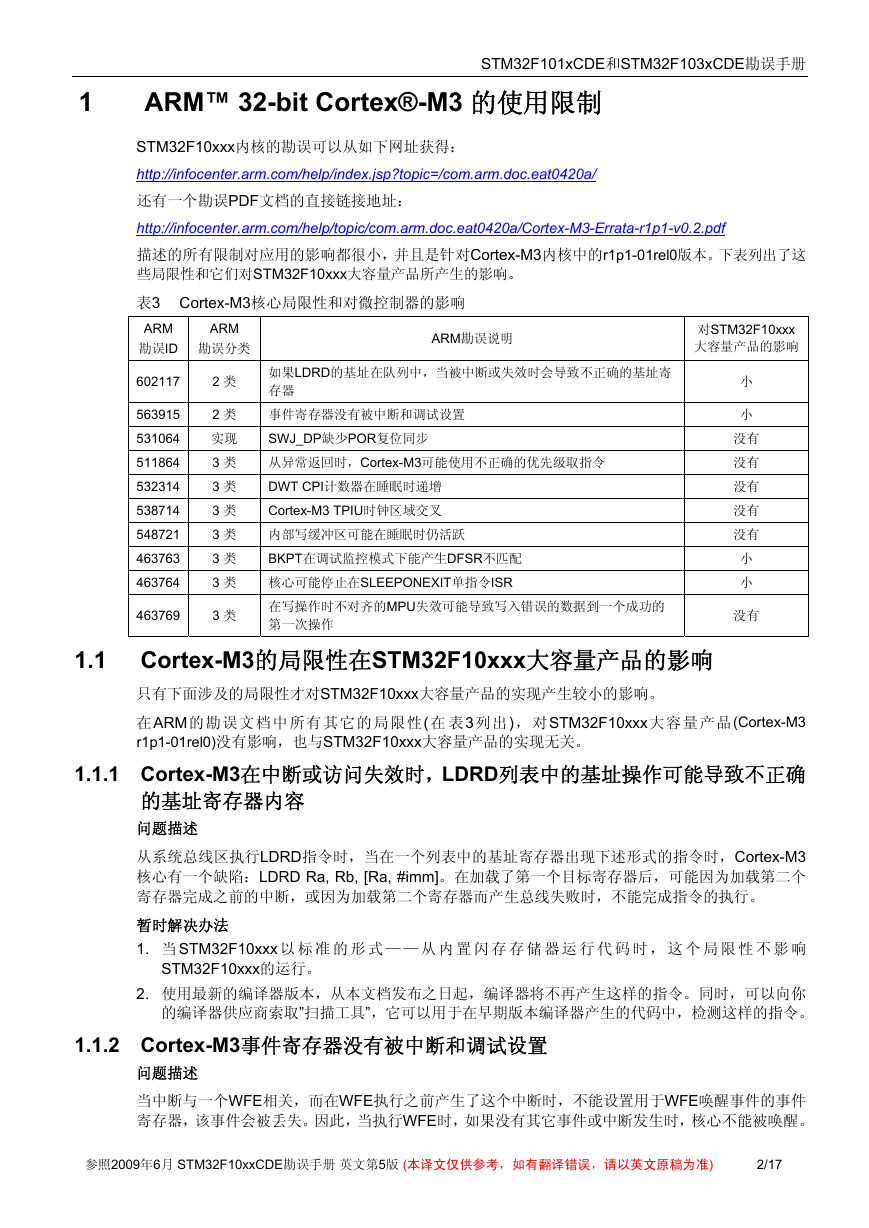

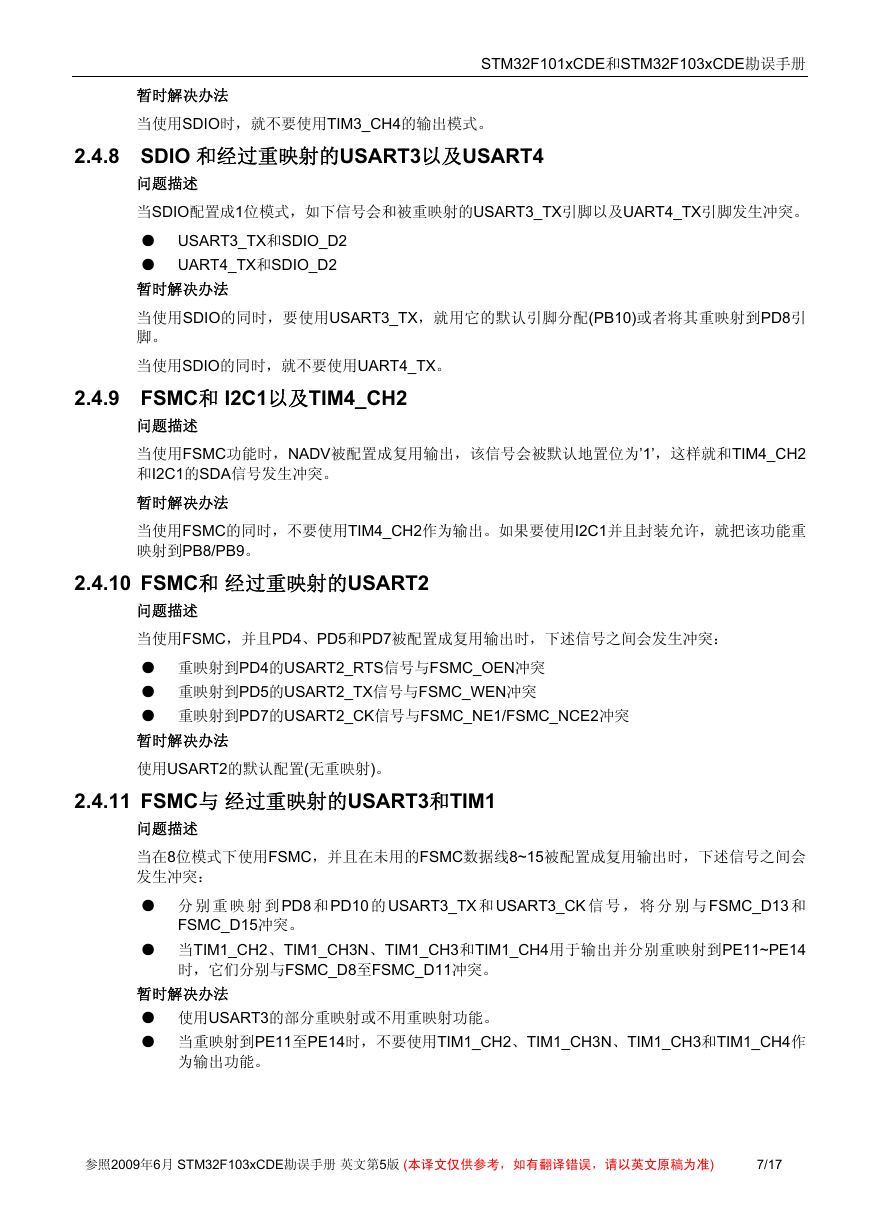

1 ARM™ 32-bit Cortex®-M3 的使用限制

1.1 Cortex-M3的局限性在STM32F10xxx大容量产品的影响

1.1.1 Cortex-M3在中断或访问失效时,LDRD列表中的基址操作可能导致不正确的基址寄存器内容

1.1.2 Cortex-M3事件寄存器没有被中断和调试设置

1.1.3 Cortex-M3的BKPT在调试监控模式下可以导致DFSR不匹配

1.1.4 Cortex-M3可能在使用SLEEPONEXIT功能时,在单指令的ISR中停止

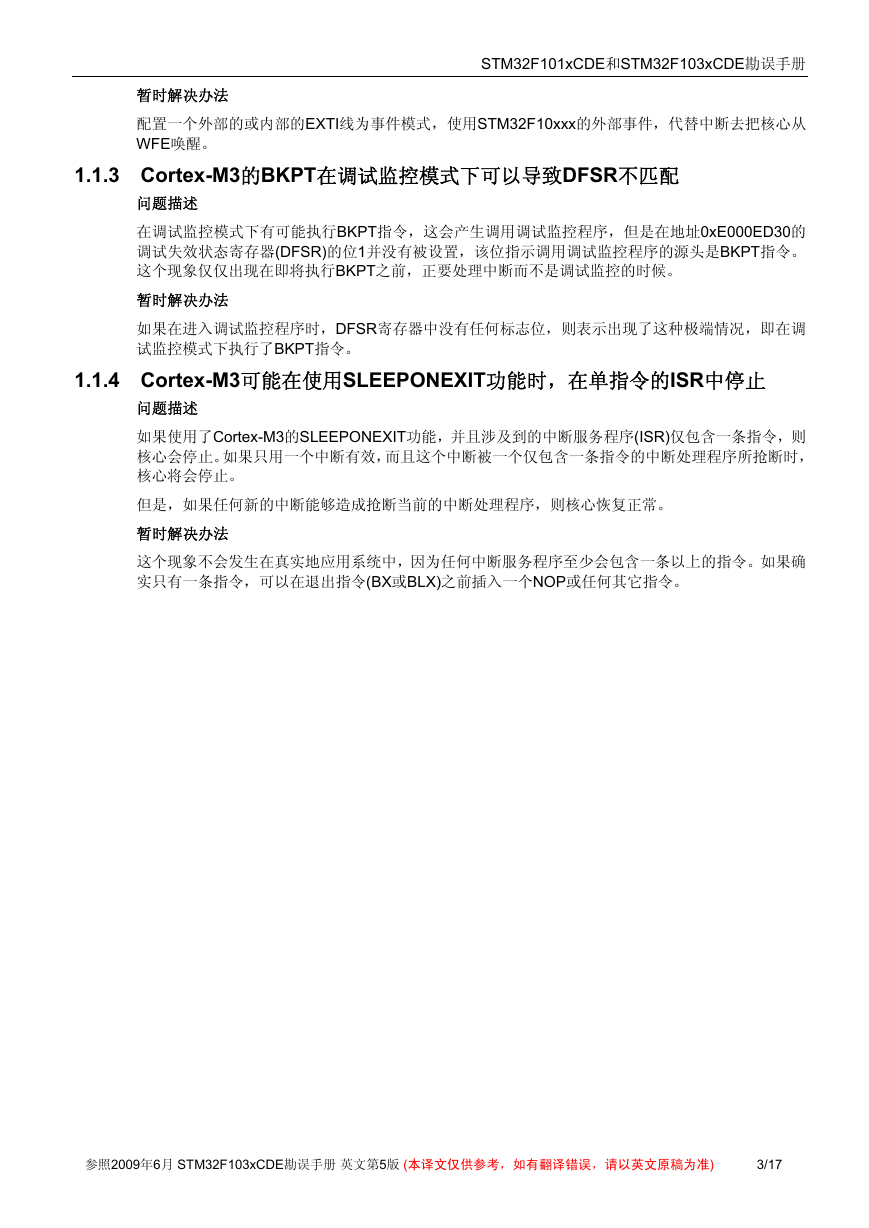

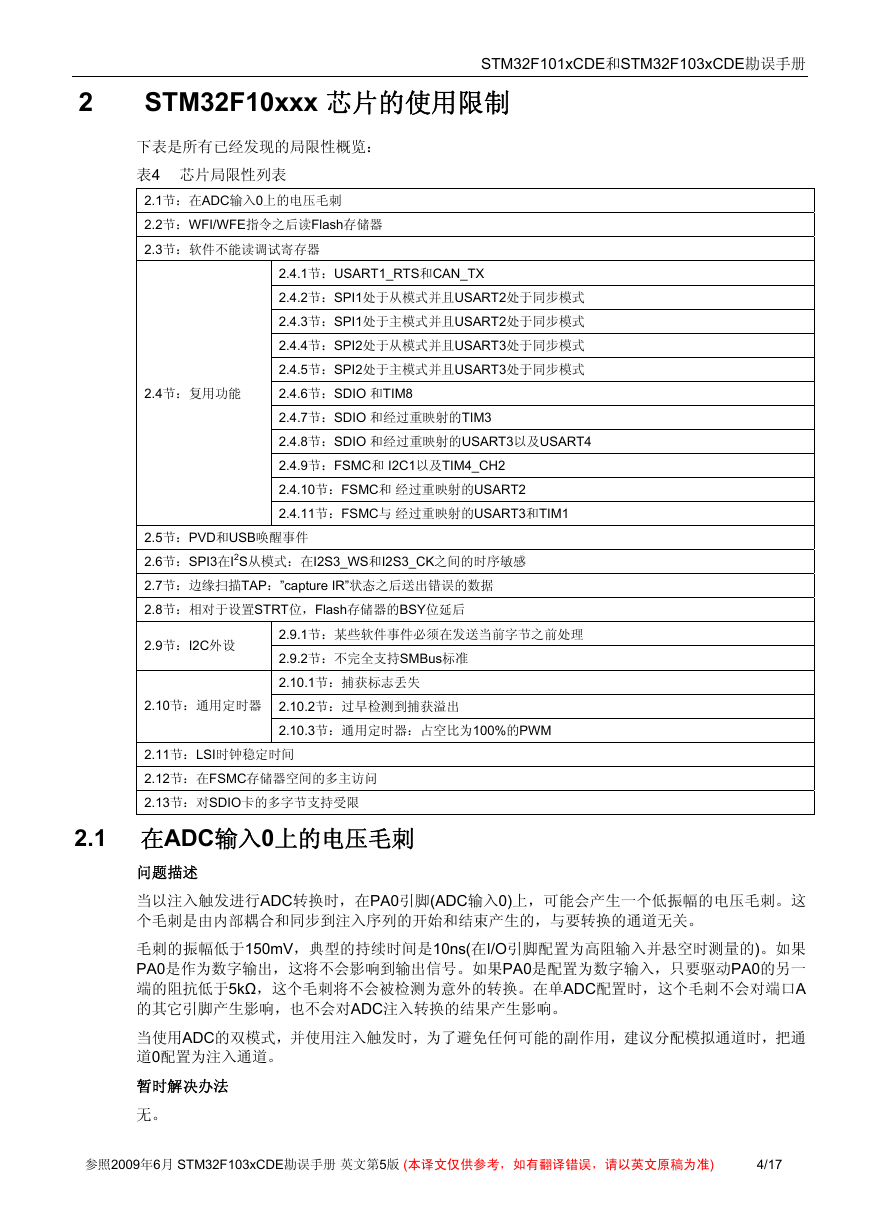

2 STM32F10xxx 芯片的使用限制

2.1 在ADC输入0上的电压毛刺

2.2 WFI/WFE指令之后读Flash存储器

2.3 软件不能读调试寄存器

2.4 复用功能

2.4.1 USART1_RTS和CAN_TX

2.4.2 SPI1处于从模式并且USART2处于同步模式

2.4.3 SPI1处于主模式并且USART2处于同步模式

2.4.4 SPI2处于从模式并且USART3处于同步模式

2.4.5 SPI2处于主模式并且USART3处于同步模式

2.4.6 SDIO 和TIM8

2.4.7 SDIO 和经过重映射的TIM3

2.4.8 SDIO 和经过重映射的USART3以及USART4

2.4.9 FSMC和 I2C1以及TIM4_CH2

2.4.10 FSMC和 经过重映射的USART2

2.4.11 FSMC与 经过重映射的USART3和TIM1

2.5 PVD和USB唤醒事件

2.6 SPI3在I2S从模式:在I2S3_WS和I2S3_CK之间的时序敏感

2.7 边缘扫描TAP:”capture IR”状态之后送出错误的数据

2.8 相对于设置STRT位,Flash存储器的BSY位延后

2.9 I2C外设

2.9.1 某些软件事件必须在发送当前字节之前处理

2.9.2 不完全支持SMBus标准

2.10 通用定时器

2.10.1 捕获标志丢失

2.10.2 过早检测到捕获溢出

2.10.3 通用定时器:占空比为100%的PWM

2.11 LSI时钟稳定时间

2.12 在FSMC存储器空间的多主访问

2.13 对SDIO卡的多字节支持受限

2.14 在SPI2/I2S2从模式和16位帧模式下意外产生TXE

附录A 产品上版本号标示

版本修订记录