w

Stereo CODEC With Speaker Driver

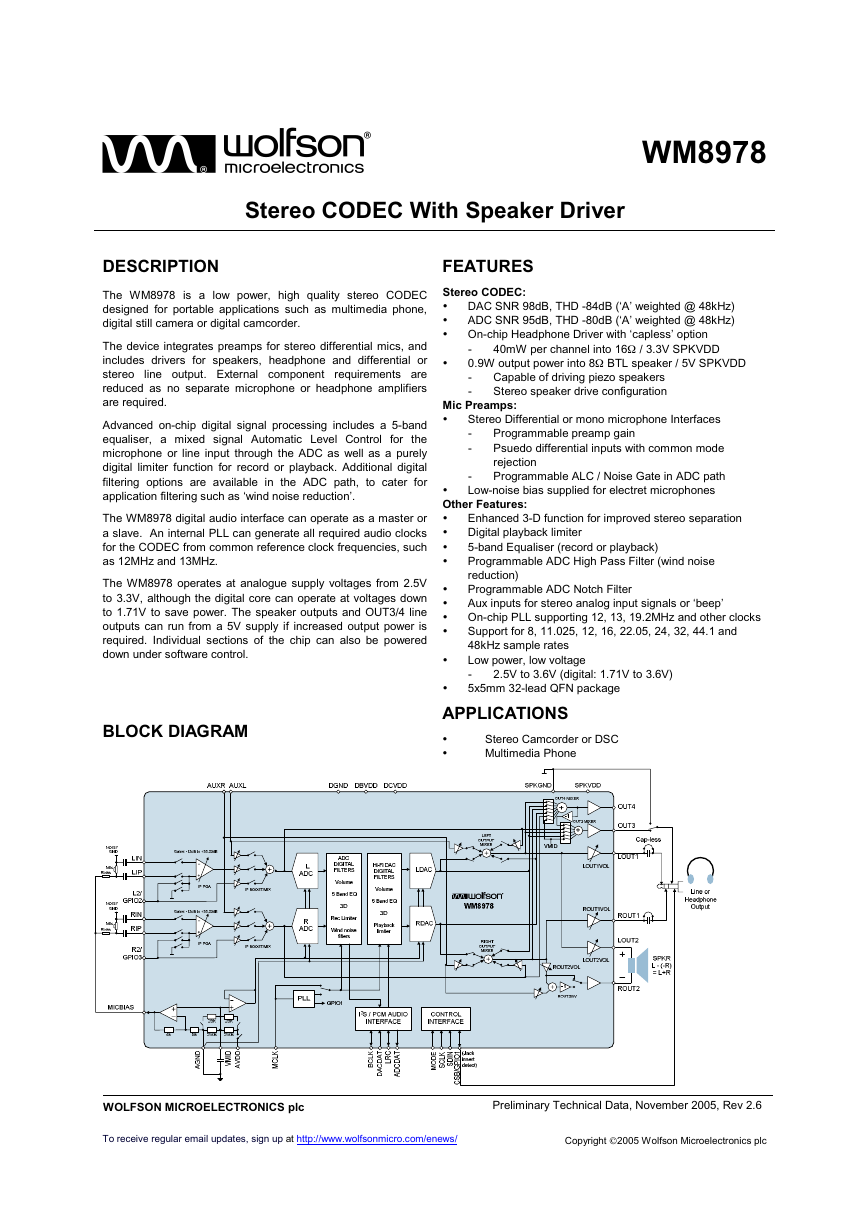

WM8978

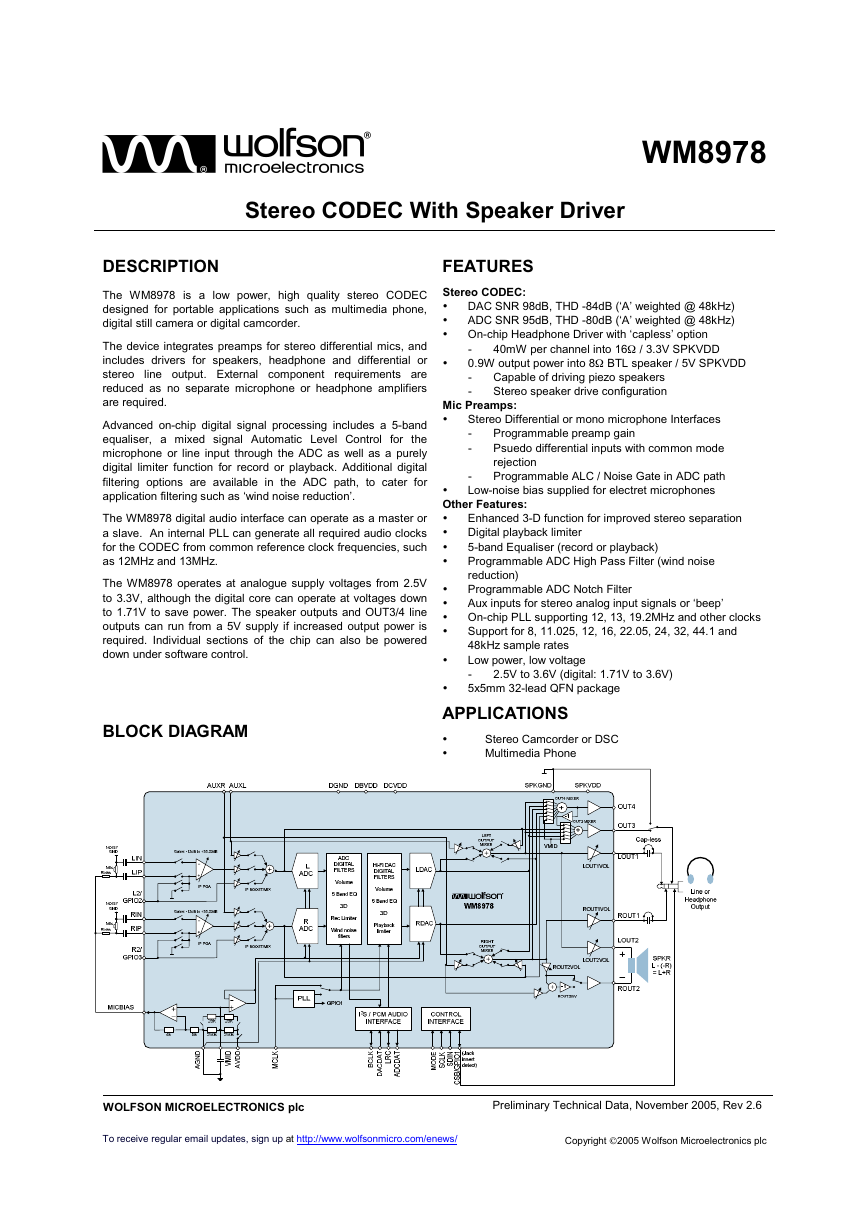

DESCRIPTION

The WM8978 is a low power, high quality stereo CODEC

designed for portable applications such as multimedia phone,

digital still camera or digital camcorder.

The device integrates preamps for stereo differential mics, and

includes drivers for speakers, headphone and differential or

stereo

line output. External component requirements are

reduced as no separate microphone or headphone amplifiers

are required.

Advanced on-chip digital signal processing includes a 5-band

equaliser, a mixed signal Automatic Level Control for the

microphone or line input through the ADC as well as a purely

digital limiter function for record or playback. Additional digital

filtering options are available in the ADC path, to cater for

application filtering such as ‘wind noise reduction’.

The WM8978 digital audio interface can operate as a master or

a slave. An internal PLL can generate all required audio clocks

for the CODEC from common reference clock frequencies, such

as 12MHz and 13MHz.

The WM8978 operates at analogue supply voltages from 2.5V

to 3.3V, although the digital core can operate at voltages down

to 1.71V to save power. The speaker outputs and OUT3/4 line

outputs can run from a 5V supply if increased output power is

required. Individual sections of the chip can also be powered

down under software control.

BLOCK DIAGRAM

FEATURES

Stereo CODEC:

•

•

• On-chip Headphone Driver with ‘capless’ option

DAC SNR 98dB, THD -84dB (‘A’ weighted @ 48kHz)

ADC SNR 95dB, THD -80dB (‘A’ weighted @ 48kHz)

•

40mW per channel into 16Ω / 3.3V SPKVDD

-

0.9W output power into 8Ω BTL speaker / 5V SPKVDD

-

-

Capable of driving piezo speakers

Stereo speaker drive configuration

Mic Preamps:

•

Stereo Differential or mono microphone Interfaces

-

-

Programmable preamp gain

Psuedo differential inputs with common mode

rejection

Programmable ALC / Noise Gate in ADC path

-

Low-noise bias supplied for electret microphones

•

Other Features:

•

•

•

•

Enhanced 3-D function for improved stereo separation

Digital playback limiter

5-band Equaliser (record or playback)

Programmable ADC High Pass Filter (wind noise

reduction)

Programmable ADC Notch Filter

Aux inputs for stereo analog input signals or ‘beep’

•

•

• On-chip PLL supporting 12, 13, 19.2MHz and other clocks

•

Support for 8, 11.025, 12, 16, 22.05, 24, 32, 44.1 and

48kHz sample rates

Low power, low voltage

-

5x5mm 32-lead QFN package

2.5V to 3.6V (digital: 1.71V to 3.6V)

•

•

APPLICATIONS

•

•

Stereo Camcorder or DSC

Multimedia Phone

WOLFSON MICROELECTRONICS plc

To receive regular email updates, sign up at http://www.wolfsonmicro.com/enews/

Preliminary Technical Data, November 2005, Rev 2.6

Copyright 2005 Wolfson Microelectronics plc

�

WM8978

Preliminary Technical Data

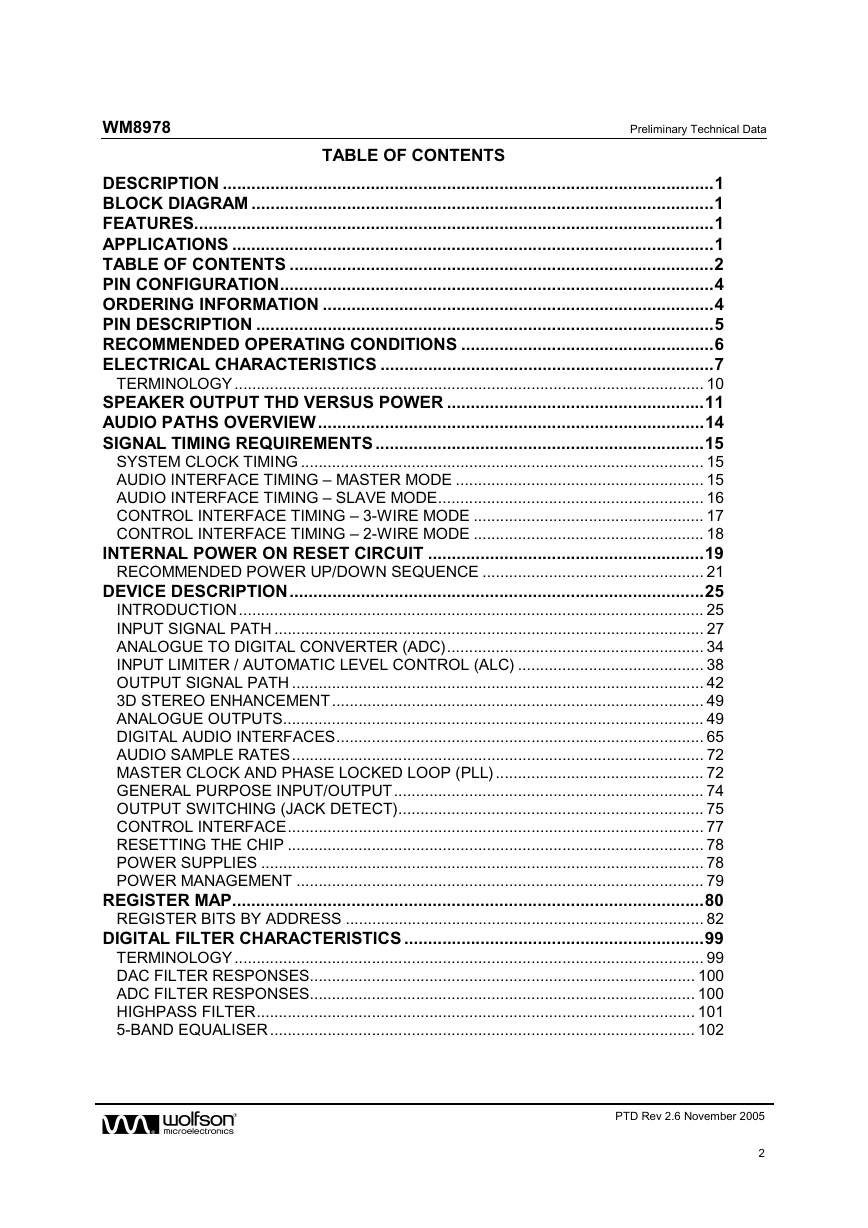

TABLE OF CONTENTS

DESCRIPTION .......................................................................................................1

BLOCK DIAGRAM .................................................................................................1

FEATURES.............................................................................................................1

APPLICATIONS .....................................................................................................1

TABLE OF CONTENTS .........................................................................................2

PIN CONFIGURATION...........................................................................................4

ORDERING INFORMATION ..................................................................................4

PIN DESCRIPTION ................................................................................................5

RECOMMENDED OPERATING CONDITIONS .....................................................6

ELECTRICAL CHARACTERISTICS ......................................................................7

TERMINOLOGY .......................................................................................................... 10

SPEAKER OUTPUT THD VERSUS POWER ......................................................11

AUDIO PATHS OVERVIEW .................................................................................14

SIGNAL TIMING REQUIREMENTS .....................................................................15

SYSTEM CLOCK TIMING ........................................................................................... 15

AUDIO INTERFACE TIMING – MASTER MODE ........................................................ 15

AUDIO INTERFACE TIMING – SLAVE MODE............................................................ 16

CONTROL INTERFACE TIMING – 3-WIRE MODE .................................................... 17

CONTROL INTERFACE TIMING – 2-WIRE MODE .................................................... 18

INTERNAL POWER ON RESET CIRCUIT ..........................................................19

RECOMMENDED POWER UP/DOWN SEQUENCE .................................................. 21

DEVICE DESCRIPTION.......................................................................................25

INTRODUCTION......................................................................................................... 25

INPUT SIGNAL PATH ................................................................................................. 27

ANALOGUE TO DIGITAL CONVERTER (ADC).......................................................... 34

INPUT LIMITER / AUTOMATIC LEVEL CONTROL (ALC) .......................................... 38

OUTPUT SIGNAL PATH ............................................................................................. 42

3D STEREO ENHANCEMENT.................................................................................... 49

ANALOGUE OUTPUTS............................................................................................... 49

DIGITAL AUDIO INTERFACES................................................................................... 65

AUDIO SAMPLE RATES............................................................................................. 72

MASTER CLOCK AND PHASE LOCKED LOOP (PLL) ............................................... 72

GENERAL PURPOSE INPUT/OUTPUT...................................................................... 74

OUTPUT SWITCHING (JACK DETECT)..................................................................... 75

CONTROL INTERFACE.............................................................................................. 77

RESETTING THE CHIP .............................................................................................. 78

POWER SUPPLIES .................................................................................................... 78

POWER MANAGEMENT ............................................................................................ 79

REGISTER MAP...................................................................................................80

REGISTER BITS BY ADDRESS ................................................................................. 82

DIGITAL FILTER CHARACTERISTICS ...............................................................99

TERMINOLOGY .......................................................................................................... 99

DAC FILTER RESPONSES....................................................................................... 100

ADC FILTER RESPONSES....................................................................................... 100

HIGHPASS FILTER................................................................................................... 101

5-BAND EQUALISER ................................................................................................ 102

w

PTD Rev 2.6 November 2005

2

�

Preliminary Technical Data

APPLICATION INFORMATION..........................................................................106

RECOMMENDED EXTERNAL COMPONENTS........................................................ 106

PACKAGE DIAGRAM ........................................................................................107

IMPORTANT NOTICE ........................................................................................108

ADDRESS: ................................................................................................................ 108

WM8978

w

PTD Rev 2.6 November 2005

3

�

WM8978

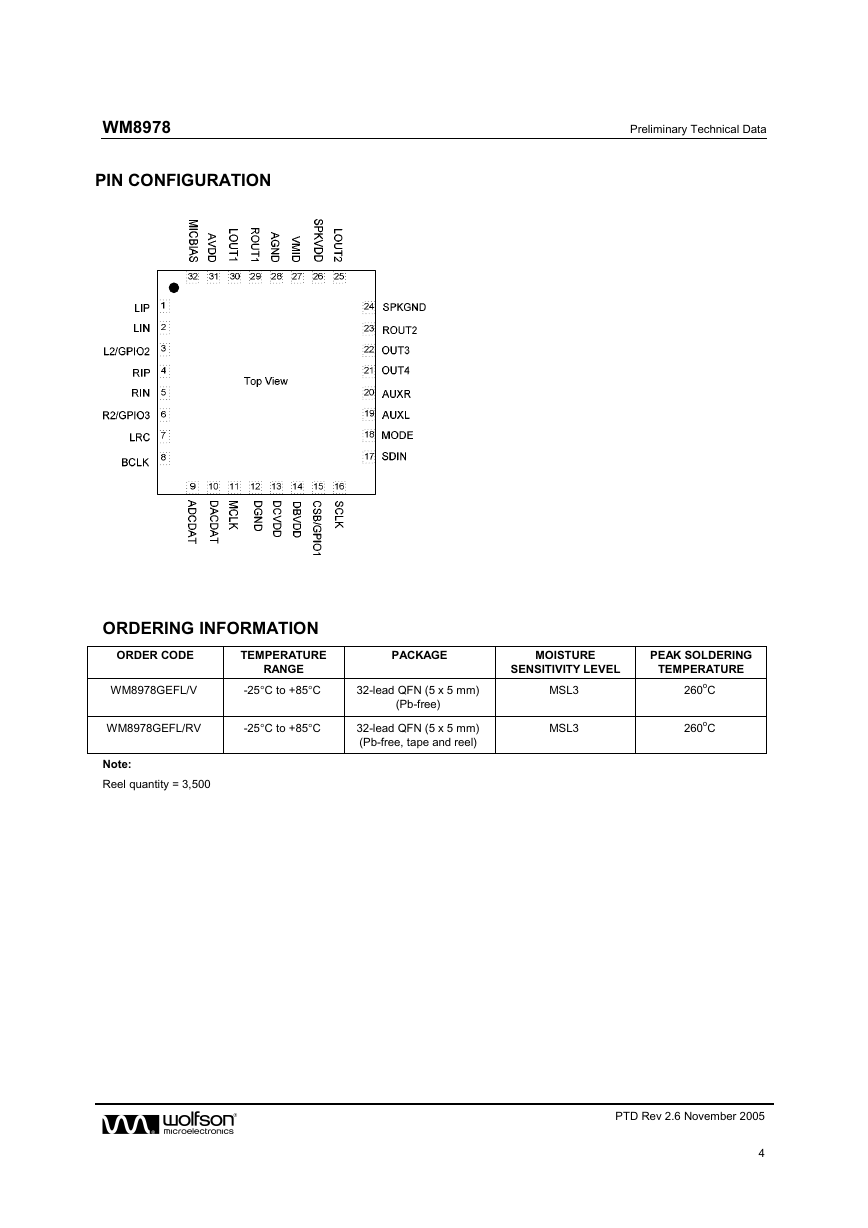

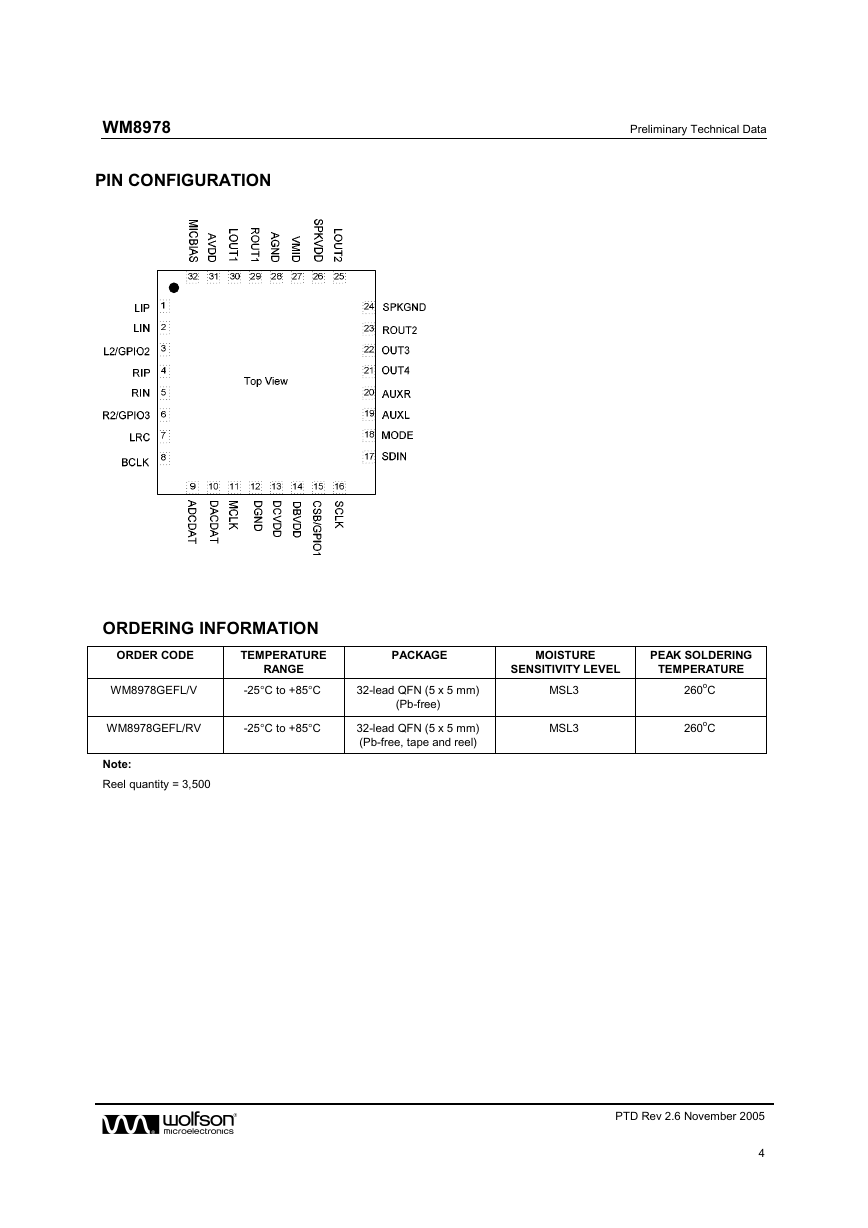

PIN CONFIGURATION

Preliminary Technical Data

ORDERING INFORMATION

ORDER CODE

TEMPERATURE

PACKAGE

WM8978GEFL/V

RANGE

-25°C to +85°C

WM8978GEFL/RV

-25°C to +85°C

Note:

Reel quantity = 3,500

MOISTURE

SENSITIVITY LEVEL

PEAK SOLDERING

TEMPERATURE

32-lead QFN (5 x 5 mm)

(Pb-free)

32-lead QFN (5 x 5 mm)

(Pb-free, tape and reel)

MSL3

MSL3

260oC

260oC

w

PTD Rev 2.6 November 2005

4

�

Preliminary Technical Data

PIN DESCRIPTION

WM8978

PIN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

NAME

LIP

LIN

L2/GPIO2

RIP

RIN

R2/GPIO3

LRC

BCLK

ADCDAT

DACDAT

MCLK

DGND

DCVDD

DBVDD

TYPE

Analogue input

Analogue input

Analogue input

Analogue input

Analogue input

Analogue input

Digital Input / Output

Digital Input / Output

Digital Output

Digital Input

Digital Input

Supply

Supply

Supply

CSB/GPIO1

Digital Input / Output

SCLK

SDIN

MODE

AUXL

AUXR

OUT4

OUT3

ROUT2

SPKGND

LOUT2

SPKVDD

VMID

AGND

ROUT1

LOUT1

AVDD

Digital Input

Digital Input / Output

Digital Input

Analogue input

Analogue input

Analogue Output

Analogue Output

Analogue Output

Supply

Analogue Output

Supply

Reference

Supply

Analogue Output

Analogue Output

Supply

MICBIAS

Analogue Output

DESCRIPTION

Left Mic Pre-amp positive input

Left Mic Pre-amp negative input

Left channel line input/secondary mic pre-amp positive input/GPIO2 pin

Right Mic Pre-amp positive input

Right Mic Pre-amp negative input

Right channel line input/secondary mic pre-amp positive input/GPIO3

pin

DAC and ADC Sample Rate Clock

Digital Audio Port Clock

ADC Digital Audio Data Output

DAC Digital Audio Data Input

Master Clock Input

Digital ground

Digital core logic supply

Digital buffer (I/O) supply

3-Wire Control Interface Chip Select / GPIO1 pin

3-Wire Control Interface Clock Input / 2-Wire Control Interface Clock

Input

3-Wire Control Interface Data Input / 2-Wire Control Interface Data Input

Control Interface Selection

Left Auxillary input

Right Auxillary input

Buffered midrail Headphone pseudo-ground, or Right line output or MONO

mix output

Buffered midrail Headphone pseudo-ground, or Left line output

Second right output, or BTL speaker driver positive output

Speaker ground (feeds speaker amp and OUT3/OUT4)

Second left output, or BTL speaker driver negative output

Speaker supply (feed speaker amp only)

Decoupling for ADC and DAC reference voltage

Analogue ground (feeds ADC and DAC)

Headphone or Line Output Right

Headphone or Line Output Left

Analogue supply (feeds ADC and DAC)

Microphone Bias

Note:

It is recommended that the QFN ground paddle should be connected to analogue ground on the application PCB.

w

PTD Rev 2.6 November 2005

5

�

WM8978

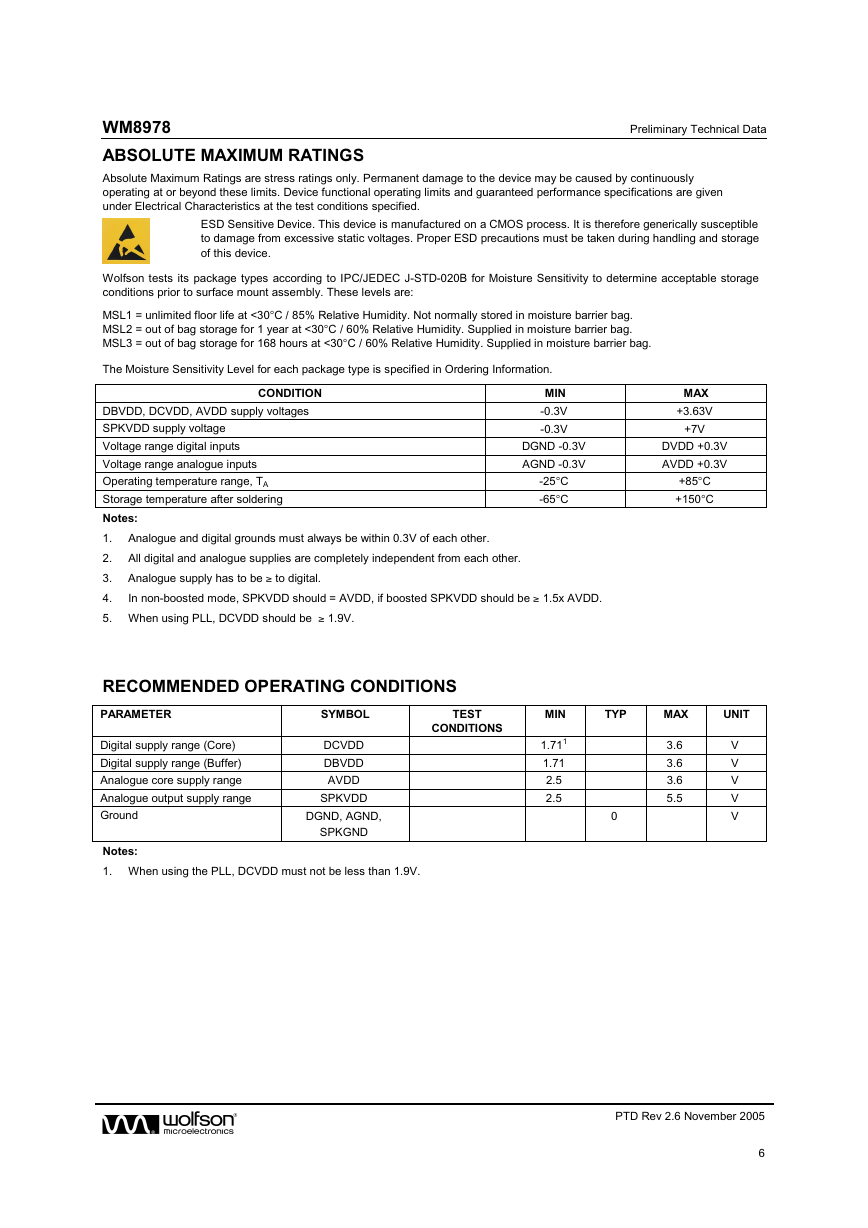

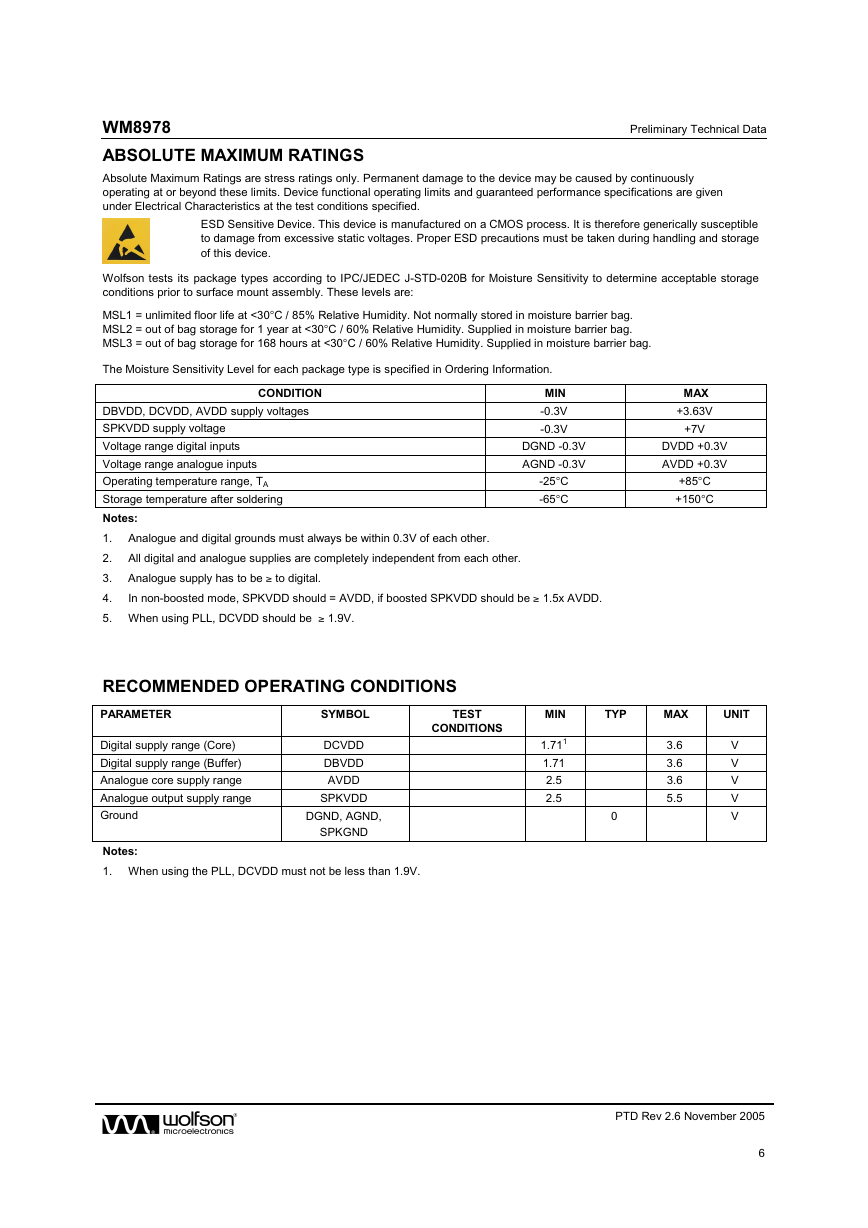

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously

operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given

under Electrical Characteristics at the test conditions specified.

Preliminary Technical Data

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible

to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage

of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage

conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

MIN

-0.3V

-0.3V

DGND -0.3V

AGND -0.3V

-25°C

-65°C

CONDITION

DBVDD, DCVDD, AVDD supply voltages

SPKVDD supply voltage

Voltage range digital inputs

Voltage range analogue inputs

Operating temperature range, TA

Storage temperature after soldering

Notes:

1. Analogue and digital grounds must always be within 0.3V of each other.

2. All digital and analogue supplies are completely independent from each other.

3. Analogue supply has to be ≥ to digital.

4.

5. When using PLL, DCVDD should be ≥ 1.9V.

In non-boosted mode, SPKVDD should = AVDD, if boosted SPKVDD should be ≥ 1.5x AVDD.

MAX

+3.63V

+7V

DVDD +0.3V

AVDD +0.3V

+85°C

+150°C

RECOMMENDED OPERATING CONDITIONS

PARAMETER

Digital supply range (Core)

Digital supply range (Buffer)

Analogue core supply range

Analogue output supply range

Ground

SYMBOL

DCVDD

DBVDD

AVDD

SPKVDD

DGND, AGND,

SPKGND

Notes:

1. When using the PLL, DCVDD must not be less than 1.9V.

TEST

CONDITIONS

MIN

TYP

MAX

UNIT

1.711

1.71

2.5

2.5

0

3.6

3.6

3.6

5.5

V

V

V

V

V

w

PTD Rev 2.6 November 2005

6

�

Preliminary Technical Data

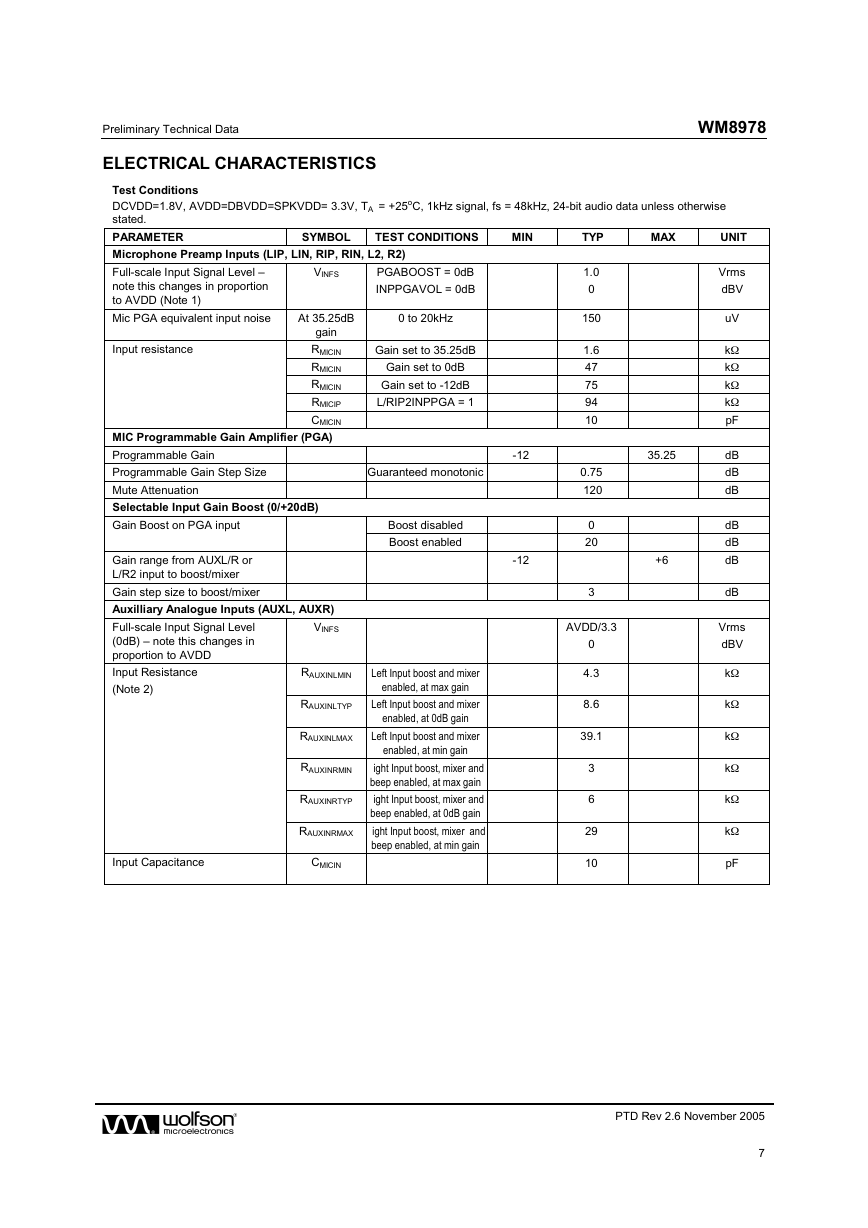

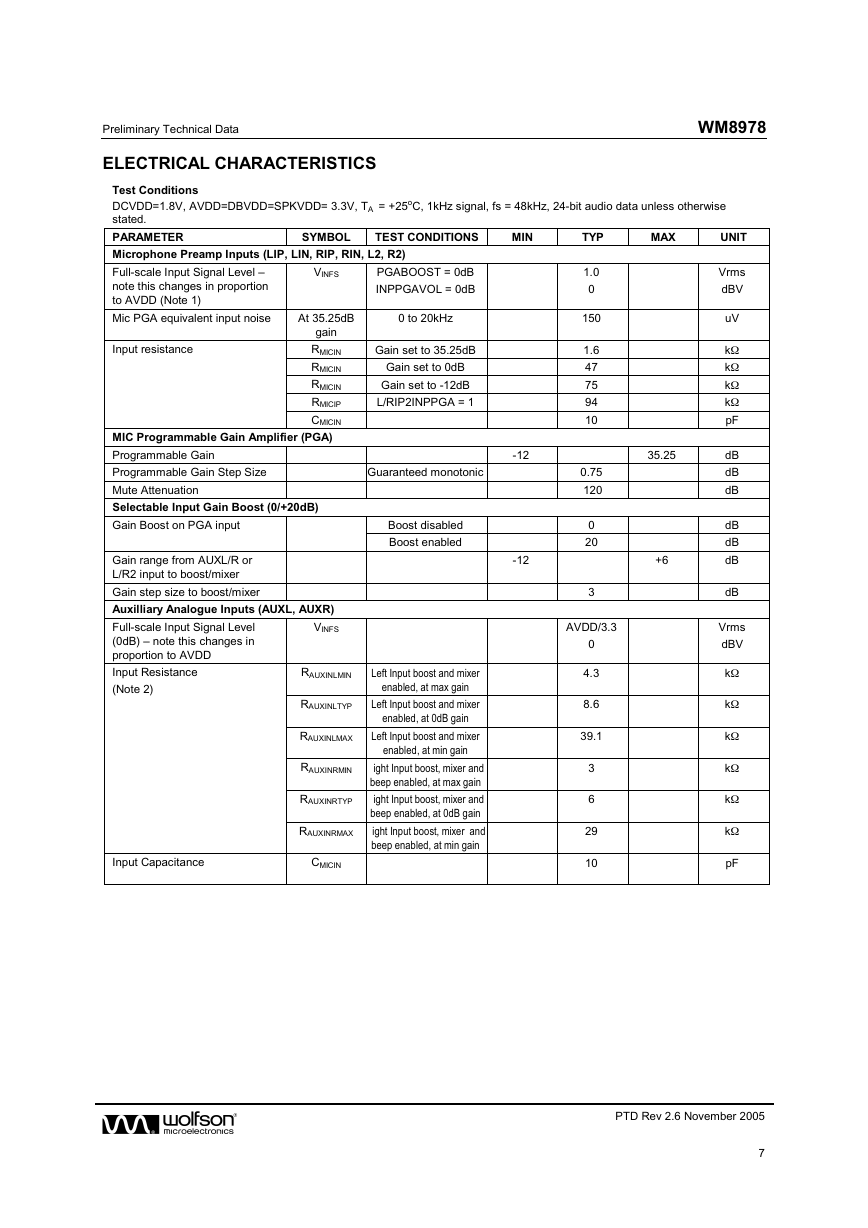

ELECTRICAL CHARACTERISTICS

WM8978

Test Conditions

DCVDD=1.8V, AVDD=DBVDD=SPKVDD= 3.3V, TA = +25oC, 1kHz signal, fs = 48kHz, 24-bit audio data unless otherwise

stated.

PARAMETER

Microphone Preamp Inputs (LIP, LIN, RIP, RIN, L2, R2)

Full-scale Input Signal Level –

note this changes in proportion

to AVDD (Note 1)

Mic PGA equivalent input noise

PGABOOST = 0dB

INPPGAVOL = 0dB

TEST CONDITIONS

At 35.25dB

0 to 20kHz

SYMBOL

VINFS

1.0

0

150

MIN

TYP

MAX

UNIT

Vrms

dBV

uV

Input resistance

gain

RMICIN

RMICIN

RMICIN

RMICIP

CMICIN

MIC Programmable Gain Amplifier (PGA)

Programmable Gain

Programmable Gain Step Size

Mute Attenuation

Selectable Input Gain Boost (0/+20dB)

Gain Boost on PGA input

Gain range from AUXL/R or

L/R2 input to boost/mixer

Gain step size to boost/mixer

Auxilliary Analogue Inputs (AUXL, AUXR)

Full-scale Input Signal Level

VINFS

(0dB) – note this changes in

proportion to AVDD

Input Resistance

(Note 2)

RAUXINLMIN

Gain set to 35.25dB

Gain set to 0dB

Gain set to -12dB

L/RIP2INPPGA = 1

Guaranteed monotonic

Boost disabled

Boost enabled

Left Input boost and mixer

enabled, at max gain

RAUXINLTYP

Left Input boost and mixer

enabled, at 0dB gain

RAUXINLMAX

Left Input boost and mixer

RAUXINRMIN

RAUXINRTYP

RAUXINRMAX

enabled, at min gain

ight Input boost, mixer and

beep enabled, at max gain

ight Input boost, mixer and

beep enabled, at 0dB gain

ight Input boost, mixer and

beep enabled, at min gain

Input Capacitance

CMICIN

-12

-12

1.6

47

75

94

10

0.75

120

0

20

3

AVDD/3.3

0

4.3

8.6

39.1

3

6

29

10

35.25

+6

kΩ

kΩ

kΩ

kΩ

pF

dB

dB

dB

dB

dB

dB

dB

Vrms

dBV

kΩ

kΩ

kΩ

kΩ

kΩ

kΩ

pF

w

PTD Rev 2.6 November 2005

7

�

WM8978

Test Conditions

DCVDD=1.8V, AVDD=DBVDD=SPKVDD= 3.3V, TA = +25oC, 1kHz signal, fs = 48kHz, 24-bit audio data unless otherwise

stated.

PARAMETER

Automatic Level Control (ALC)

Target Record Level

Programmable gain

Gain Hold Time (Note 3,5)

TEST CONDITIONS

MCLK = 12.288MHz

SYMBOL

-1.5

-22.5

-12

35.25

0, 2.67, 5.33, 10.67, … , 43691

(time doubles with each step)

tHOLD

MAX

TYP

MIN

UNIT

dB

ms

Preliminary Technical Data

Gain Ramp-Up (Decay) Time

(Note 4,5)

tDCY

Gain Ramp-Down (Attack) Time

(Note 4,5)

tATK

(Note 3)

ALCMODE=0 (ALC),

MCLK=12.288MHz

(Note 3)

ALCMODE=1 (limiter),

MCLK=12.288MHz

(Note 3)

ALCMODE=0 (ALC),

MCLK=12.288MHz

(Note 3)

ALCMODE=1 (limiter),

MCLK=12.288MHz

(Note 3)

3.3, 6.6, 13.1, … , 3360

(time doubles with each step)

0.73, 1.45, 2.91, … , 744

(time doubles with each step)

0.83, 1.66, 3.33, … , 852

(time doubles with each step)

0.18, 0.36, 0.73, … , 186

(time doubles with each step)

Mute Attenuation

Analogue to Digital Converter (ADC)

Signal to Noise Ratio (Note 6)

Total Harmonic Distortion

(Note 7)

Channel Separation (Note 9)

Digital to Analogue Converter (DAC) to Line-Out (LOUT1, ROUT1 with 10kΩΩΩΩ / 50pF load)

Full-scale output

A-weighted, 0dB gain

PGA gains set to 0dB,

1kHz input signal

-3dBFS input

SNR

THD

120

95

-84

110

AVDD/3.3

SNR

THD

Signal to Noise Ratio (Note 6)

Total Harmonic Distortion

(Note 7)

Channel Separation (Note 8)

Output Mixers (LMX1, RMX1)

PGA gain range into mixer

PGA gain step into mixer

Analogue Outputs (LOUT1, ROUT1, LOUT2, ROUT2)

Programmable Gain range

Programmable Gain step size

Mute attenuation

Headphone Output (LOUT1, ROUT1 with 32ΩΩΩΩ load)

0dB full scale output voltage

Signal to Noise Ratio

Total Harmonic Distortion

SNR

THD

OUT34BOOST=0

PGA gains set to 0dB,

OUT34BOOST=1

A-weighted

RL = 10kΩ

full-scale signal

1kHz signal

Monotonic

1kHz, full scale signal

A-weighted

RL = 16Ω, Po=20mW

AVDD=3.3V

RL = 32 Ω, Po=20mW

AVDD=3.3V

-15

-57

1.5x

(AVDD/3.3)

98

-84

110

0

3

0

1

85

AVDD/3.3

102

0.003

-92

0.008

- 82

+6

+6

ms

ms

dB

dB

dB

dB

Vrms

dB

dB

dB

dB

dB

dB

dB

dB

Vrms

dB

%

dB

%

dB

w

PTD Rev 2.6 November 2005

8

�