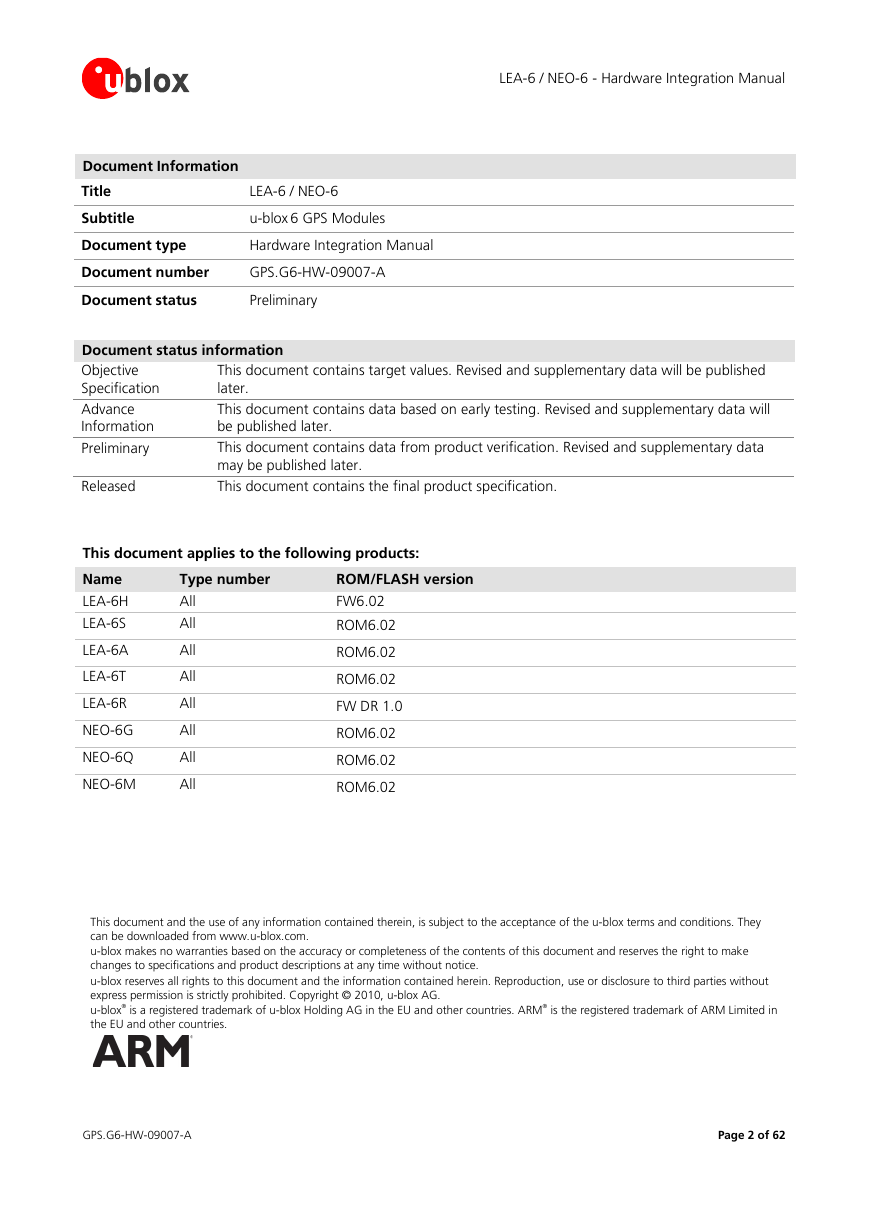

Preface

Contents

1 Hardware description

1.1 Overview

1.2 Architecture

1.3 Power management

1.3.1.1 VCC - main power

1.3.1.2 V_BCKP - backup battery

1.3.1.3 VDD_USB - USB interface power supply

1.3.2.1 Maximum Performance mode

1.3.2.2 Eco mode

1.3.2.3 Power Save mode

1.4 Antenna supply - V_ANT (LEA-6)

1.5 System functions

1.6 Interfaces

1.6.2.1 USB external components

1.6.3.1 Communicating to an I2C EEPROM with the GPS receiver as I2C master

1.6.4.1 Connecting SPI FLASH memory

1.6.4.2 SPI communication (connecting to an SPI master)

1.6.4.3 Pin configuration with module as one of several slaves

1.7 I/O pins

2 Design-in

2.1 Design-in checklist

2.2 LEA-6 design

2.2.2.1 Second time pulse for LEA-6T

2.2.2.2 LEA-6R considerations

2.3 NEO-6 design

2.4 Layout

2.4.2 Placement

2.4.3 Antenna connection and grounding plane design

2.5 Antenna and antenna supervisor

2.5.3 Active antenna

2.5.4.1 Short circuit protection

2.5.5.1 Short and open circuit active antenna supervisor

3 Product handling

3.1 Packaging, shipping, storage and moisture preconditioning

3.2 Soldering

3.3 EOS/ESD/EMI Precautions

3.3.8.1 Isolation between GPS and GSM antenna

3.3.8.2 Increasing jamming immunity

3.3.8.3 In-band jamming

3.3.8.4 Out-band jamming

4 Product testing

4.1 u-blox in-series production test

4.2 Test parameters for OEM manufacturer

4.3 System sensitivity test

Appendix

A Abbreviations

B Migration to u-blox-6 receivers

B.1 Checklist for migration

B.2 Software migration

B.3 Hardware Migration

B.3.1 Hardware Migration: ANTARIS 4 ( u-blox 6

B.3.2 Hardware Migration: u-blox 5 ( u-blox 6

B.4 Migration of LEA modules

B.4.1 Migration from LEA-4 to LEA-6

B.4.2 Migration from LEA-5 to LEA-6

B.5 Migration of NEO modules

B.5.1 Migration from NEO-4S to NEO-6

B.5.2 Migration from NEO-5 to NEO-6

C Interface Backgrounder

C.1 DDC Interface

C.1.1 Addresses, roles and modes

C.1.2 DDC troubleshooting

C.2 SPI Interface

C.2.1 SPI basics

Related documents

Revision history

Revision history (Internal)

Contact