7 Series FPGAs

SelectIO Resources

User Guide

UG471 (v1.10) May 8, 2018

�

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL

WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF

MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether

in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising

under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or

consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action

brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.

Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. You may not

reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and

conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and

support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any

application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps.

AUTOMOTIVE APPLICATIONS DISCLAIMER

AUTOMOTIVE PRODUCTS (IDENTIFIED AS “XA” IN THE PART NUMBER) ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT

OF AIRBAGS OR FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE (“SAFETY APPLICATION”) UNLESS THERE

IS A SAFETY CONCEPT OR REDUNDANCY FEATURE CONSISTENT WITH THE ISO 26262 AUTOMOTIVE SAFETY STANDARD

(“SAFETY DESIGN”). CUSTOMER SHALL, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE PRODUCTS,

THOROUGHLY TEST SUCH SYSTEMS FOR SAFETY PURPOSES. USE OF PRODUCTS IN A SAFETY APPLICATION WITHOUT A

SAFETY DESIGN IS FULLY AT THE RISK OF CUSTOMER, SUBJECT ONLY TO APPLICABLE LAWS AND REGULATIONS GOVERNING

LIMITATIONS ON PRODUCT LIABILITY.

© Copyright 2011–2018 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Zynq, Artix, Kintex, Spartan, ISE and other designated brands included

herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

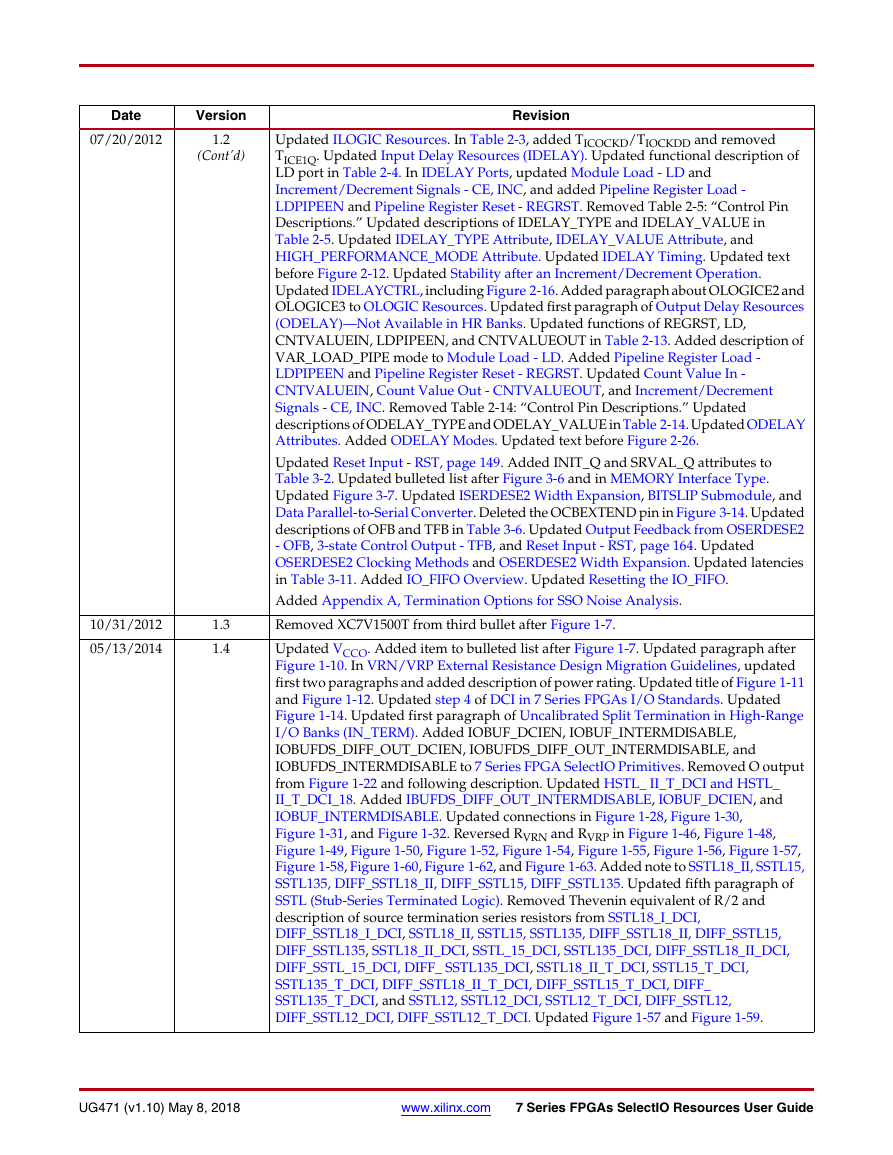

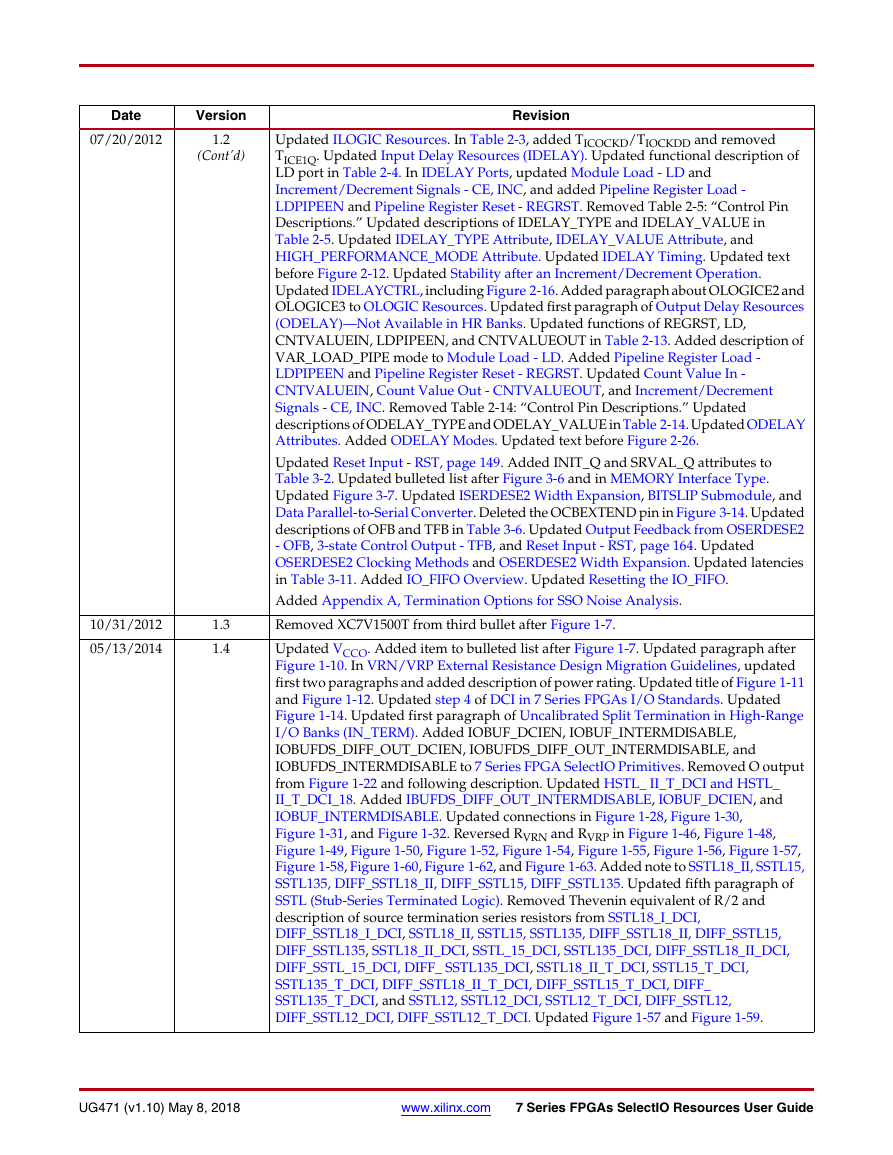

Revision History

The following table shows the revision history for this document.

Date

Version

03/01/2011

04/06/2011

05/31/2011

1.0

1.0.1

1.1

07/20/2012

1.2

Revision

Initial Xilinx release.

Updated disclaimer and copyright sections on page 2.

Added New Features. Updated the example device including Figure 1-15 and the

partgen example on page 24. Added VRN/VRP External Resistance Design Migration

Guidelines.

Updated the BITSLIP Submodule section including Figure 3-12. Removed Figure 3-13:

Bits from Data Input Stream (D) of Figure 3-12.

Updated paragraph before Table 1-1. Added LVDS signaling to Table 1-1. Updated

VCCO and VCCAUX_IO. Updated Xilinx DCI. Removed VCCINT. Added Match_cycle

Configuration Option, DCIUpdateMode Configuration Option, DCIRESET Primitive,

and Special DCI Requirements for Some Banks. Updated DCI Cascading. Updated DCI

cascading guidelines after Figure 1-7. Updated table note in Table 1-3. Added

Uncalibrated Split Termination in High-Range I/O Banks (IN_TERM). Updated 7 Series

FPGA SelectIO Primitives. Added DCI_CASCADE Constraint and VCCAUX_IO

Constraint. Updated IBUF_LOW_PWR Attribute, Output Slew Rate Attributes, Output

Drive Strength Attributes, PULLUP/PULLDOWN/KEEPER Attribute for IBUF,

OBUFT, and IOBUF, and 7 Series FPGA I/O Resource VHDL/Verilog Examples. Put

Internal VREF inside Differential Termination Attribute, page 49. Updated DRIVE

attribute in Table 1-10. Updated titles of Figure 1-41 through Figure 1-44. Updated LVDS

and LVDS_25 (Low Voltage Differential Signaling), including adding Figure 1-72.

Added IN_TERM attribute to SSTL (Stub-Series Terminated Logic). Added table note to

Table 1-55. Added Simultaneous Switching Outputs.

7 Series FPGAs SelectIO Resources User Guide

www.xilinx.com

UG471 (v1.10) May 8, 2018

�

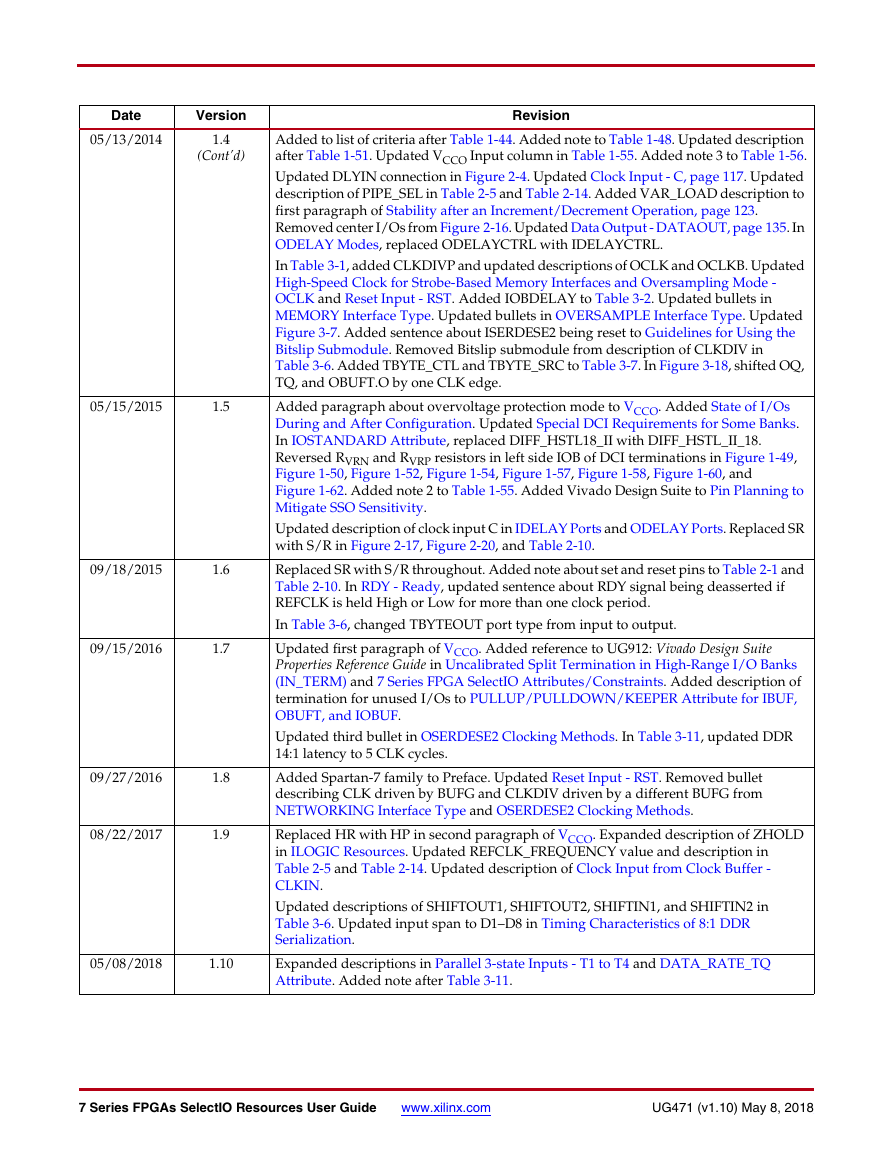

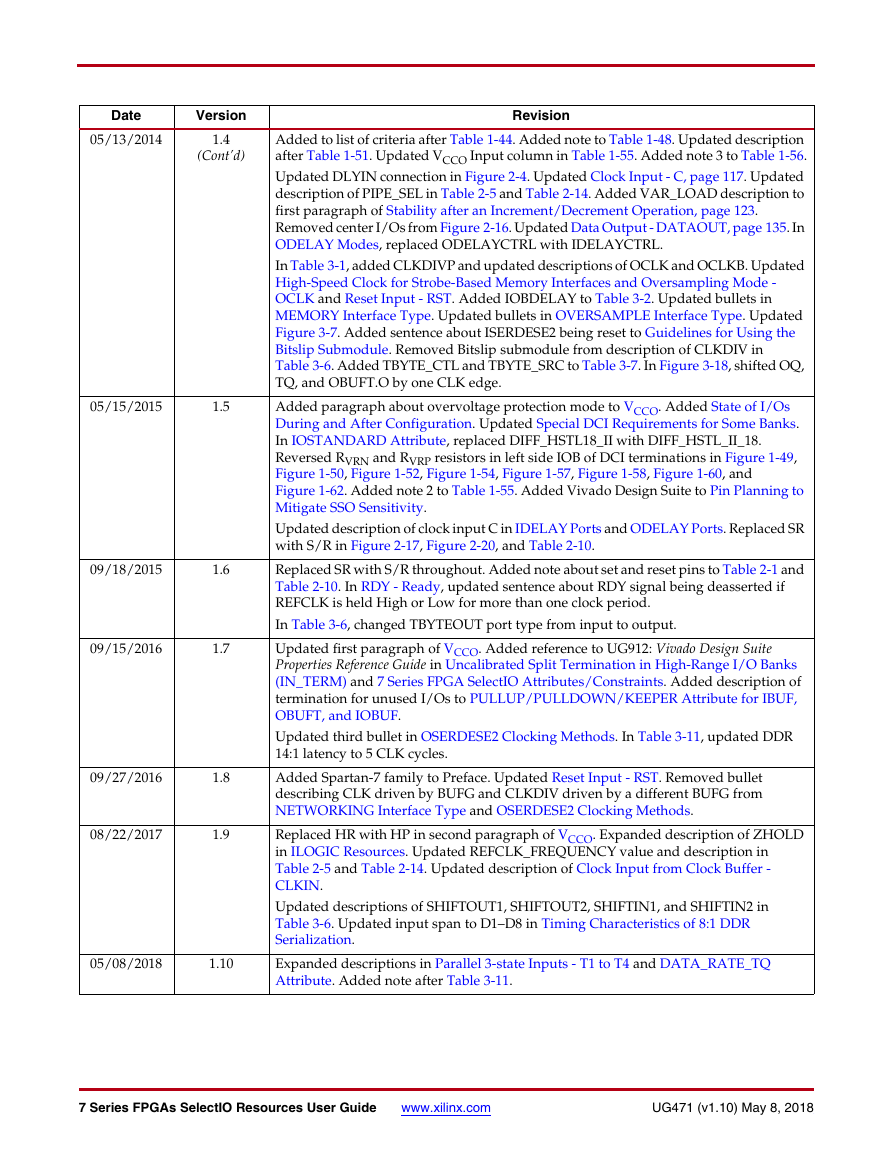

Date

07/20/2012

Version

1.2

(Cont’d)

10/31/2012

05/13/2014

1.3

1.4

Revision

Updated ILOGIC Resources. In Table 2-3, added TICOCKD/TIOCKDD and removed

TICE1Q. Updated Input Delay Resources (IDELAY). Updated functional description of

LD port in Table 2-4. In IDELAY Ports, updated Module Load - LD and

Increment/Decrement Signals - CE, INC, and added Pipeline Register Load -

LDPIPEEN and Pipeline Register Reset - REGRST. Removed Table 2-5: “Control Pin

Descriptions.” Updated descriptions of IDELAY_TYPE and IDELAY_VALUE in

Table 2-5. Updated IDELAY_TYPE Attribute, IDELAY_VALUE Attribute, and

HIGH_PERFORMANCE_MODE Attribute. Updated IDELAY Timing. Updated text

before Figure 2-12. Updated Stability after an Increment/Decrement Operation.

Updated IDELAYCTRL, including Figure 2-16. Added paragraph about OLOGICE2 and

OLOGICE3 to OLOGIC Resources. Updated first paragraph of Output Delay Resources

(ODELAY)—Not Available in HR Banks. Updated functions of REGRST, LD,

CNTVALUEIN, LDPIPEEN, and CNTVALUEOUT in Table 2-13. Added description of

VAR_LOAD_PIPE mode to Module Load - LD. Added Pipeline Register Load -

LDPIPEEN and Pipeline Register Reset - REGRST. Updated Count Value In -

CNTVALUEIN, Count Value Out - CNTVALUEOUT, and Increment/Decrement

Signals - CE, INC. Removed Table 2-14: “Control Pin Descriptions.” Updated

descriptions of ODELAY_TYPE and ODELAY_VALUE in Table 2-14. Updated ODELAY

Attributes. Added ODELAY Modes. Updated text before Figure 2-26.

Updated Reset Input - RST, page 149. Added INIT_Q and SRVAL_Q attributes to

Table 3-2. Updated bulleted list after Figure 3-6 and in MEMORY Interface Type.

Updated Figure 3-7. Updated ISERDESE2 Width Expansion, BITSLIP Submodule, and

Data Parallel-to-Serial Converter. Deleted the OCBEXTEND pin in Figure 3-14. Updated

descriptions of OFB and TFB in Table 3-6. Updated Output Feedback from OSERDESE2

- OFB, 3-state Control Output - TFB, and Reset Input - RST, page 164. Updated

OSERDESE2 Clocking Methods and OSERDESE2 Width Expansion. Updated latencies

in Table 3-11. Added IO_FIFO Overview. Updated Resetting the IO_FIFO.

Added Appendix A, Termination Options for SSO Noise Analysis.

Removed XC7V1500T from third bullet after Figure 1-7.

Updated VCCO. Added item to bulleted list after Figure 1-7. Updated paragraph after

Figure 1-10. In VRN/VRP External Resistance Design Migration Guidelines, updated

first two paragraphs and added description of power rating. Updated title of Figure 1-11

and Figure 1-12. Updated step 4 of DCI in 7 Series FPGAs I/O Standards. Updated

Figure 1-14. Updated first paragraph of Uncalibrated Split Termination in High-Range

I/O Banks (IN_TERM). Added IOBUF_DCIEN, IOBUF_INTERMDISABLE,

IOBUFDS_DIFF_OUT_DCIEN, IOBUFDS_DIFF_OUT_INTERMDISABLE, and

IOBUFDS_INTERMDISABLE to 7 Series FPGA SelectIO Primitives. Removed O output

from Figure 1-22 and following description. Updated HSTL_ II_T_DCI and HSTL_

II_T_DCI_18. Added IBUFDS_DIFF_OUT_INTERMDISABLE, IOBUF_DCIEN, and

IOBUF_INTERMDISABLE. Updated connections in Figure 1-28, Figure 1-30,

Figure 1-31, and Figure 1-32. Reversed RVRN and RVRP in Figure 1-46, Figure 1-48,

Figure 1-49, Figure 1-50, Figure 1-52, Figure 1-54, Figure 1-55, Figure 1-56, Figure 1-57,

Figure 1-58, Figure 1-60, Figure 1-62, and Figure 1-63. Added note to SSTL18_II, SSTL15,

SSTL135, DIFF_SSTL18_II, DIFF_SSTL15, DIFF_SSTL135. Updated fifth paragraph of

SSTL (Stub-Series Terminated Logic). Removed Thevenin equivalent of R/2 and

description of source termination series resistors from SSTL18_I_DCI,

DIFF_SSTL18_I_DCI, SSTL18_II, SSTL15, SSTL135, DIFF_SSTL18_II, DIFF_SSTL15,

DIFF_SSTL135, SSTL18_II_DCI, SSTL_15_DCI, SSTL135_DCI, DIFF_SSTL18_II_DCI,

DIFF_SSTL_15_DCI, DIFF_ SSTL135_DCI, SSTL18_II_T_DCI, SSTL15_T_DCI,

SSTL135_T_DCI, DIFF_SSTL18_II_T_DCI, DIFF_SSTL15_T_DCI, DIFF_

SSTL135_T_DCI, and SSTL12, SSTL12_DCI, SSTL12_T_DCI, DIFF_SSTL12,

DIFF_SSTL12_DCI, DIFF_SSTL12_T_DCI. Updated Figure 1-57 and Figure 1-59.

UG471 (v1.10) May 8, 2018

www.xilinx.com

7 Series FPGAs SelectIO Resources User Guide

�

Date

05/13/2014

Version

1.4

(Cont’d)

05/15/2015

1.5

09/18/2015

1.6

09/15/2016

1.7

09/27/2016

08/22/2017

1.8

1.9

05/08/2018

1.10

Revision

Added to list of criteria after Table 1-44. Added note to Table 1-48. Updated description

after Table 1-51. Updated VCCO Input column in Table 1-55. Added note 3 to Table 1-56.

Updated DLYIN connection in Figure 2-4. Updated Clock Input - C, page 117. Updated

description of PIPE_SEL in Table 2-5 and Table 2-14. Added VAR_LOAD description to

first paragraph of Stability after an Increment/Decrement Operation, page 123.

Removed center I/Os from Figure 2-16. Updated Data Output - DATAOUT, page 135. In

ODELAY Modes, replaced ODELAYCTRL with IDELAYCTRL.

In Table 3-1, added CLKDIVP and updated descriptions of OCLK and OCLKB. Updated

High-Speed Clock for Strobe-Based Memory Interfaces and Oversampling Mode -

OCLK and Reset Input - RST. Added IOBDELAY to Table 3-2. Updated bullets in

MEMORY Interface Type. Updated bullets in OVERSAMPLE Interface Type. Updated

Figure 3-7. Added sentence about ISERDESE2 being reset to Guidelines for Using the

Bitslip Submodule. Removed Bitslip submodule from description of CLKDIV in

Table 3-6. Added TBYTE_CTL and TBYTE_SRC to Table 3-7. In Figure 3-18, shifted OQ,

TQ, and OBUFT.O by one CLK edge.

Added paragraph about overvoltage protection mode to VCCO. Added State of I/Os

During and After Configuration. Updated Special DCI Requirements for Some Banks.

In IOSTANDARD Attribute, replaced DIFF_HSTL18_II with DIFF_HSTL_II_18.

Reversed RVRN and RVRP resistors in left side IOB of DCI terminations in Figure 1-49,

Figure 1-50, Figure 1-52, Figure 1-54, Figure 1-57, Figure 1-58, Figure 1-60, and

Figure 1-62. Added note 2 to Table 1-55. Added Vivado Design Suite to Pin Planning to

Mitigate SSO Sensitivity.

Updated description of clock input C in IDELAY Ports and ODELAY Ports. Replaced SR

with S/R in Figure 2-17, Figure 2-20, and Table 2-10.

Replaced SR with S/R throughout. Added note about set and reset pins to Table 2-1 and

Table 2-10. In RDY - Ready, updated sentence about RDY signal being deasserted if

REFCLK is held High or Low for more than one clock period.

In Table 3-6, changed TBYTEOUT port type from input to output.

Updated first paragraph of VCCO. Added reference to UG912: Vivado Design Suite

Properties Reference Guide in Uncalibrated Split Termination in High-Range I/O Banks

(IN_TERM) and 7 Series FPGA SelectIO Attributes/Constraints. Added description of

termination for unused I/Os to PULLUP/PULLDOWN/KEEPER Attribute for IBUF,

OBUFT, and IOBUF.

Updated third bullet in OSERDESE2 Clocking Methods. In Table 3-11, updated DDR

14:1 latency to 5 CLK cycles.

Added Spartan-7 family to Preface. Updated Reset Input - RST. Removed bullet

describing CLK driven by BUFG and CLKDIV driven by a different BUFG from

NETWORKING Interface Type and OSERDESE2 Clocking Methods.

Replaced HR with HP in second paragraph of VCCO. Expanded description of ZHOLD

in ILOGIC Resources. Updated REFCLK_FREQUENCY value and description in

Table 2-5 and Table 2-14. Updated description of Clock Input from Clock Buffer -

CLKIN.

Updated descriptions of SHIFTOUT1, SHIFTOUT2, SHIFTIN1, and SHIFTIN2 in

Table 3-6. Updated input span to D1–D8 in Timing Characteristics of 8:1 DDR

Serialization.

Expanded descriptions in Parallel 3-state Inputs - T1 to T4 and DATA_RATE_TQ

Attribute. Added note after Table 3-11.

7 Series FPGAs SelectIO Resources User Guide

www.xilinx.com

UG471 (v1.10) May 8, 2018

�

Table of Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Chapter 1: SelectIO Resources

I/O Tile Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

New Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

SelectIO Resources Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

SelectIO Resources General Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7 Series FPGA I/O Bank Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Supply Voltages for the SelectIO Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

State of I/Os During and After Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

7 Series FPGA DCI—Only available in the HP I/O banks . . . . . . . . . . . . . . . . . . . . 19

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Xilinx DCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Match_cycle Configuration Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DCIUpdateMode Configuration Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DCIRESET Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Special DCI Requirements for Some Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

DCI Cascading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Controlled Impedance Driver (Source Termination) . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Controlled Impedance Driver with Half Impedance (Source Termination) . . . . . . . . 25

Split-Termination DCI (Thevenin Equivalent Termination to VCCO/2) . . . . . . . . . . 26

VRN/VRP External Resistance Design Migration Guidelines . . . . . . . . . . . . . . . . . . . 27

DCI and 3-state DCI (T_DCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

DCI in 7 Series FPGAs I/O Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

DCI Usage Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Uncalibrated Split Termination in High-Range I/O Banks (IN_TERM) . . . . . . . 33

7 Series FPGA SelectIO Primitives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

IBUF and IBUFG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

IBUF_IBUFDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

IBUF_INTERMDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

IBUFDS and IBUFGDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

IBUFDS_DIFF_OUT and IBUFGDS_DIFF_OUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

IBUFDS_DIFF_OUT_IBUFDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

IBUFDS_IBUFDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

IBUFDS_INTERMDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

IBUFDS_DIFF_OUT_INTERMDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

IOBUF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

IOBUF_DCIEN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

IOBUF_INTERMDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

IOBUFDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

IOBUFDS_DCIEN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

www.xilinx.com

5

Send Feedback�

IOBUFDS_DIFF_OUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

IOBUFDS_DIFF_OUT_DCIEN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

IOBUFDS_DIFF_OUT_INTERMDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

IOBUFDS_INTERMDISABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

OBUF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

OBUFDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

OBUFT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

OBUFTDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7 Series FPGA SelectIO Attributes/Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

DCI_CASCADE Constraint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Location Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

IOSTANDARD Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

IBUF_LOW_PWR Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Output Slew Rate Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Output Drive Strength Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

PULLUP/PULLDOWN/KEEPER Attribute for IBUF, OBUFT, and IOBUF . . . . . . . 49

Differential Termination Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Internal VREF. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

VCCAUX_IO Constraint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7 Series FPGA I/O Resource VHDL/Verilog Examples . . . . . . . . . . . . . . . . . . . . . . . . 51

Supported I/O Standards and Terminations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

LVTTL (Low Voltage TTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

LVCMOS (Low Voltage CMOS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

LVDCI (Low-Voltage Digitally Controlled Impedance) . . . . . . . . . . . . . . . . . . . . . . . . . 56

LVDCI_DV2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

HSLVDCI (High-Speed LVDCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

HSTL (High-Speed Transceiver Logic) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

HSTL_ I and HSTL_ I_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

HSTL_I_12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

HSTL_ I_DCI and HSTL_ I_DCI_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

HSTL_ II and HSTL_ II_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

HSTL_ II_DCI and HSTL_ II_DCI_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

HSTL_ II_T_DCI and HSTL_ II_T_DCI_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

DIFF_HSTL_I and DIFF_HSTL_I_18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

DIFF_HSTL_I_DCI and DIFF_HSTL_I_DCI_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

DIFF_HSTL_ II and DIFF_HSTL_II_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

DIFF_HSTL_II_DCI and DIFF_HSTL_II_DCI_18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

DIFF_HSTL_II_T_DCI and DIFF_HSTL_II_T_DCI_18 . . . . . . . . . . . . . . . . . . . . . . . . . . 62

HSTL Class I (1.2V, 1.5V, or 1.8V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Differential HSTL Class I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

HSTL Class II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Differential HSTL Class II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

HSTL_II_T_DCI (1.5V or 1.8V) Split-Thevenin Termination (3-state) . . . . . . . . . . . . . 72

SSTL (Stub-Series Terminated Logic) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

SSTL15_R, SSTL135_R, DIFF_SSTL15_R, DIFF_SSTL135_R . . . . . . . . . . . . . . . . . . . . . . 76

SSTL18_I, DIFF_SSTL18_I. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

SSTL18_I_DCI, DIFF_SSTL18_I_DCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

SSTL18_II, SSTL15, SSTL135, DIFF_SSTL18_II, DIFF_SSTL15, DIFF_SSTL135. . . . . . . . 76

SSTL18_II_DCI, SSTL_15_DCI, SSTL135_DCI, DIFF_SSTL18_II_DCI, DIFF_SSTL_15_DCI, DIFF_

SSTL135_DCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

SSTL18_II_T_DCI, SSTL15_T_DCI, SSTL135_T_DCI, DIFF_SSTL18_II_T_DCI,

DIFF_SSTL15_T_DCI, DIFF_ SSTL135_T_DCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

SSTL12, SSTL12_DCI, SSTL12_T_DCI, DIFF_SSTL12, DIFF_SSTL12_DCI, DIFF_SSTL12_T_DCI77

6

www.xilinx.com

7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Send Feedback�

SSTL18, SSTL15, SSTL135, SSTL12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Differential SSTL18, SSTL15, SSTL135, SSTL12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

SSTL18, SSTL15, SSTL135, or SSTL12 (T_DCI) Termination . . . . . . . . . . . . . . . . . . . . . 84

HSUL_12 (High Speed Unterminated Logic) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

HSUL_12 and DIFF_HSUL_12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

HSUL_DCI_12 and DIFF_HSUL_12_DCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

HSUL_12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Differential HSUL_12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

MOBILE_DDR (Low Power DDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Summary of Memory Interface IOSTANDARDs and Attributes Supported . . . . . . . 88

LVDS and LVDS_25 (Low Voltage Differential Signaling) . . . . . . . . . . . . . . . . . . . . . . 91

Transmitter Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Receiver Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

RSDS (Reduced Swing Differential Signaling) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Mini-LVDS (Mini Low Voltage Differential Signaling) . . . . . . . . . . . . . . . . . . . . . . . . . 94

PPDS (Point-to-Point Differential Signaling) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

TMDS (Transition Minimized Differential Signaling) . . . . . . . . . . . . . . . . . . . . . . . . . . 95

BLVDS (Bus LVDS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Rules for Combining I/O Standards in the Same Bank . . . . . . . . . . . . . . . . . . . . . . . 97

Simultaneous Switching Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Pin Planning to Mitigate SSO Sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Chapter 2: SelectIO Logic Resources

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

ILOGIC Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Combinatorial Input Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Input DDR Overview (IDDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

OPPOSITE_EDGE Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

SAME_EDGE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

SAME_EDGE_PIPELINED Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Input DDR Resources (IDDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

IDDR VHDL and Verilog Templates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

ILOGIC Timing Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

ILOGIC Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

ILOGIC Timing Characteristics, DDR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Input Delay Resources (IDELAY). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

IDELAYE2 Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

IDELAY Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

IDELAY Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

IDELAY Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

IDELAY Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Stability after an Increment/Decrement Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

IDELAY VHDL and Verilog Instantiation Template . . . . . . . . . . . . . . . . . . . . . . . . . . 123

IDELAYCTRL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

IDELAYCTRL Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

IDELAYCTRL Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

IDELAYCTRL Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

IDELAYCTRL Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

IDELAYCTRL Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

IDELAYCTRL Usage and Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

OLOGIC Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

www.xilinx.com

7

Send Feedback�

Combinatorial Output Data and 3-State Control Path . . . . . . . . . . . . . . . . . . . . . . . . . 127

Output DDR Overview (ODDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

OPPOSITE_EDGE Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

SAME_EDGE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Clock Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Output DDR Primitive (ODDR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

ODDR VHDL and Verilog Templates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

OLOGIC Timing Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Output Delay Resources (ODELAY)—Not Available in HR Banks . . . . . . . . . . 134

ODELAYE2 Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

ODELAY Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

ODELAY Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

ODELAY Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

ODELAY Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Stability after an Increment/Decrement Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

ODELAY VHDL and Verilog Instantiation Template. . . . . . . . . . . . . . . . . . . . . . . . . . 141

Chapter 3: Advanced SelectIO Logic Resources

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Input Serial-to-Parallel Logic Resources (ISERDESE2) . . . . . . . . . . . . . . . . . . . . . . 143

ISERDESE2 Primitive (ISERDESE2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

ISERDESE2 Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Registered Outputs – Q1 to Q8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Combinatorial Output – O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Bitslip Operation - BITSLIP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Clock Enable Inputs - CE1 and CE2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

High-Speed Clock Input - CLK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

High-Speed Clock Input - CLKB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Divided Clock Input - CLKDIV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Serial Input Data from IOB - D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Serial Input Data from IDELAYE2 - DDLY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Serial Input Data from OSERDESE2 - OFB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

High-Speed Clock for Strobe-Based Memory Interfaces and

Oversampling Mode - OCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Reset Input - RST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

ISERDESE2 Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

DATA_RATE Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

DATA_WIDTH Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

INTERFACE_TYPE Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

NUM_CE Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

SERDES_MODE Attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

ISERDESE2 Clocking Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

NETWORKING Interface Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

MEMORY Interface Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

MEMORY_QDR Interface Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

OVERSAMPLE Interface Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

MEMORY_DDR3 Interface Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

ISERDESE2 Width Expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Guidelines for Expanding the Serial-to-Parallel Converter Bit Width . . . . . . . . . . . . . 155

ISERDESE2 Latencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Dynamic Clock Inversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

8

www.xilinx.com

7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Send Feedback�