LGDP4531

Rev 1.15

LGDP4531

720-Channel, 262,144-Color One-Chip Driver

with RAM, Power Supply and Gate Circuits

for Amorphous TFT-LCD Panels

Rev 1.15

2007-7-3

Description ...................................................................................................................................................4

Features ........................................................................................................................................................5

Block Diagram .............................................................................................................................................6

Pin Function .................................................................................................................................................7

PAD Arrangement.....................................................................................................................................11

PAD Coordinate ........................................................................................................................................12

Bump Arrangement ....................................................................................................................................18

Block Function ...........................................................................................................................................19

System Interface ....................................................................................................................................19

External Display Interface .....................................................................................................................19

Address Counter (AC) ...........................................................................................................................20

Graphics RAM (GRAM) .......................................................................................................................20

Grayscale Voltage Generating Circuit...................................................................................................20

Timing Generator ..................................................................................................................................20

Oscillator (OSC)....................................................................................................................................20

LCD Driver Circuit................................................................................................................................20

LCD Drive Power Supply Circuit..........................................................................................................20

Internal logic power supply regulator....................................................................................................20

GRAM Address MAP ................................................................................................................................21

Instructions.................................................................................................................................................29

Outline ...................................................................................................................................................29

Instruction Data Format.........................................................................................................................29

Instruction Description ..........................................................................................................................31

Index (IR) ..............................................................................................................................................31

Device code read (R00h) .......................................................................................................................31

Driver output control (R01h).................................................................................................................31

LCD Driving Wave Control (R02h) ......................................................................................................31

Entry Mode (R03h)................................................................................................................................32

Resizing Control (R04h)........................................................................................................................35

Display Control 1 (R07h) ......................................................................................................................36

Display Control 2 (R08h) ......................................................................................................................37

Display Control 3 (R09h) ......................................................................................................................38

Display Control 4 (R0Ah) .....................................................................................................................39

External Display Interface Control 1 (R0Ch) ........................................................................................40

Frame Maker Position (R0Dh) ..............................................................................................................42

External Display Interface Control 2 (R0Fh).........................................................................................42

Power Control 1 (R10h).........................................................................................................................43

Power Control 2 (R11h).........................................................................................................................45

Power Control 3 (R12h).........................................................................................................................46

Power Control 4 (R13h).........................................................................................................................47

Regulator Control (R15h).....................................................................................................................48

IPS Control (R16h)...............................................................................................................................49

RAM Address Set (Horizontal Address) (R20h) ...................................................................................50

1

�

LGDP4531

Rev 1.15

RAM Address Set (Vertical Address) (R21h) .......................................................................................50

Write Data to RAM (R22h) ..................................................................................................................51

Read Data from RAM (R22h) ...............................................................................................................54

Gamma Control 1-10 (R30h to R39h) ...................................................................................................55

EPROM Control Register 1 (R40h).......................................................................................................56

EPROM Control Register 2 (R41h).......................................................................................................56

EPROM Control Register 3 (R42h).......................................................................................................56

Window Horizontal RAM Address Start/End (R50h/R51h) .................................................................57

Window Vertical RAM Address Start/End (R52h/R53h)......................................................................57

Driver Output Control (R60h) ...............................................................................................................58

Base Image Display Control (R61h)......................................................................................................58

Vertical Scroll Control (R6Ah)..............................................................................................................58

Partial Image 1: Display Position (R80h) ..............................................................................................61

RAM Address (Start/End Line Address) (R81h/R82h) .........................................................................61

Partial Image 2: Display Position (R83h) ..............................................................................................61

RAM Address (Start/End Line Address) (R84h/R85h) .........................................................................61

Panel Interface Control 1 (R90h)...........................................................................................................62

Panel Interface Control 2 (R92h)...........................................................................................................63

Panel Interface Control 3 (R93h)...........................................................................................................64

Panel Interface Control 4 (R95h)...........................................................................................................64

Panel Interface Control 5 (R97h)...........................................................................................................66

Panel Interface Control 6 (R98h)...........................................................................................................67

Test Register 1 (RA0h)..........................................................................................................................67

Test Register 2 (RA1h)..........................................................................................................................68

Test Register 3 (RA2h)..........................................................................................................................68

Instruction List ...........................................................................................................................................69

Reset Function............................................................................................................................................71

Basic Mode operation of the LGDP4531 ...................................................................................................73

Interface and data format............................................................................................................................74

System Interface.........................................................................................................................................77

80-system 18-bit Bus Interface..............................................................................................................78

80-system 16-bit Bus Interface..............................................................................................................79

Data Transfer Synchronous in 16-bit Bus Interface operation...............................................................80

80-system 9-bit Bus Interface................................................................................................................81

Data Transfer Synchronous in 9-bit Bus Interface operation.................................................................82

80-system 8-bit Bus Interface................................................................................................................83

Data Transfer Synchronous in 8-bit Bus Interface operation.................................................................85

Serial Interface.......................................................................................................................................86

VSYNC Interface .......................................................................................................................................89

Notes in using the VSYNC interface.....................................................................................................91

External Display Interface..........................................................................................................................93

RGB Interface........................................................................................................................................93

Polarities of VSYNC, HSYNC, ENABLE, and DOTCLK Signals.......................................................94

RGB Interface Timing ...........................................................................................................................94

Moving Picture Display with the RGB Interface...................................................................................95

RAM access via system interface in RGB interface operation..............................................................96

6-bit RGB Interface ...............................................................................................................................97

Data Transfer Synchronization in 6-bit Bus Interface operation ...........................................................98

16-bit RGB Interface .............................................................................................................................99

18-bit RGB Interface ...........................................................................................................................100

Notes on Using the External Display Interface....................................................................................101

RAM Address and Display Position on the Panel ....................................................................................103

Restrictions in setting display control instruction................................................................................104

Screen setting.......................................................................................................................................104

Instruction setting example..................................................................................................................105

Resizing function......................................................................................................................................108

Resizing setting....................................................................................................................................108

2

�

LGDP4531

Rev 1.15

Notes to Resizing function...................................................................................................................109

FMARK function .....................................................................................................................................111

FMP setting example...........................................................................................................................112

Display operation synchronous data transfer using FMARK ..............................................................112

Window Address Function.......................................................................................................................114

EPROM Control.......................................................................................................................................115

Scan Mode Setting....................................................................................................................................117

8-color Display Mode...............................................................................................................................118

Line Inversion AC Drive..........................................................................................................................119

Frame-Frequency Adjustment Function...................................................................................................120

Relationship between the liquid crystal Drive Duty and the Frame Frequency...................................120

Partial Display Function...........................................................................................................................121

Liquid crystal panel interface timing........................................................................................................122

Internal clock operation .......................................................................................................................122

RGB Interface operation......................................................................................................................123

Oscillator ..................................................................................................................................................124

γ-Correction Function...............................................................................................................................125

Grayscale Amplifier Unit Configuration .............................................................................................126

γ-Correction Register...........................................................................................................................129

Ladder Resistors and 8-to-1 Selector...................................................................................................130

Power-supply Generating Circuit .............................................................................................................136

Power supply circuit connection example 1 (Vci1 = VciOUT)...........................................................136

Power supply circuit connection example2 (Vci1 = Vci direct input).................................................137

Specifications of Power-supply Circuit External Elements......................................................................138

Voltage Setting Pattern Diagram..............................................................................................................139

Power Supply Instruction Setting.............................................................................................................140

Instruction Setting ....................................................................................................................................141

Display ON/OFF sequence..................................................................................................................141

Sleep mode SET/EXIT sequences .......................................................................................................142

Deep standby mode IN/EXIT sequences ............................................................................................143

8-color mode setting ............................................................................................................................143

Parital Display setting..........................................................................................................................144

Absolute Maximum Ratings.....................................................................................................................145

Electrical Characteristics..........................................................................................................................146

DC Characteristics...............................................................................................................................146

80-System Bus Interface Timing Characteristics (18/16-Bit Bus).......................................................146

80-System Bus Interface Timing Characteristics (8/9-Bit Bus) ..........................................................147

Serial Peripheral Interface Timing Characteristics .............................................................................147

RGB Interface Timing Characteristics.................................................................................................148

Reset Timing Characteristics...............................................................................................................148

LCD Driver Output Characteristics .....................................................................................................148

Notes to Electrical Characteristics.......................................................................................................149

Timing characteristic diagram .............................................................................................................150

3

�

LGDP4531

Rev 1.15

Description

The LGDP4531 is a one-chip liquid crystal controller driver LSI, comprising RAM of 240 RGB x 320

dots at maximum, a source driver, a gate driver and a power supply circuit. For effective data transfer, the

LGDP4531 supports high-speed 8-/9-/16-/18-bit bus interfaces as a system interface to microcomputer

and high-speed RAM write mode.

As a moving picture interface, the LGDP4531 supports RGB interface (VSYNC, HSYNC, DOTCLK,

ENABLE, DB17-0).

Also, the LGDP4531 incorporates step-up circuits and voltage follower circuits to generate TFT liquid

crystal panel drive voltages.

The LGDP4531’s power management functions such as 8-color display and deep standby and so on make

this LSI an ideal driver for the medium or small sized portable products with color display systems such

as digital cellular phones or small PDAs, where long battery life is a major concern.

4

�

LGDP4531

Rev 1.15

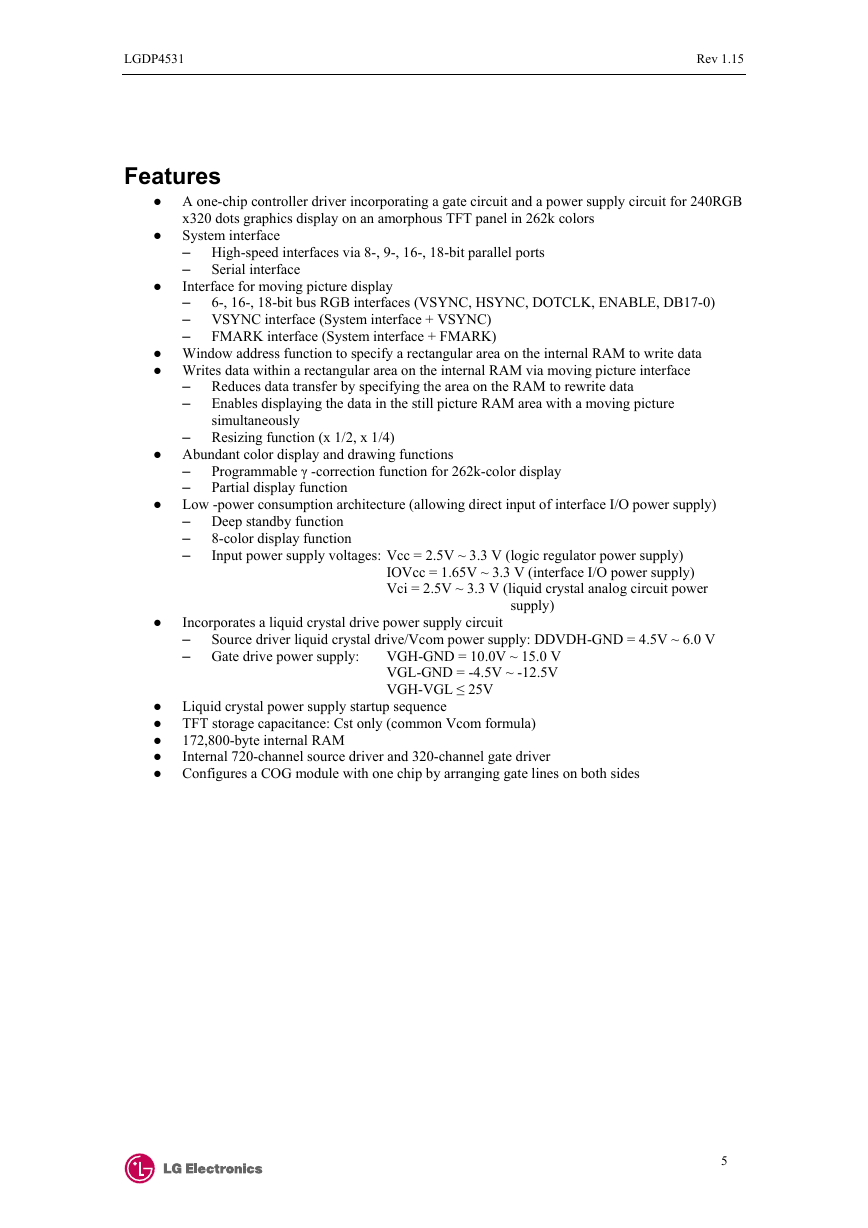

Features

● A one-chip controller driver incorporating a gate circuit and a power supply circuit for 240RGB

●

●

Serial interface

x320 dots graphics display on an amorphous TFT panel in 262k colors

System interface

– High-speed interfaces via 8-, 9-, 16-, 18-bit parallel ports

–

Interface for moving picture display

–

– VSYNC interface (System interface + VSYNC)

–

FMARK interface (System interface + FMARK)

6-, 16-, 18-bit bus RGB interfaces (VSYNC, HSYNC, DOTCLK, ENABLE, DB17-0)

● Window address function to specify a rectangular area on the internal RAM to write data

● Writes data within a rectangular area on the internal RAM via moving picture interface

– Reduces data transfer by specifying the area on the RAM to rewrite data

– Enables displaying the data in the still picture RAM area with a moving picture

simultaneously

– Resizing function (x 1/2, x 1/4)

● Abundant color display and drawing functions

–

–

Programmable γ -correction function for 262k-color display

Partial display function

● Low -power consumption architecture (allowing direct input of interface I/O power supply)

– Deep standby function

–

8-color display function

–

Input power supply voltages: Vcc = 2.5V ~ 3.3 V (logic regulator power supply)

IOVcc = 1.65V ~ 3.3 V (interface I/O power supply)

Vci = 2.5V ~ 3.3 V (liquid crystal analog circuit power

supply)

Source driver liquid crystal drive/Vcom power supply: DDVDH-GND = 4.5V ~ 6.0 V

●

Incorporates a liquid crystal drive power supply circuit

–

– Gate drive power supply: VGH-GND = 10.0V ~ 15.0 V

VGL-GND = -4.5V ~ -12.5V

VGH-VGL ≤ 25V

● Liquid crystal power supply startup sequence

● TFT storage capacitance: Cst only (common Vcom formula)

●

●

● Configures a COG module with one chip by arranging gate lines on both sides

172,800-byte internal RAM

Internal 720-channel source driver and 320-channel gate driver

5

�

LGDP4531

Rev 1.15

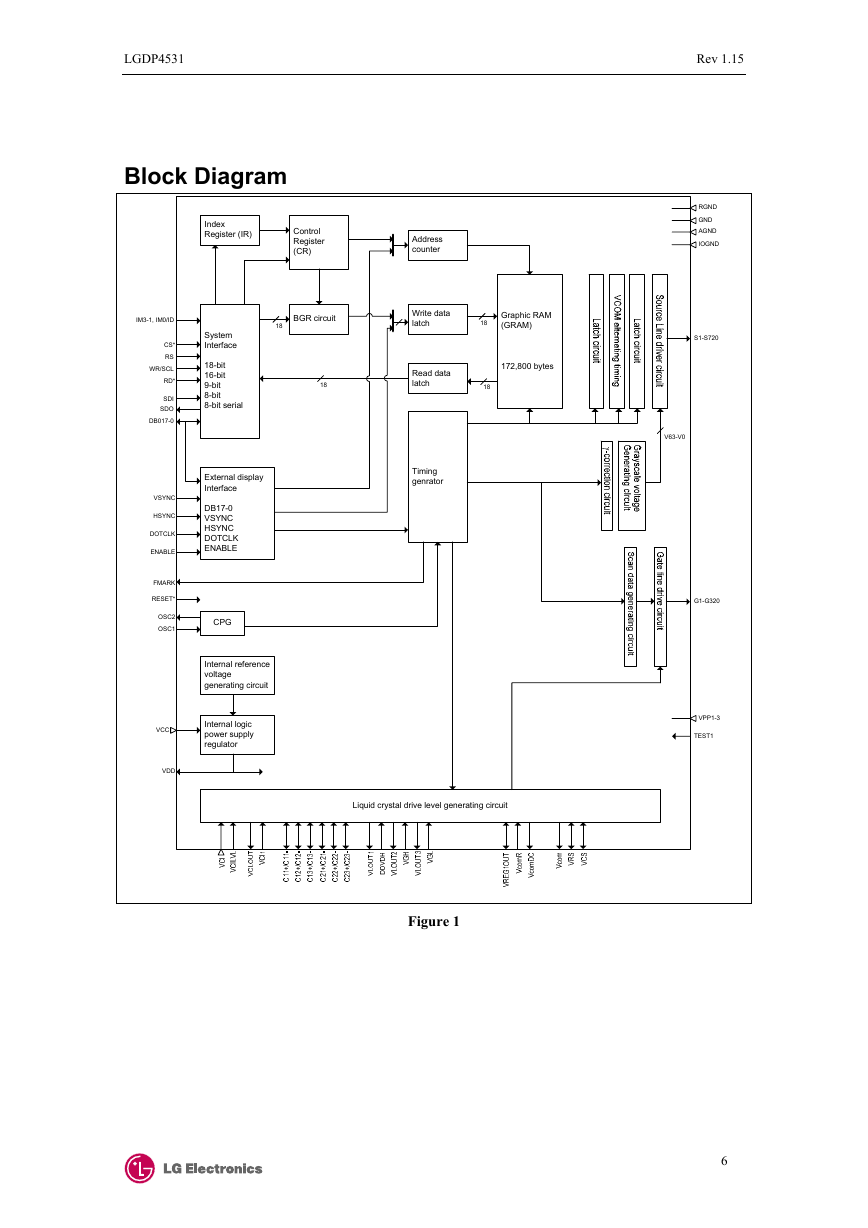

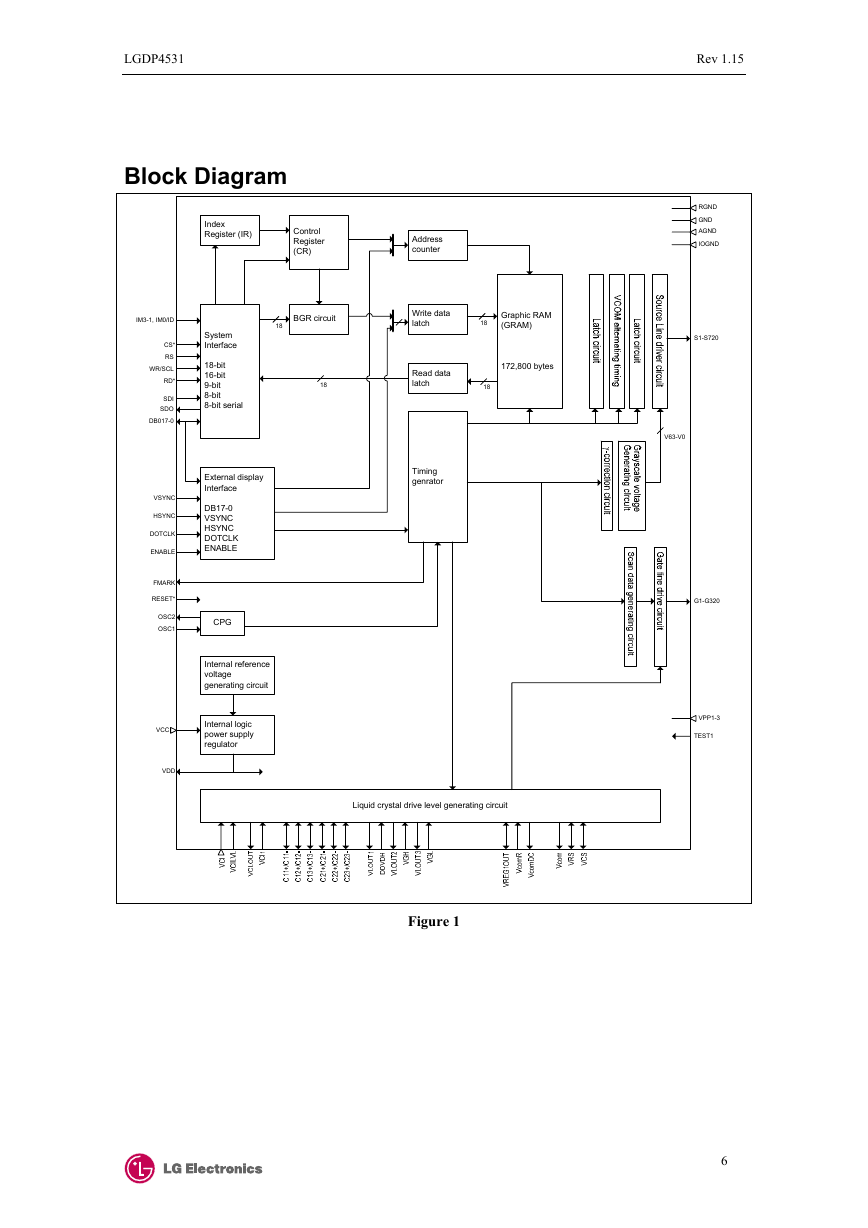

Block Diagram

Index

Register (IR)

Control

Register

(CR)

Address

counter

BGR circuit

18

Write data

latch

18

Graphic RAM

(GRAM)

18

Read data

latch

18

172,800 bytes

Timing

genrator

V63-V0

IM3-1, IM0/ID

CS*

RS

WR/SCL

RD*

SDI

SDO

DB017-0

System

Interface

18-bit

16-bit

9-bit

8-bit

8-bit serial

External display

Interface

DB17-0

VSYNC

HSYNC

DOTCLK

ENABLE

CPG

Internal reference

voltage

generating circuit

Internal logic

power supply

regulator

VSYNC

HSYNC

DOTCLK

ENABLE

FMARK

RESET*

OSC2

OSC1

VCC

VDD

Liquid crystal drive level generating circuit

Figure 1

RGND

GND

AGND

IOGND

S1-S720

G1-G320

VPP1-3

TEST1

6

�

LGDP4531

Rev 1.15

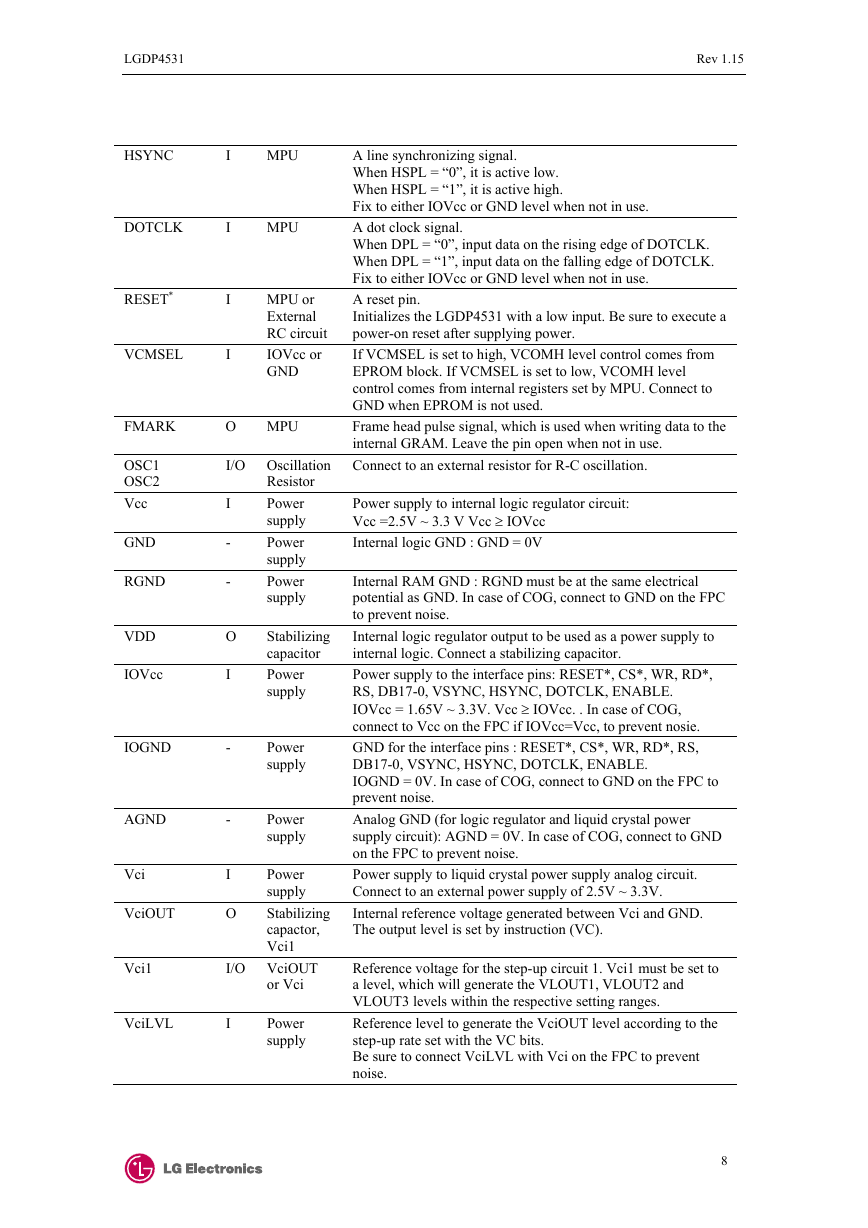

Pin Function

Table 1

Signal

IM3-1,

IM0/ID

CS*

RS

WR*/SCL

RD*

SDI

I

I

I

I

I

I

I/O Connected

to

GND/

IOVcc

MPU

MPU

MPU

MPU

MPU

SDO

O

MPU

DB0 ~ DB17

I/O MPU

ENABLE

VSYNC

I

I

MPU

MPU

Function

Select a mode to interface to an MPU. In SPI mode, the IM0

pin is used to set the ID of device code.

IM[3:0]

000*

0010

Interface Mode

Setting disabled

80-system 16-bit interface

0011

010*

011*

100*

1010

1011

11**

80-system 8-bit interface

Serial peripheral interface (SPI)

Setting disabled

Setting disabled

80-system 18-bit interface

80-system 9-bit interface

Setting disabled

DB Pins

-

DB[17:10],

DB[8:1]

DB[17:10]

SDI, SDO

-

-

DB[17:0]

DB[17:9]

-

A chip select signal. Amplitude: IOVCC-GND.

Low: LGDP4531 is selected and accessible.

High: LGDP4531 is not selected and not accessible.

Fix to the GND level when not in use.

A register select signal. Amplitude: IOVCC-GND.

Low: select the index/status register.

High: select a control register.

In SPI mode, fix to either IOVcc or GND level.

Outputs a write strobe signal in 80-system bus interface mode

and enables an operation to write data when the signal is low.

In SPI mode, a synchronizing clock signal is output.

Outputs a read strobe signal in 80-system bus interface mode

and enables an operation to read data when the signal is low. In

SPI mode, fix to either IOVcc or GND level.

A serial data input (SDI) pin in SPI mode. Data are input on the

rising edge of the SCL signal. Fix to either IOVcc or GND

level when not in use.

A serial data output (SDO) pin in SPI mode. Data are output on

the falling edge of the SCL signal. Leave the pin open when not

in use.

An 18-bit parallel bidirectional data bus. Unused pins must be

fixed either IOVcc or GND level.

A data enable signal in RGB interface mode.

Low: Select (accessible)

High: Not select (inaccessible)

The EPL bit inverts the polarity of the ENABLE signal. Fix to

either IOVcc or GND level when not in use.

A frame synchronizing signal.

When VSPL = “0”, it is active low.

When VSPL = “1”, it is active high.

Fix to either IOVcc or GND level when not in use.

7

�

LGDP4531

Rev 1.15

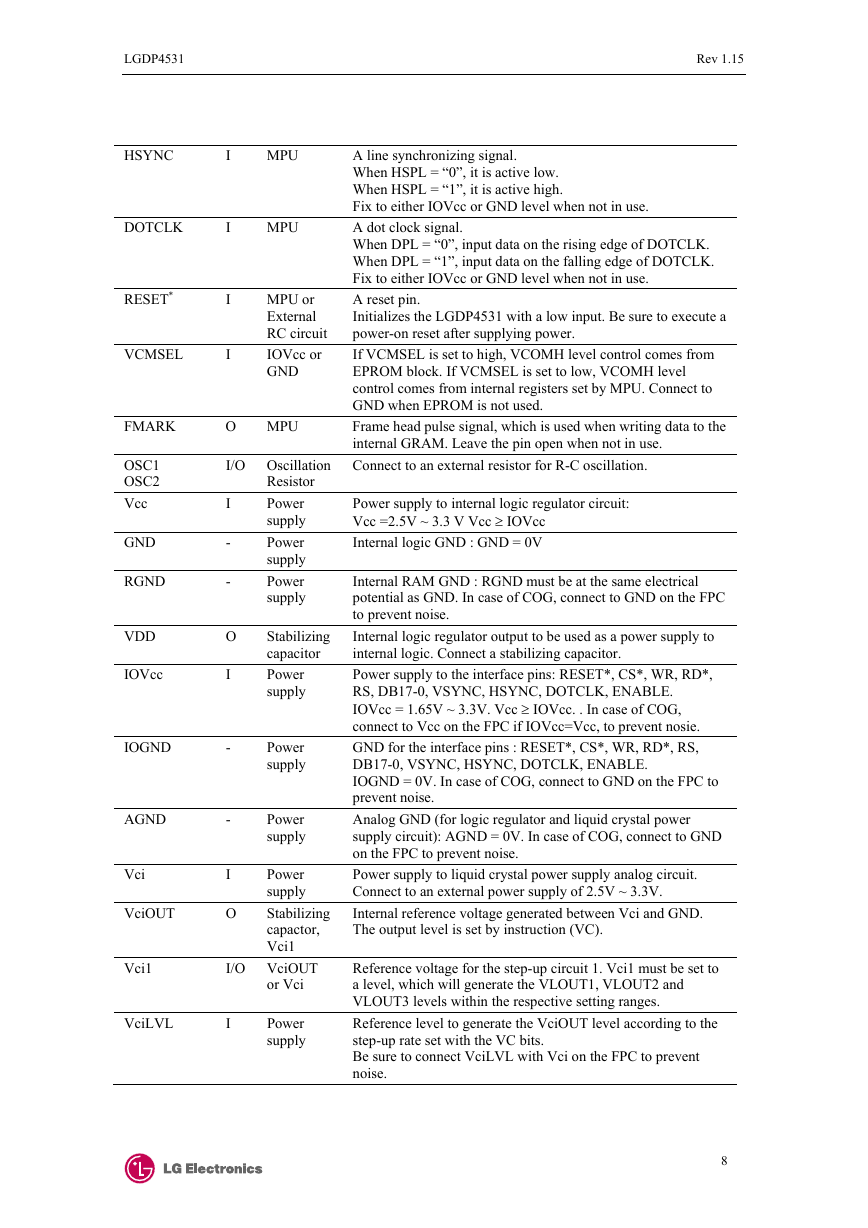

HSYNC

DOTCLK

RESET*

VCMSEL

I

I

I

I

MPU

MPU

MPU or

External

RC circuit

IOVcc or

GND

FMARK

O

MPU

I/O Oscillation

OSC1

OSC2

Vcc

GND

RGND

VDD

IOVcc

IOGND

AGND

Vci

I

-

-

O

I

-

-

I

Resistor

Power

supply

Power

supply

Power

supply

Stabilizing

capacitor

Power

supply

Power

supply

Power

supply

Power

supply

Stabilizing

capactor,

Vci1

VciOUT

O

Vci1

I/O VciOUT

or Vci

VciLVL

I

Power

supply

A line synchronizing signal.

When HSPL = “0”, it is active low.

When HSPL = “1”, it is active high.

Fix to either IOVcc or GND level when not in use.

A dot clock signal.

When DPL = “0”, input data on the rising edge of DOTCLK.

When DPL = “1”, input data on the falling edge of DOTCLK.

Fix to either IOVcc or GND level when not in use.

A reset pin.

Initializes the LGDP4531 with a low input. Be sure to execute a

power-on reset after supplying power.

If VCMSEL is set to high, VCOMH level control comes from

EPROM block. If VCMSEL is set to low, VCOMH level

control comes from internal registers set by MPU. Connect to

GND when EPROM is not used.

Frame head pulse signal, which is used when writing data to the

internal GRAM. Leave the pin open when not in use.

Connect to an external resistor for R-C oscillation.

Power supply to internal logic regulator circuit:

Vcc =2.5V ~ 3.3 V Vcc ≥ IOVcc

Internal logic GND : GND = 0V

Internal RAM GND : RGND must be at the same electrical

potential as GND. In case of COG, connect to GND on the FPC

to prevent noise.

Internal logic regulator output to be used as a power supply to

internal logic. Connect a stabilizing capacitor.

Power supply to the interface pins: RESET*, CS*, WR, RD*,

RS, DB17-0, VSYNC, HSYNC, DOTCLK, ENABLE.

IOVcc = 1.65V ~ 3.3V. Vcc ≥ IOVcc. . In case of COG,

connect to Vcc on the FPC if IOVcc=Vcc, to prevent nosie.

GND for the interface pins : RESET*, CS*, WR, RD*, RS,

DB17-0, VSYNC, HSYNC, DOTCLK, ENABLE.

IOGND = 0V. In case of COG, connect to GND on the FPC to

prevent noise.

Analog GND (for logic regulator and liquid crystal power

supply circuit): AGND = 0V. In case of COG, connect to GND

on the FPC to prevent noise.

Power supply to liquid crystal power supply analog circuit.

Connect to an external power supply of 2.5V ~ 3.3V.

Internal reference voltage generated between Vci and GND.

The output level is set by instruction (VC).

Reference voltage for the step-up circuit 1. Vci1 must be set to

a level, which will generate the VLOUT1, VLOUT2 and

VLOUT3 levels within the respective setting ranges.

Reference level to generate the VciOUT level according to the

step-up rate set with the VC bits.

Be sure to connect VciLVL with Vci on the FPC to prevent

noise.

8

�