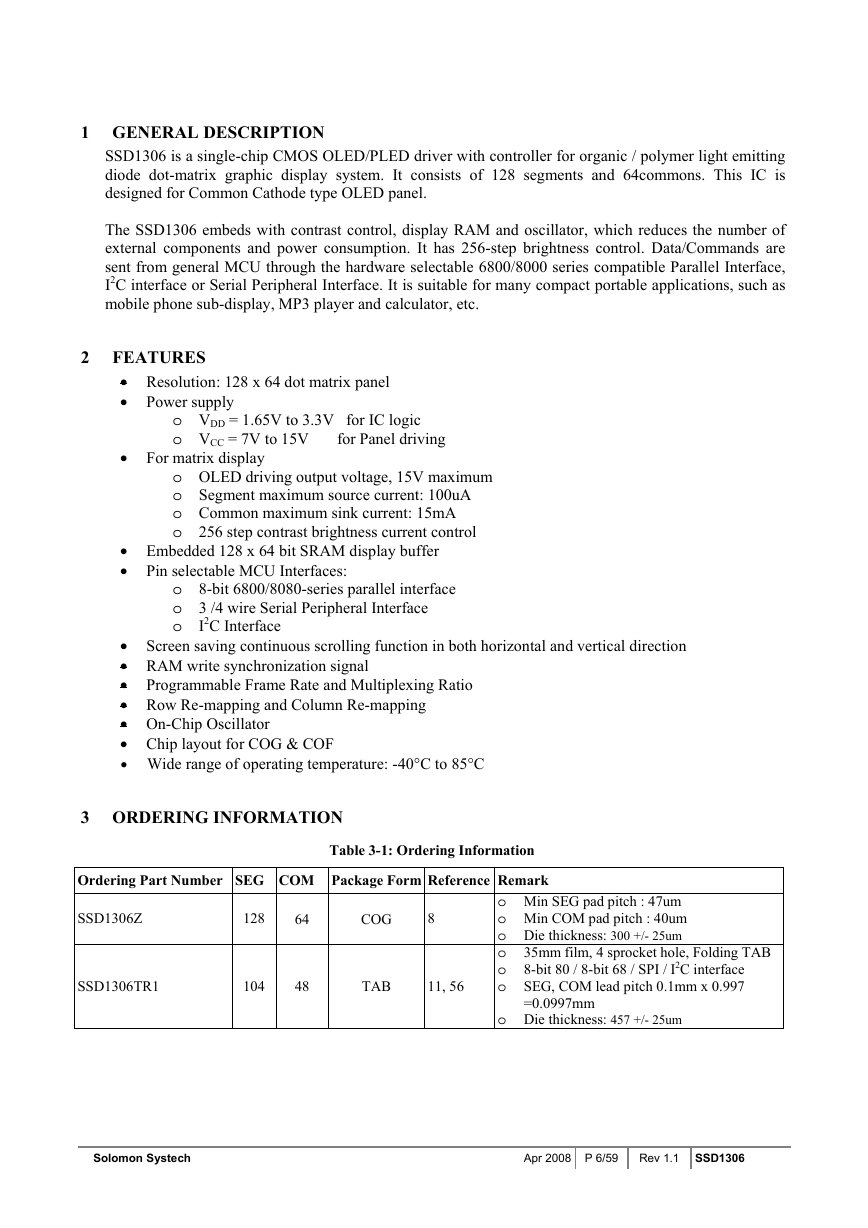

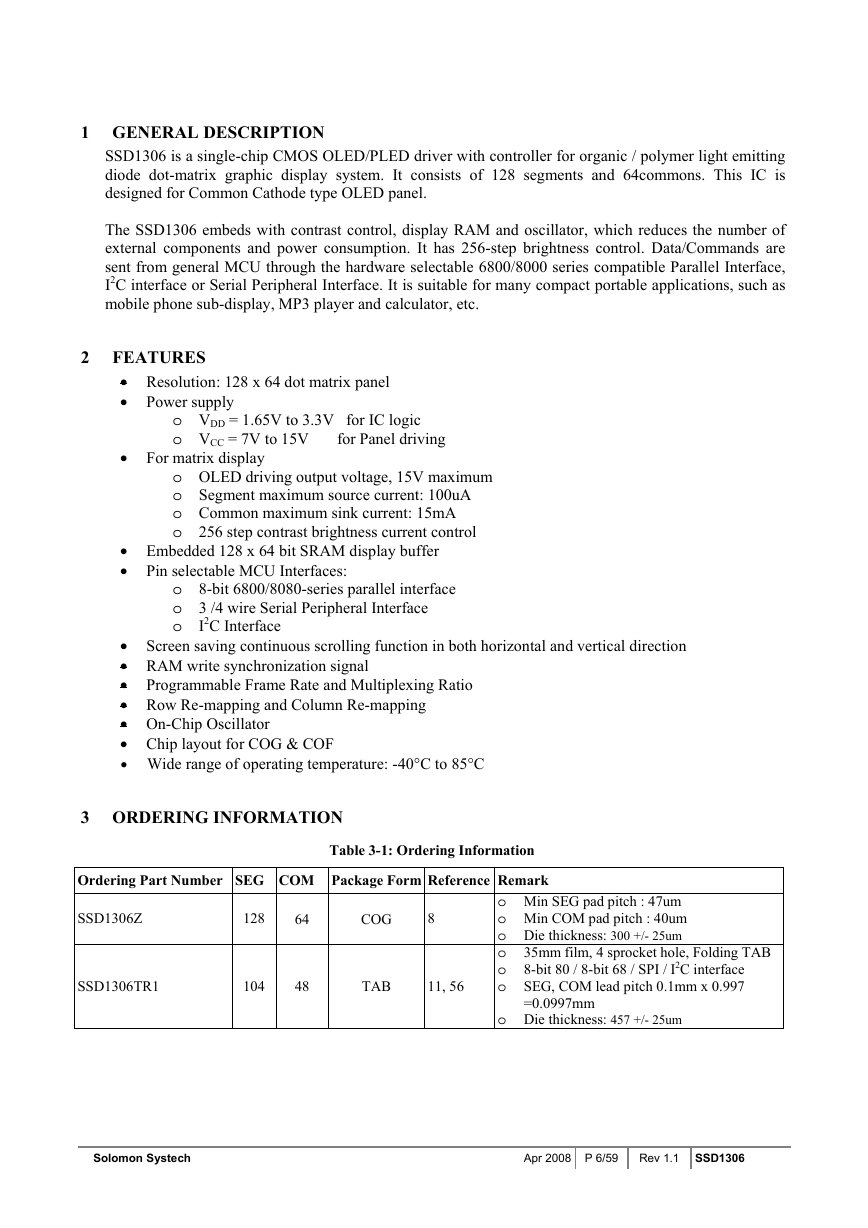

1 GENERAL DESCRIPTION

2 FEATURES

3 ORDERING INFORMATION

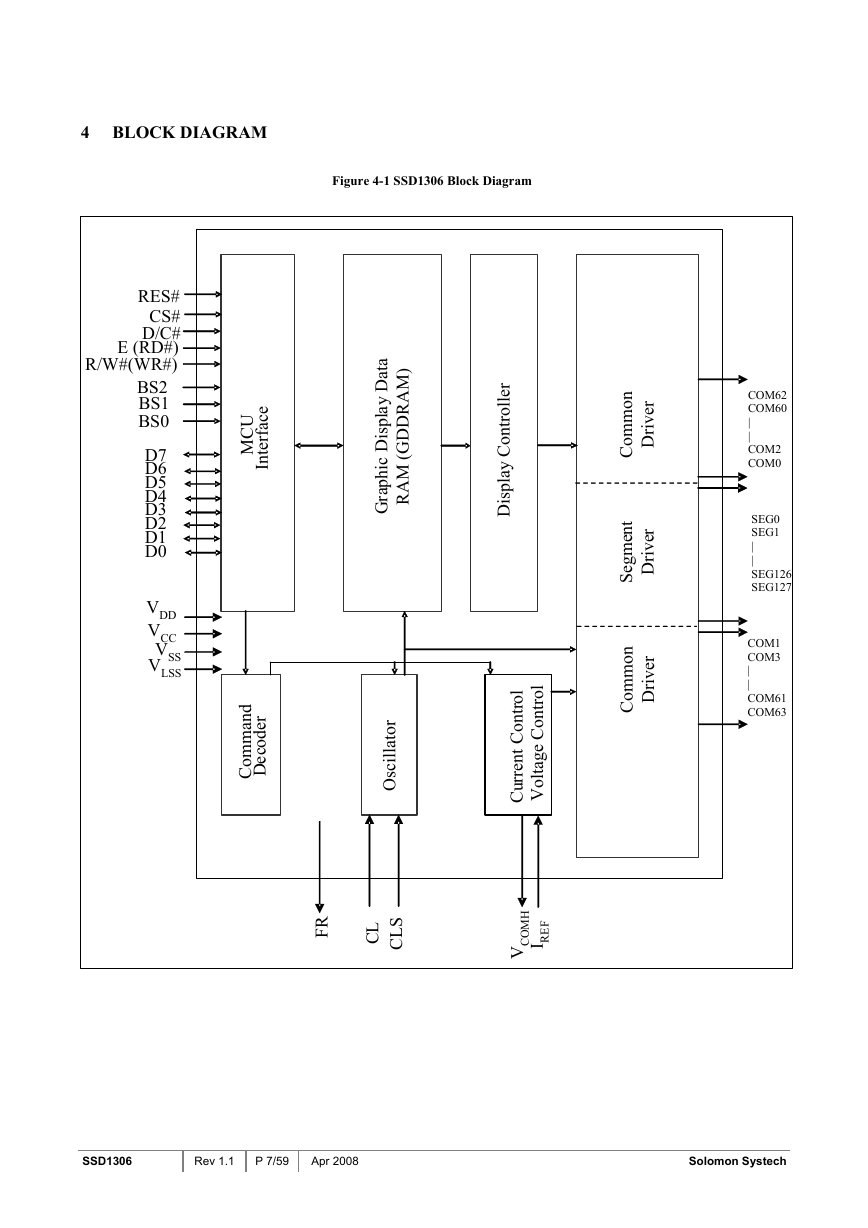

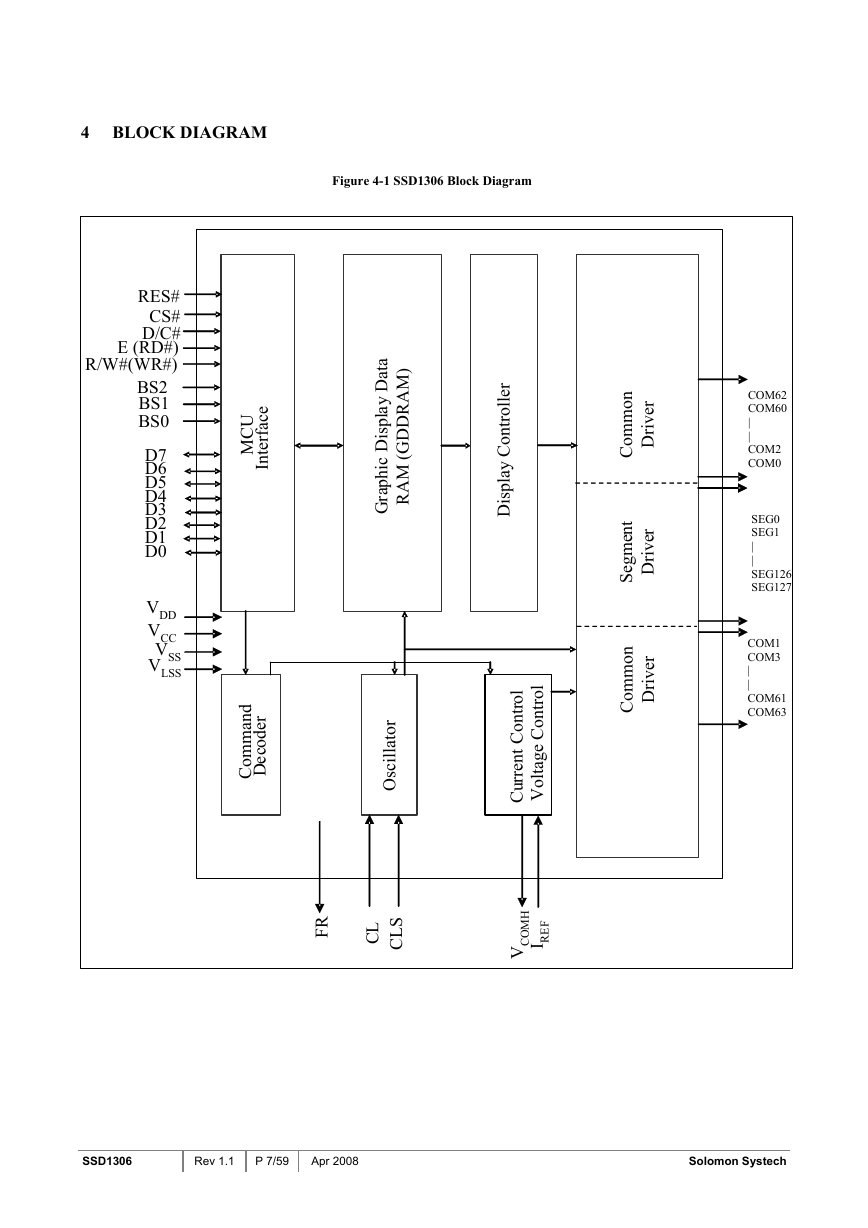

4 BLOCK DIAGRAM

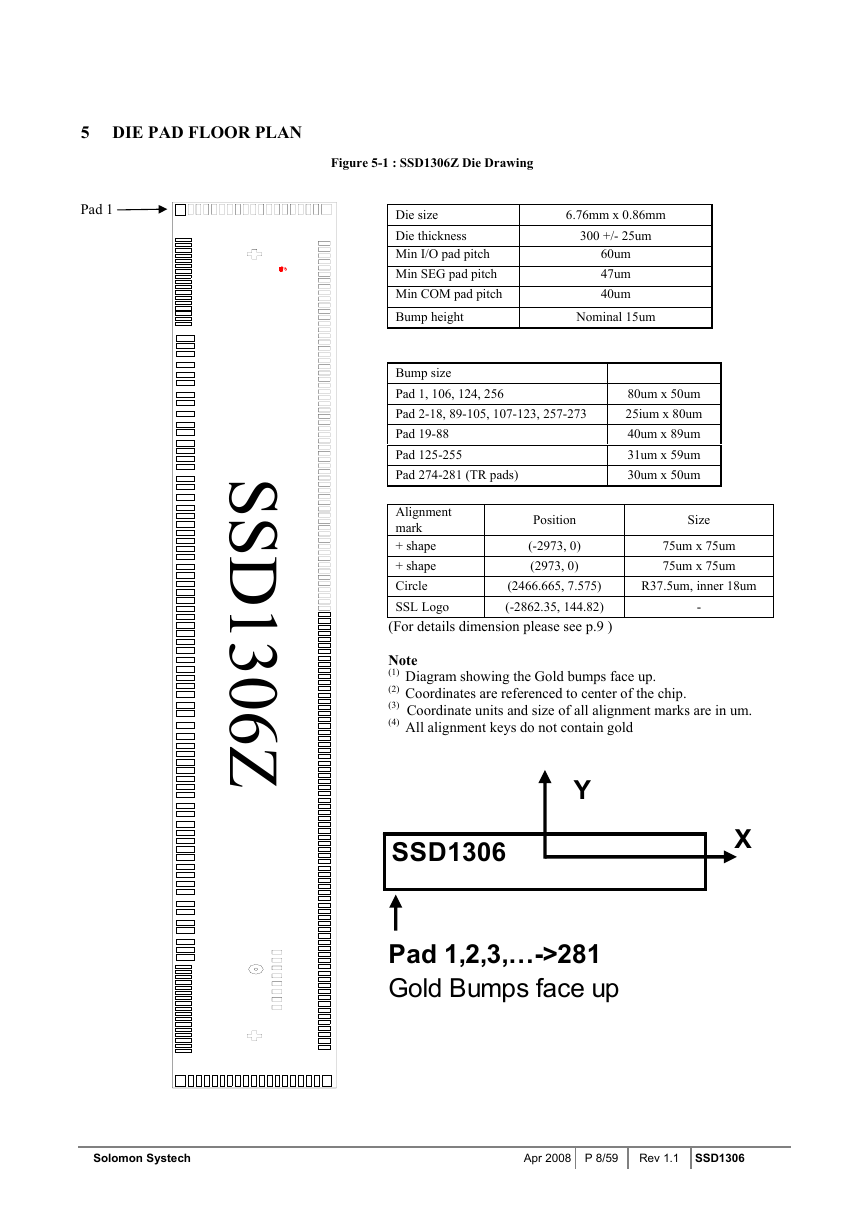

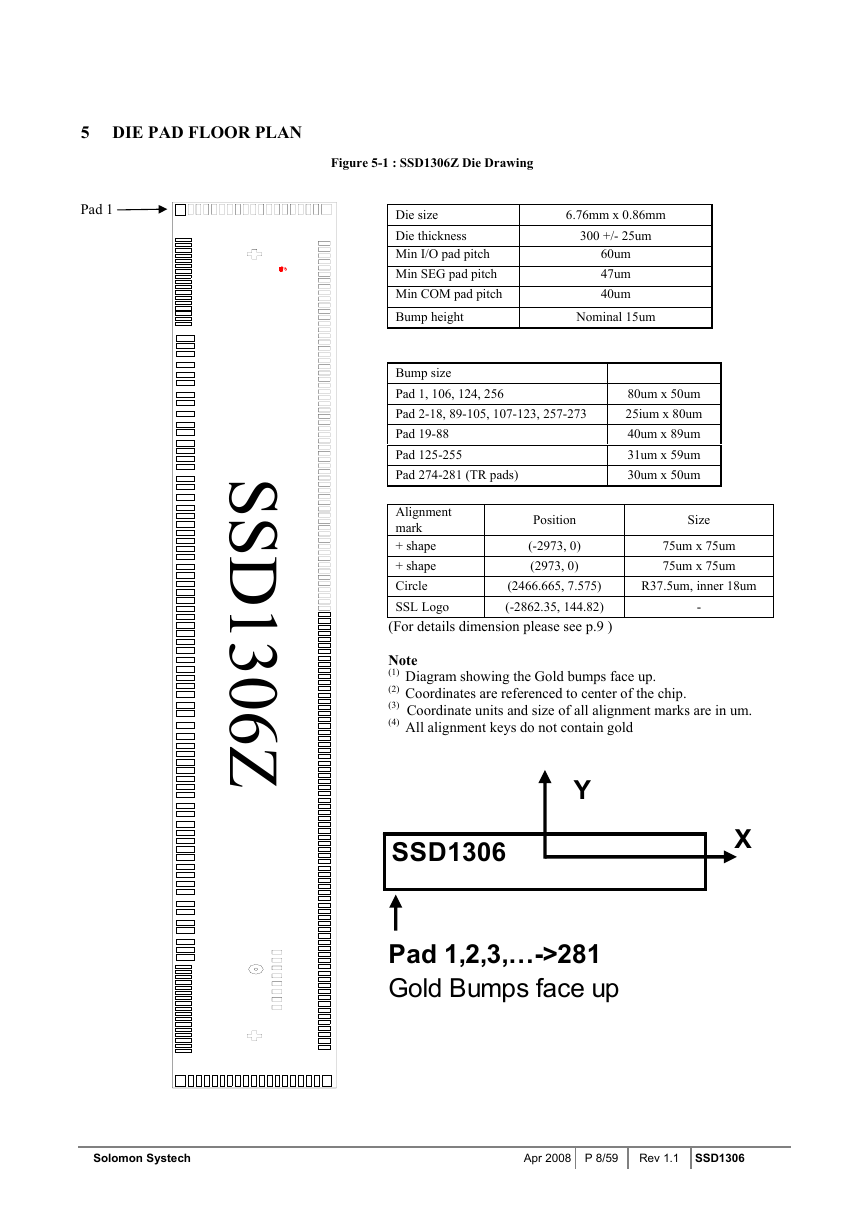

5 DIE PAD FLOOR PLAN

6 PIN ARRANGEMENT

6.1 SSD1306TR1 pin assignment

7 PIN DESCRIPTION

8 FUNCTIONAL BLOCK DESCRIPTIONS

8.1 MCU Interface selection

8.1.1 MCU Parallel 6800-series Interface

8.1.2 MCU Parallel 8080-series Interface

8.1.3 MCU Serial Interface (4-wire SPI)

8.1.4 MCU Serial Interface (3-wire SPI)

8.1.5 MCU I2C Interface

8.1.5.1 I2C-bus Write data

8.1.5.2 Write mode for I2C

8.2 Command Decoder

8.3 Oscillator Circuit and Display Time Generator

8.4 FR synchronization

8.5 Reset Circuit

8.6 Segment Drivers / Common Drivers

8.7 Graphic Display Data RAM (GDDRAM)

8.8 SEG/COM Driving block

8.9 Power ON and OFF sequence

9 COMMAND TABLE

9.1 Data Read / Write

10 COMMAND DESCRIPTIONS

10.1 Fundamental Command

10.1.1 Set Lower Column Start Address for Page Addressing Mode (00h~0Fh)

10.1.2 Set Higher Column Start Address for Page Addressing Mode (10h~1Fh)

10.1.3 Set Memory Addressing Mode (20h)

10.1.4 Set Column Address (21h)

10.1.5 Set Page Address (22h)

10.1.6 Set Display Start Line (40h~7Fh)

10.1.7 Set Contrast Control for BANK0 (81h)

10.1.8 Set Segment Re-map (A0h/A1h)

10.1.9 Entire Display ON (A4h/A5h)

10.1.10 Set Normal/Inverse Display (A6h/A7h)

10.1.11 Set Multiplex Ratio (A8h)

10.1.12 Set Display ON/OFF (AEh/AFh)

10.1.13 Set Page Start Address for Page Addressing Mode (B0h~B7h)

10.1.14 Set COM Output Scan Direction (C0h/C8h)

10.1.15 Set Display Offset (D3h)

10.1.16 Set Display Clock Divide Ratio/ Oscillator Frequency (D5h)

10.1.17 Set Pre-charge Period (D9h)

10.1.18 Set COM Pins Hardware Configuration (DAh)

10.1.19 Set VCOMH Deselect Level (DBh)

10.1.20 NOP (E3h)

10.1.21 Status register Read

10.2 Graphic Acceleration Command

10.2.1 Horizontal Scroll Setup (26h/27h)

10.2.2 Continuous Vertical and Horizontal Scroll Setup (29h/2Ah)

10.2.3 Deactivate Scroll (2Eh)

10.2.4 Activate Scroll (2Fh)

10.2.5 Set Vertical Scroll Area(A3h)

11 MAXIMUM RATINGS

12 DC CHARACTERISTICS

13 AC CHARACTERISTICS

14 Application Example

15 PACKAGE INFORMATION

15.1 SSD1306TR1 Detail Dimension

15.2 SSD1306Z Die Tray Information