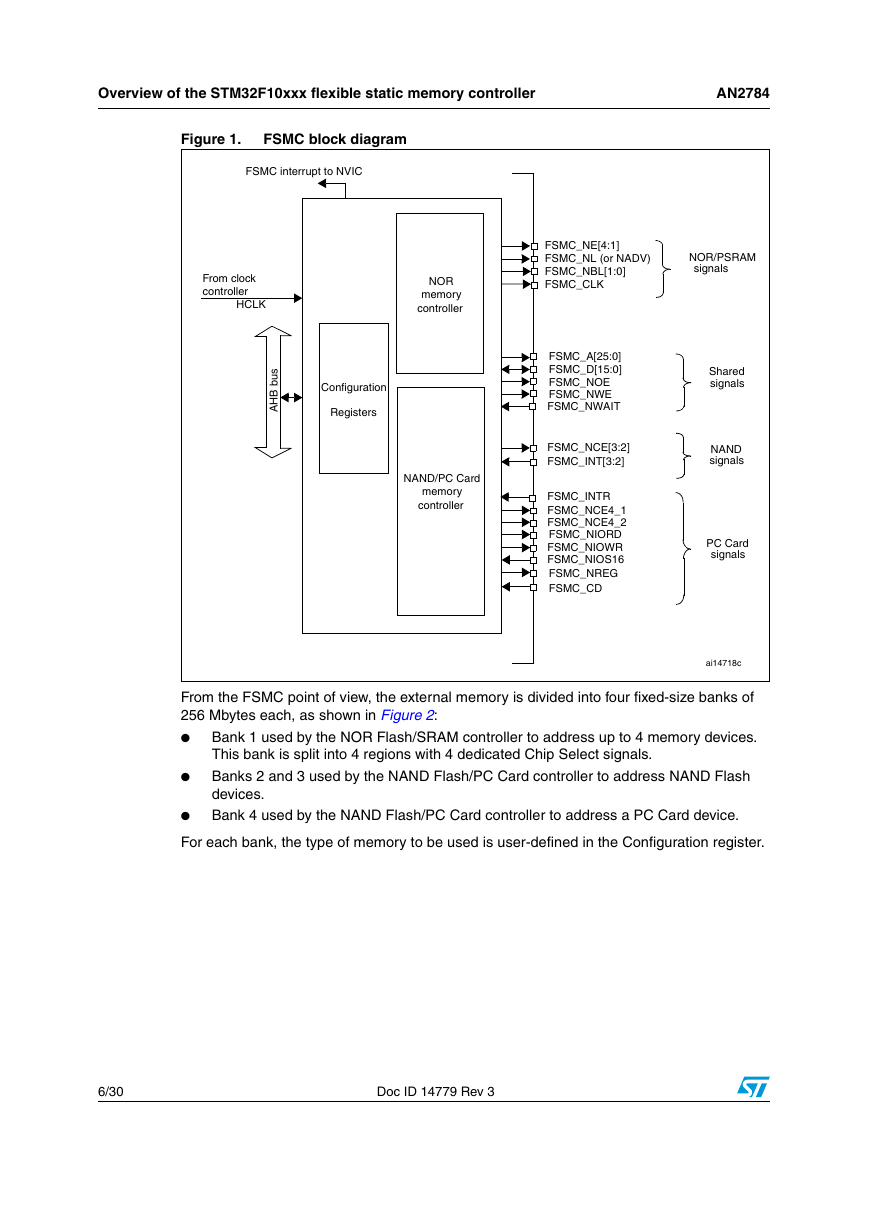

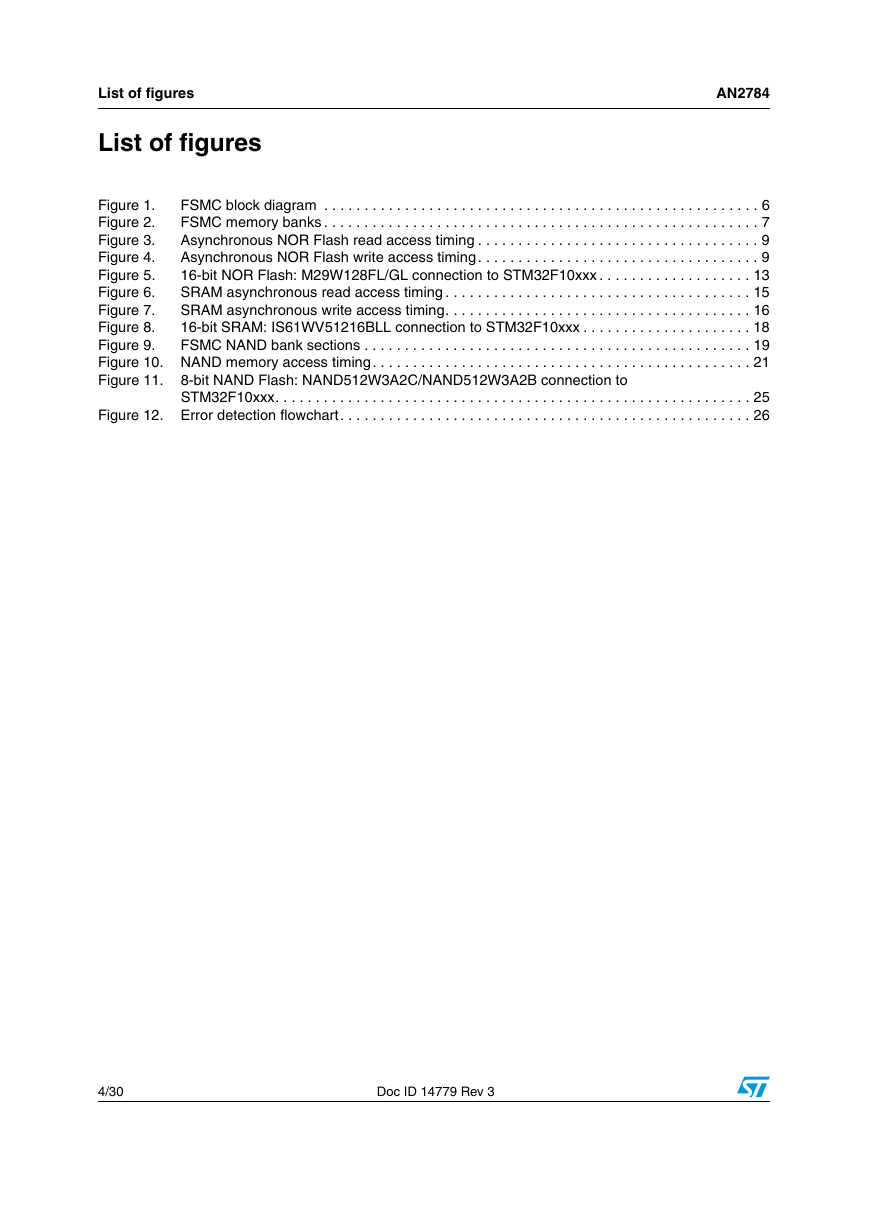

1 Overview of the STM32F10xxx flexible static memory controller

Figure 1. FSMC block diagram

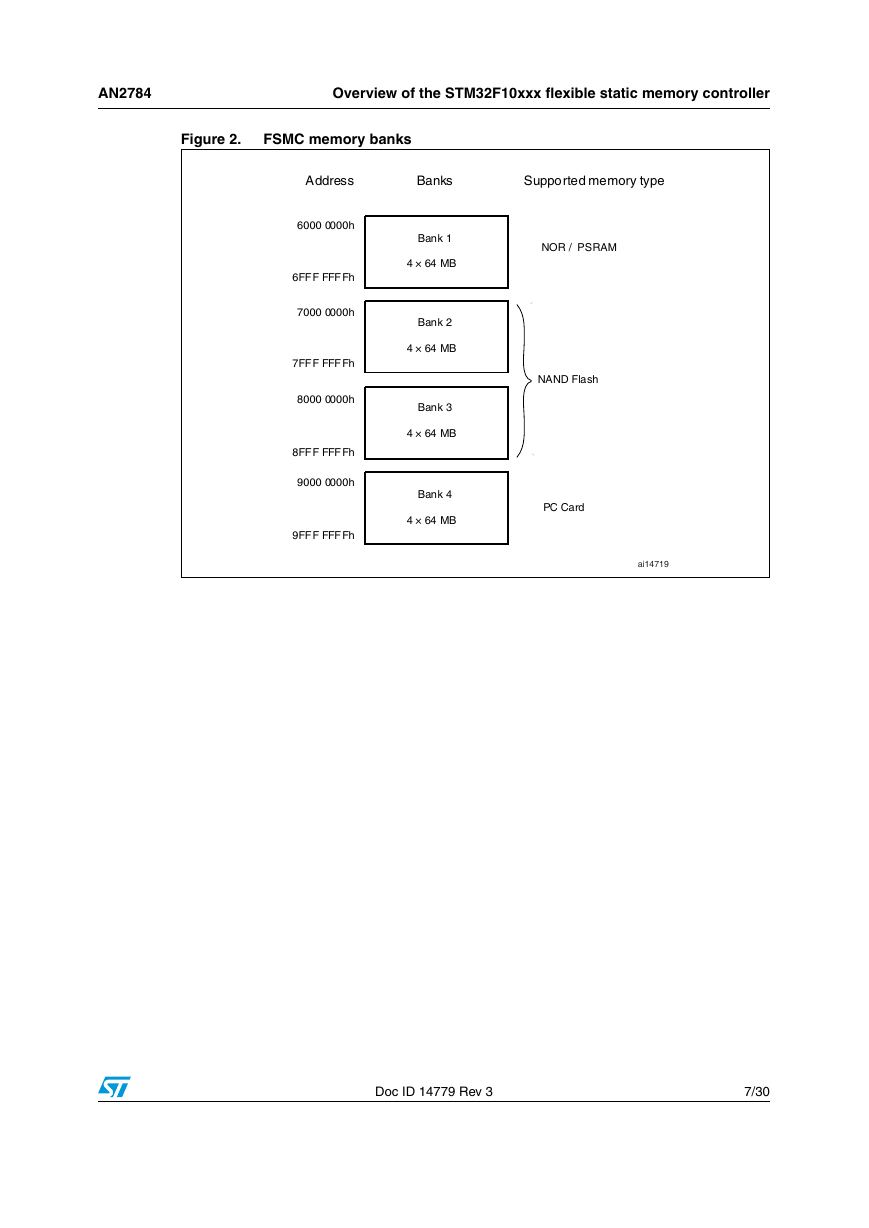

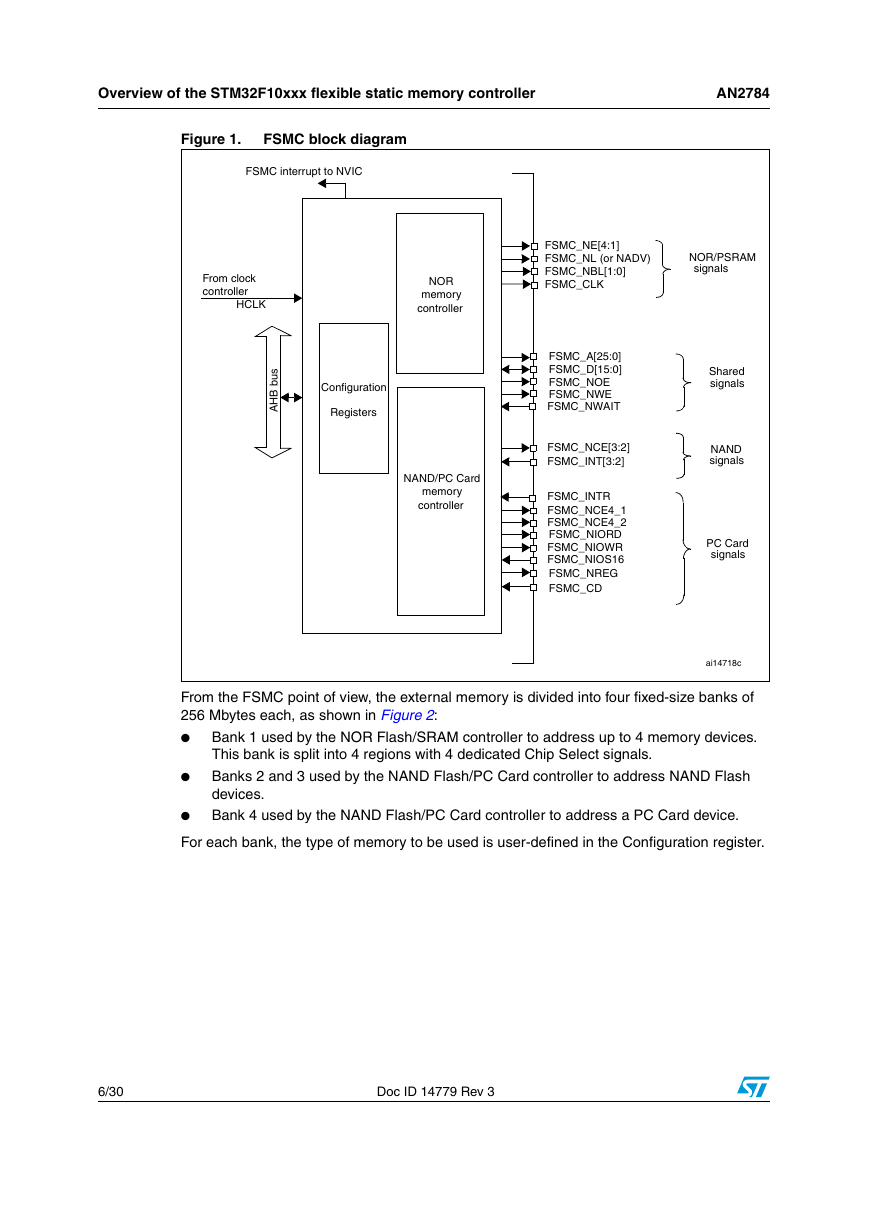

Figure 2. FSMC memory banks

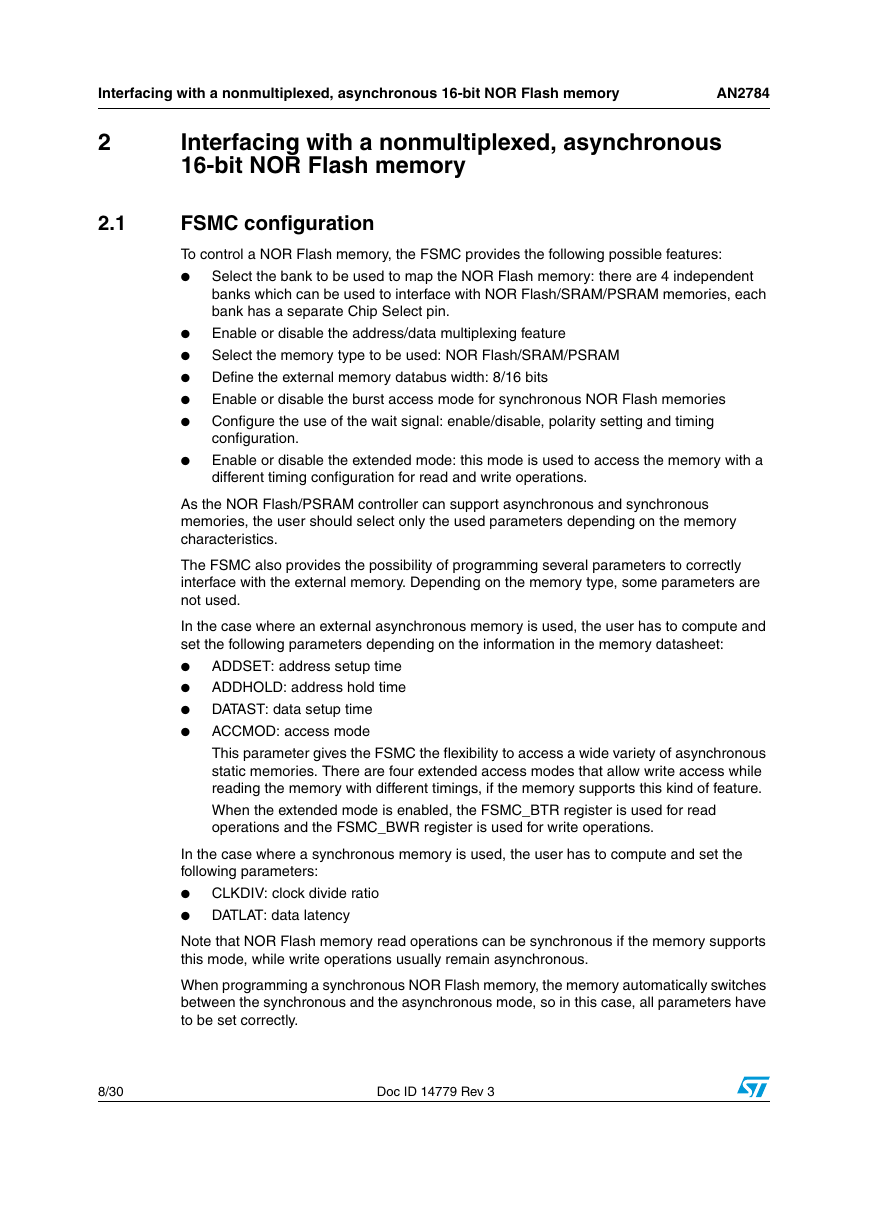

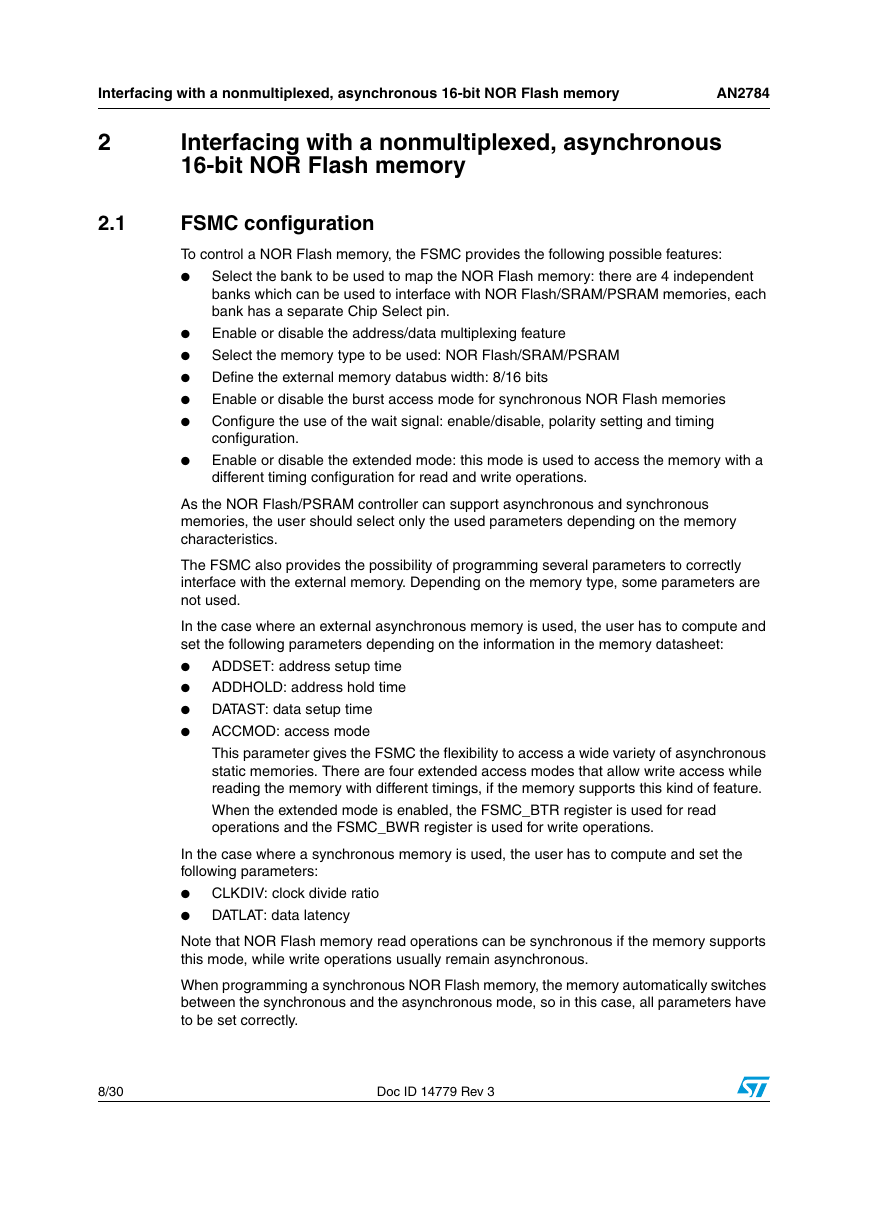

2 Interfacing with a nonmultiplexed, asynchronous 16-bit NOR Flash memory

2.1 FSMC configuration

Figure 3. Asynchronous NOR Flash read access timing

Figure 4. Asynchronous NOR Flash write access timing

2.1.1 Typical use of the FSMC to interface with a NOR Flash memory

2.2 Timing computation

Table 1. NOR Flash memory timings

Table 2. STM32F10xxx parameters

2.3 Hardware connection

Table 3. M29W128FL signal to FSMC pin correspondence

Figure 5. 16-bit NOR Flash: M29W128FL/GL connection to STM32F10xxx

2.4 Code execution from an external NOR Flash memory

3 Interfacing with a nonmultiplexed, asynchronous 16- bit SRAM

3.1 FSMC configuration

Figure 6. SRAM asynchronous read access timing

Figure 7. SRAM asynchronous write access timing

3.1.1 Typical use of the FSMC to interface with an SRAM

3.2 Timing computation

Table 4. SRAM timings

3.3 Hardware connection

Table 5. IS61WV51216BLL signal to FSMC pin correspondence

Figure 8. 16-bit SRAM: IS61WV51216BLL connection to STM32F10xxx

3.4 Using the external SRAM as a data memory

4 Interfacing with an 8-bit NAND Flash memory

Figure 9. FSMC NAND bank sections

4.1 FSMC configuration

Figure 10. NAND memory access timing

4.1.1 Typical use of the FSMC to interface with a NAND memory

4.2 Timing computation

Table 6. NAND Flash memory timings

4.3 Hardware connection

Table 7. NAND512W3A signal to FSMC pin correspondence

Figure 11. 8-bit NAND Flash: NAND512W3A2C/NAND512W3A2B connection to STM32F10xxx

4.4 Error correction code computation

4.4.1 Error correction code (ECC) computation overview

4.4.2 Error detection

Figure 12. Error detection flowchart

5 STM32F10xxx FSMC configuration in 100-pin packages

5.1 Interfacing the FSMC with a NAND Flash memory

Table 8. NAND Flash memory connection to the FSMC

5.2 Interfacing the FSMC with a NOR Flash memory

Table 9. NOR Flash memory connection to the FSMC

6 Revision history

Table 10. Document revision history