Abbreviations

References

Register conventions

Features (continued from front page)

High-Performance and Low-Power 8051-Compatible Microcontroll

Up to 128 KB Non-volatile Program Memory and 2 x 4 KB Data M

Hardware AES Encryption/Decryption

Peripheral Features

Low Power

802.15.4 MAC hardware support

Integrated 2.4GHz DSSS Digital Radio

Absolute Maximum Ratings

Operating Conditions

Electrical Specifications

General Characteristics

RF Receive Section

RF Transmit Section

32 MHz Crystal Oscillator

32.768 kHz Crystal Oscillator

Low Power RC Oscillator

High Speed RC Oscillator

Frequency Synthesizer Characteristics

Analog Temperature Sensor

8-14 bit ADC

Control AC Characteristics

SPI AC Characteristics

Debug Interface AC Characteristics

Port Outputs AC Characteristics

Timer Inputs AC Characteristics

DC Characteristics

Pin and I/O Port Configuration

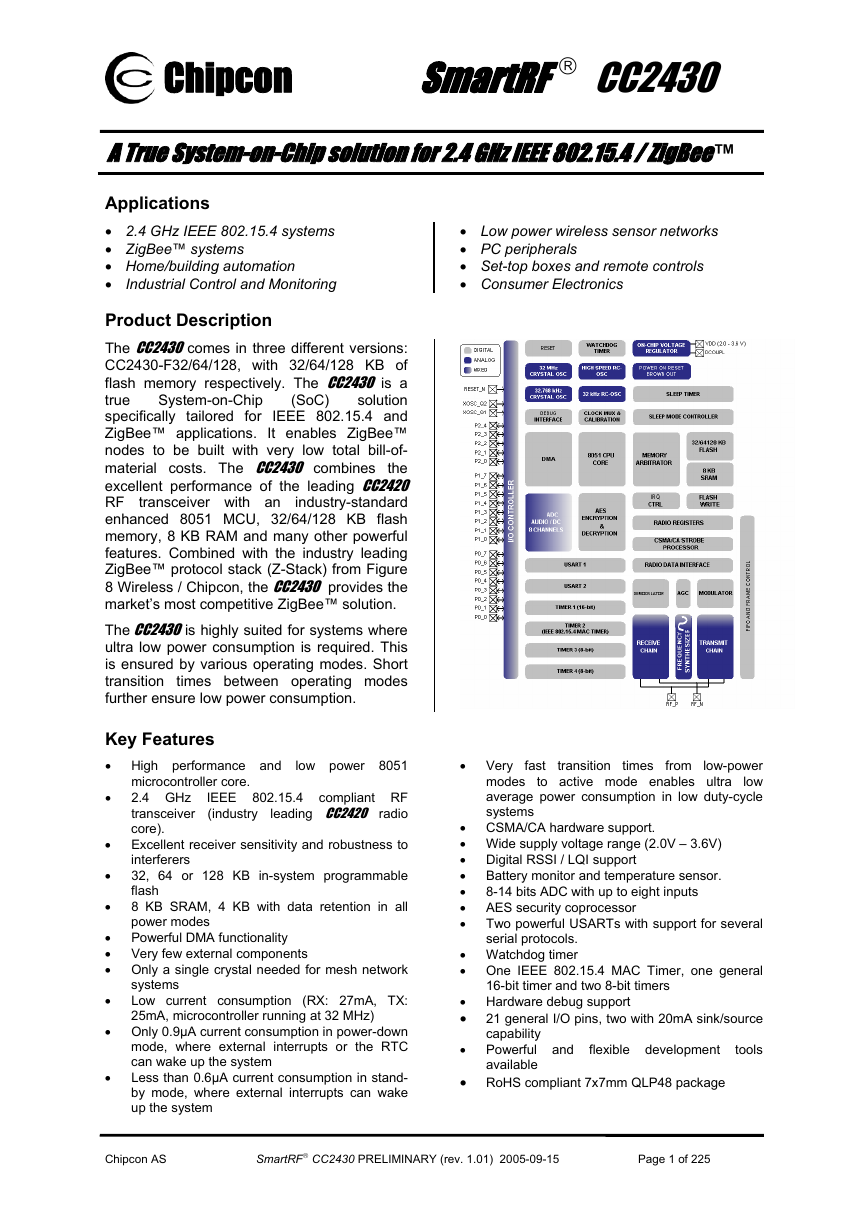

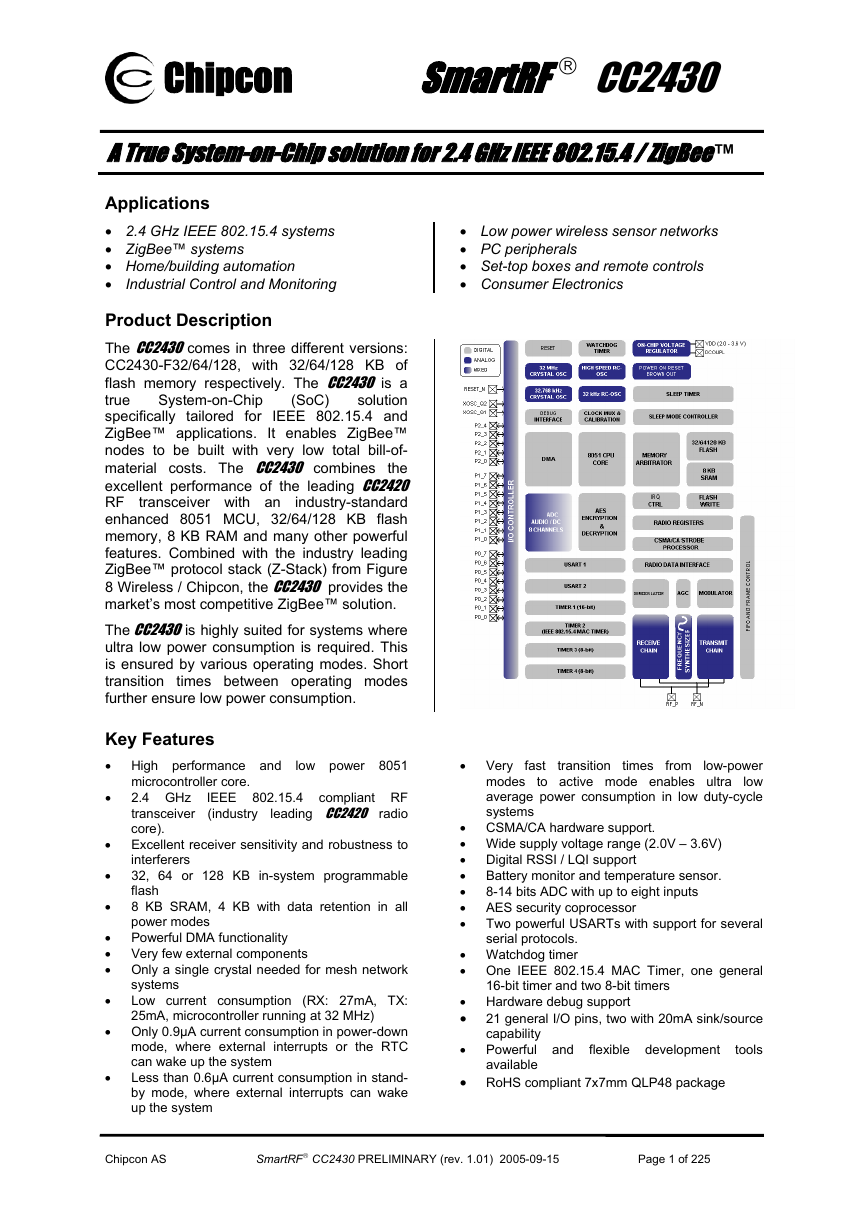

Circuit Description

CPU and Peripherals

Radio

Power Management

Application Circuit

Input / output matching

Bias resistors

Crystal

Voltage regulators

Power supply decoupling and filtering

8051 CPU

8051 CPU Introduction

Reset

Memory

Memory Map

Memory Space

Data Pointers

XDATA Memory Access

SFR Registers

CPU Registers

Registers R0-R7

Program Status Word

Accumulator

B Register

Stack Pointer

Instruction Set Summary

Interrupts

Interrupt Masking

Interrupt Processing

Interrupt Priority

Oscillators and clocks

Debug Interface

Debug Mode

Debug Communication

Debug Commands

Debug Lock Bit

Debug Configuration

Debug Status

Hardware Breakpoints

Flash Programming

RAM

Flash Memory

Memory Arbiter

Peripherals

I/O ports

General Purpose I/O

General Purpose I/O Interrupts

General Purpose I/O DMA

Peripheral I/O

USART0

USART1

Timer 1

Timer 3

Timer 4

ADC

Debug interface

32.768 kHz XOSC input

Unused I/O pins

I/O registers

DMA Controller

DMA Operation

DMA Configuration Parameters

Source Address

Destination Address

Transfer Count

VLEN Setting

Trigger Event

Source and Destination Increment

DMA Transfer Mode

DMA Priority

Byte or Word transfers

Interrupt mask

Mode 8 setting

DMA Configuration Setup

Stopping DMA Transfers

DMA Interrupts

DMA Configuration Data Structure

DMA registers

16-bit Timer, Timer1

16-bit Timer Counter

Timer 1 Operation

Free-running Mode

Modulo Mode

Up/down Mode

Channel Mode Control

Input Capture Mode

RF Event Capture

Output Compare Mode

Timer 1 Interrupts

DMA Triggers

Timer 1 Registers

MAC Timer (Timer 2)

Timer Operation

General

Up Counter

Timer overflow

Timer delta increment

Timer Compare

Capture Input

Overflow count

Overflow count compare

Interrupts

DMA Triggers

Timer start/stop synchronization

General

Timer synchronous stop

Timer synchronous start

Timer 2 Registers

Sleep Timer

Timer Operation

General

Timer Compare

8-bit Timer 3 and Timer 4

8-bit Timer Counter

Timer 3/4 Mode Control

Channel Mode Control

Input Capture Mode

Output Compare Mode

Timer 3 and 4 interrupts

Timer 3 and Timer 4 DMA triggers

Timer 3 and 4 registers

ADC

ADC Introduction

ADC Operation

ADC Core

ADC conversion sequences

ADC Inputs

ADC Operating Modes

ADC Conversion Results

ADC Reference Voltage

ADC Conversion Timing

ADC Interrupts

ADC DMA Triggers

ADC Registers

Random Generator

Introduction

Random Generator Operation

Semi random sequence generation

Seeding

CRC16

Registers

AES Coprocessor

AES Operation

Key and IV

Padding of input data

Interface to CPU

Modes of operation

CBC-MAC

CCM mode

Sharing the AES coprocessor between layers

AES Interrupts

AES DMA Triggers

AES Registers

Power Management

Power Management Introduction

PM0

PM1

PM2

PM3

Power Management Control

System clock

High-speed oscillators

32.768 kHz oscillators

Timer Tick generation

Data Retention

Power Management Registers

Power On Reset and Brown Out Detector

Watchdog Timer

Watchdog mode

Timer mode

Watchdog Timer Example

Watchdog Timer Register

USART

UART mode

UART Transmit

UART Receive

UART Hardware Flow Control

UART Character Format

SPI Mode

SPI Master Operation

SPI Slave Operation

Baud Rate Generation

USART flushing

USART Interrupts

USART DMA Triggers

USART Registers

FLASH Controller

Flash Write

DMA Flash Write

CPU Flash Write

Flash Page Erase

Flash Lock Protection

Flash Write Timing

Flash DMA trigger

Flash Controller Registers

Radio

IEEE 802.15.4 Modulation Format

Command strobes

RF Registers

Interrupts

Interrupt registers

FIFO access

DMA

Receive mode

RXFIFO overflow

Transmit mode

General control and status

Demodulator, Symbol Synchronizer and Data Decision

Frame Format

Synchronization header

Length field

MAC protocol data unit

Frame check sequence

RF Data Buffering

Buffered transmit mode

Buffered receive mode

Address Recognition

Acknowledge Frames

Radio control state machine

MAC Security Operations (Encryption and Authentication)

Linear IF and AGC Settings

RSSI / Energy Detection

Link Quality Indication

Clear Channel Assessment

Frequency and Channel Programming

VCO and PLL Self-Calibration

VCO

PLL self-calibration

Output Power Programming

Input / Output Matching

Transmitter Test Modes

Unmodulated carrier

Modulated spectrum

System Considerations and Guidelines

SRD regulations

Frequency hopping and multi-channel systems

Data burst transmissions

Crystal accuracy and drift

Communication robustness

Communication security

Low cost systems

Battery operated systems

BER / PER measurements

PCB Layout Recommendation

Antenna Considerations

CSMA/CA Strobe Processor

Instruction Memory

Data Registers

Program Execution

Interrupt Requests

Random Number Instruction

Running CSP Programs

Instruction Set Summary

Instruction Set Definition

DECZ

DECY

INCY

INCMAXY

RANDXY

INT

WAITX

WAIT W

WEVENT

LABEL

RPT C

SKIP S, C

STOP

SNOP

STXCALN

SRXON

STXON

STXONCCA

SRFOFF

SFLUSHRX

SFLUSHTX

SACK

SACKPEND

ISSTOP

ISSTART

ISTXCALN

ISRXON

ISTXON

ISTXONCCA

ISRFOFF

ISFLUSHRX

ISFLUSHTX

ISACK

ISACKPEND

Example programs

Radio Registers

Radio Test Output Signals

Voltage Regulators

Voltage Regulators Power-on

Evaluation Software

Register overview

Package Description (QLP 48)

Recommended PCB layout for package (QLP 48)

Package thermal properties

Soldering information

Plastic tube specification

Carrier tape and reel specification

Ordering Information

General Information

Document History

Product Status Definitions

Disclaimer

Trademarks

Life Support Policy

Address Information