悠景科技股份有限公司

UG-2864HSWEG01

128X64

Evaluation Kit User Guide

Writer: James Wang

E-mail: James_Wang@univision.com.tw

Version: Preliminary

1

�

悠景科技股份有限公司

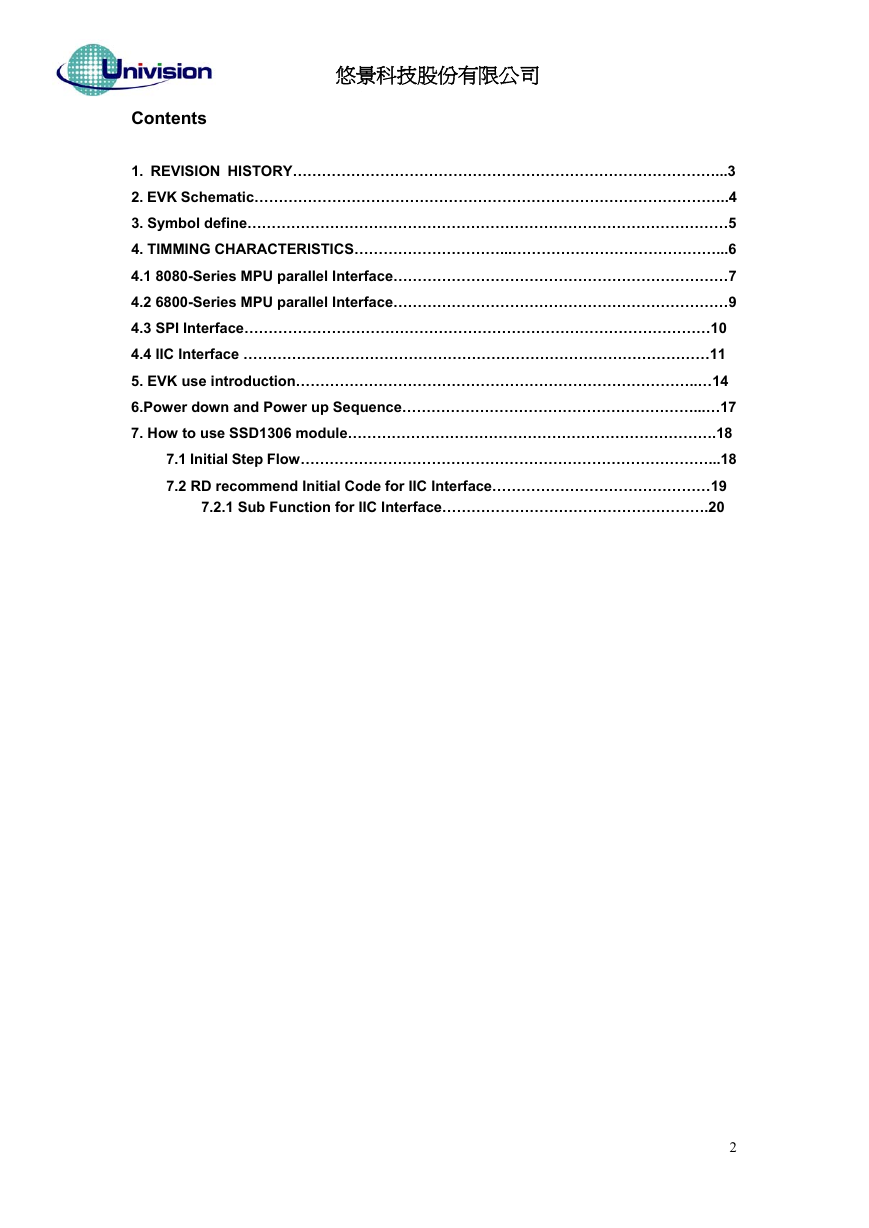

Contents

1. REVISION HISTORY……………………………………………………………………………...3

2. EVK Schematic……………………………………………………………………………………..4

3. Symbol define………………………………………………………………………………………5

4. TIMMING CHARACTERISTICS…………………………...……………………………………...6

4.1 8080-Series MPU parallel Interface……………………………………………………………7

4.2 6800-Series MPU parallel Interface……………………………………………………………9

4.3 SPI Interface……………………………………………………………………………………10

4.4 IIC Interface ……………………………………………………………………………………11

5. EVK use introduction………………………………………………………………………..…14

6.Power down and Power up Sequence……………………………………………………...…17

7. How to use SSD1306 module………………………………………………………………….18

7.1 Initial Step Flow…………………………………………………………………………...18

7.2 RD recommend Initial Code for IIC Interface………………………………………19

7.2.1 Sub Function for IIC Interface……………………………………………….20

2

�

悠景科技股份有限公司

1. REVISION HISTORY

Page Contents

Date

2008/10/01

Preliminary

Version

Preliminary 0.0

3

�

悠景科技股份有限公司

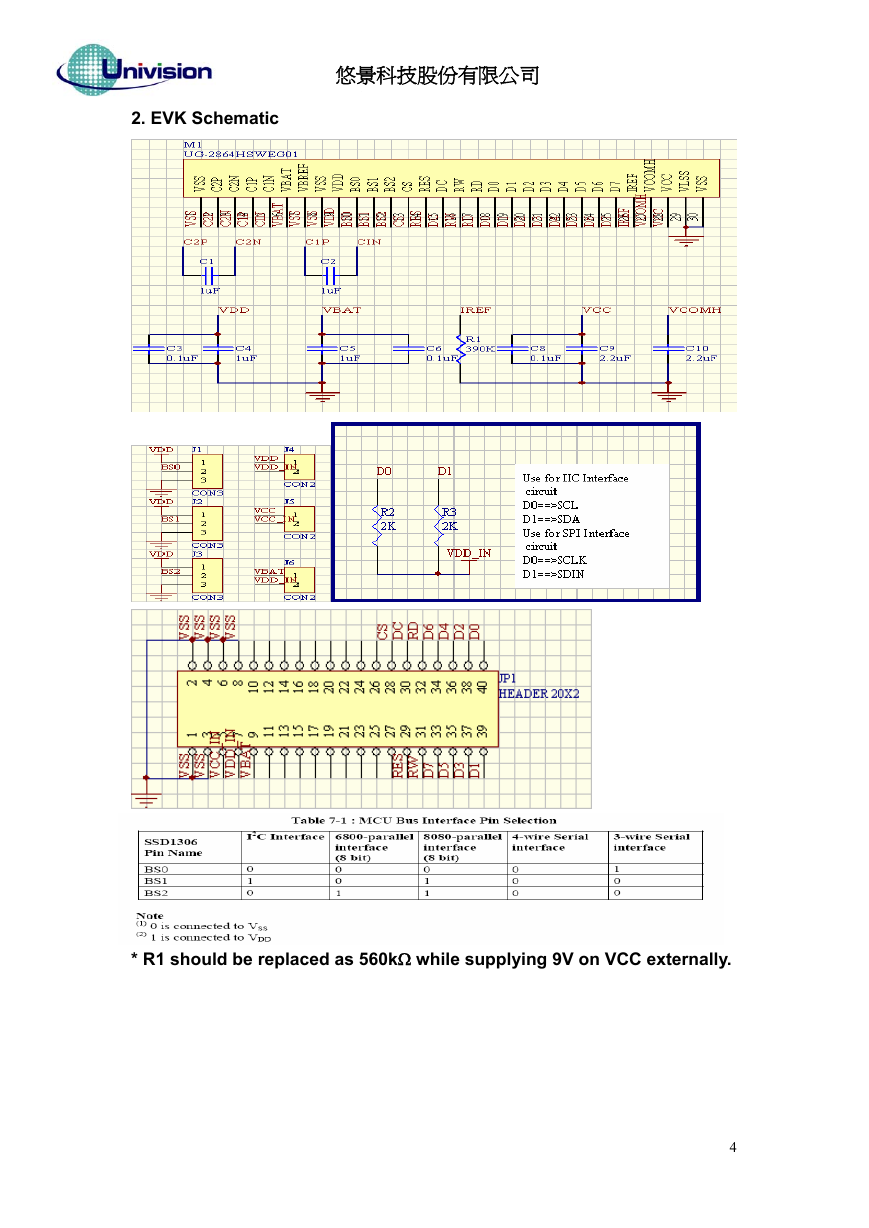

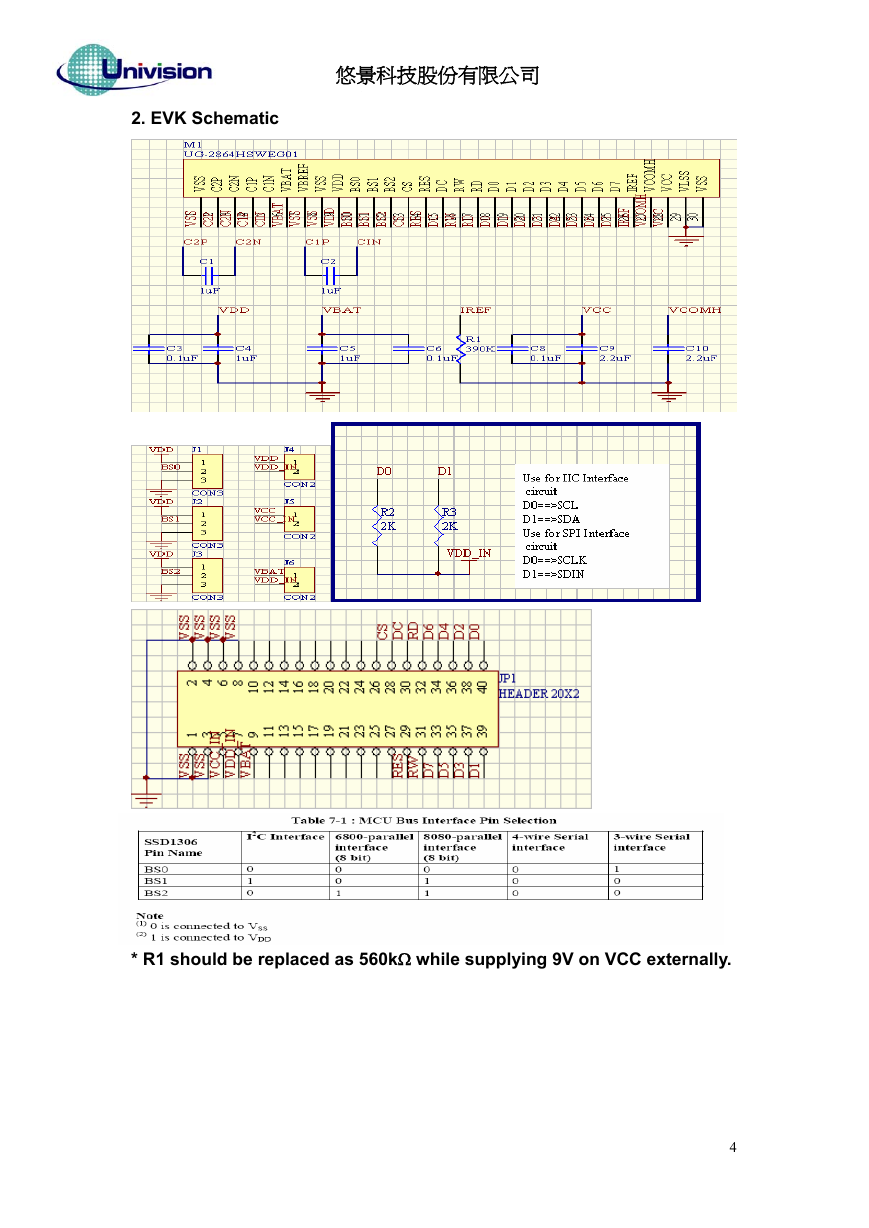

2. EVK Schematic

* R1 should be replaced as 560kΩ while supplying 9V on VCC externally.

4

�

悠景科技股份有限公司

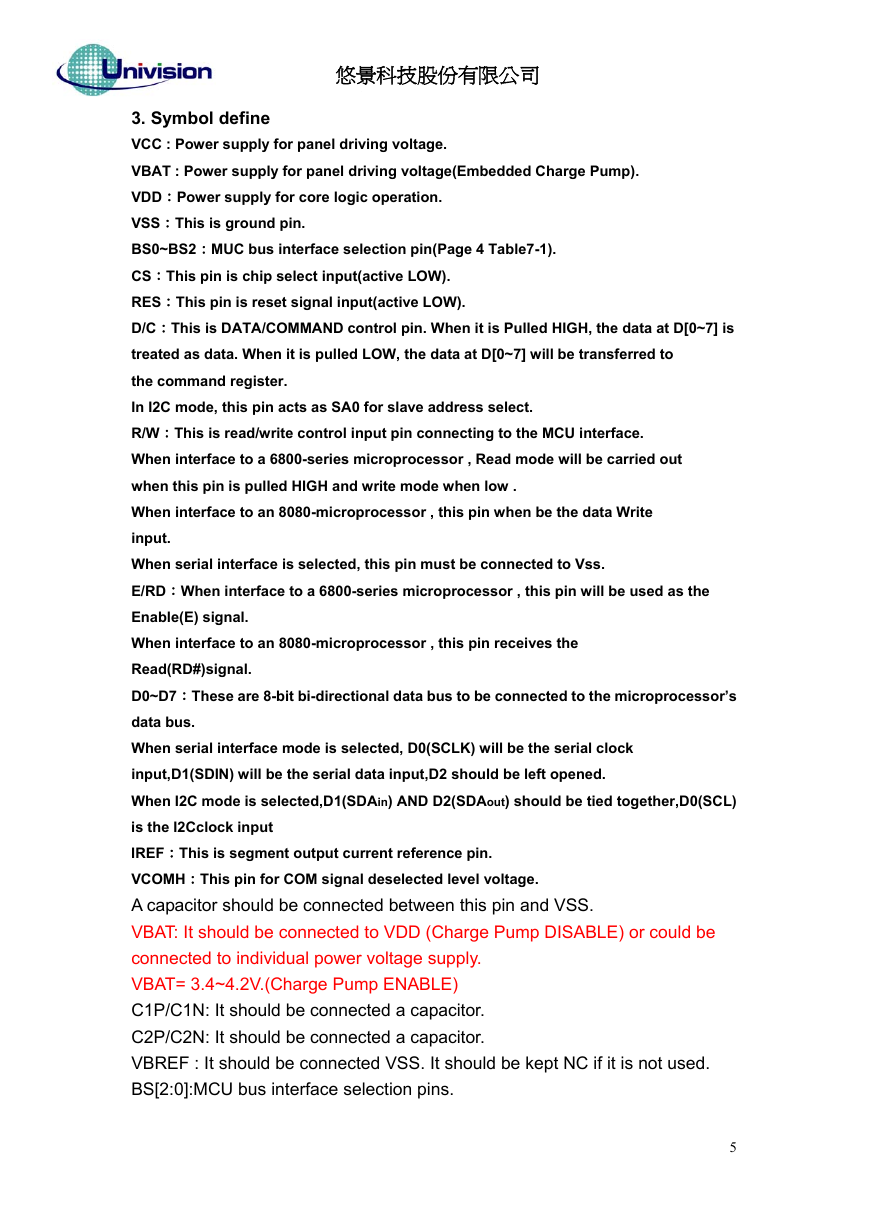

3. Symbol define

VCC : Power supply for panel driving voltage.

VBAT : Power supply for panel driving voltage(Embedded Charge Pump).

VDD:Power supply for core logic operation.

VSS:This is ground pin.

BS0~BS2:MUC bus interface selection pin(Page 4 Table7-1).

CS:This pin is chip select input(active LOW).

RES:This pin is reset signal input(active LOW).

D/C:This is DATA/COMMAND control pin. When it is Pulled HIGH, the data at D[0~7] is

treated as data. When it is pulled LOW, the data at D[0~7] will be transferred to

the command register.

In I2C mode, this pin acts as SA0 for slave address select.

R/W:This is read/write control input pin connecting to the MCU interface.

When interface to a 6800-series microprocessor , Read mode will be carried out

when this pin is pulled HIGH and write mode when low .

When interface to an 8080-microprocessor , this pin when be the data Write

input.

When serial interface is selected, this pin must be connected to Vss.

E/RD:When interface to a 6800-series microprocessor , this pin will be used as the

Enable(E) signal.

When interface to an 8080-microprocessor , this pin receives the

Read(RD#)signal.

D0~D7:These are 8-bit bi-directional data bus to be connected to the microprocessor’s

data bus.

When serial interface mode is selected, D0(SCLK) will be the serial clock

input,D1(SDIN) will be the serial data input,D2 should be left opened.

When I2C mode is selected,D1(SDAin) AND D2(SDAout) should be tied together,D0(SCL)

is the I2Cclock input

IREF:This is segment output current reference pin.

VCOMH:This pin for COM signal deselected level voltage.

A capacitor should be connected between this pin and VSS.

VBAT: It should be connected to VDD (Charge Pump DISABLE) or could be

connected to individual power voltage supply.

VBAT= 3.4~4.2V.(Charge Pump ENABLE)

C1P/C1N: It should be connected a capacitor.

C2P/C2N: It should be connected a capacitor.

VBREF : It should be connected VSS. It should be kept NC if it is not used.

BS[2:0]:MCU bus interface selection pins.

5

�

悠景科技股份有限公司

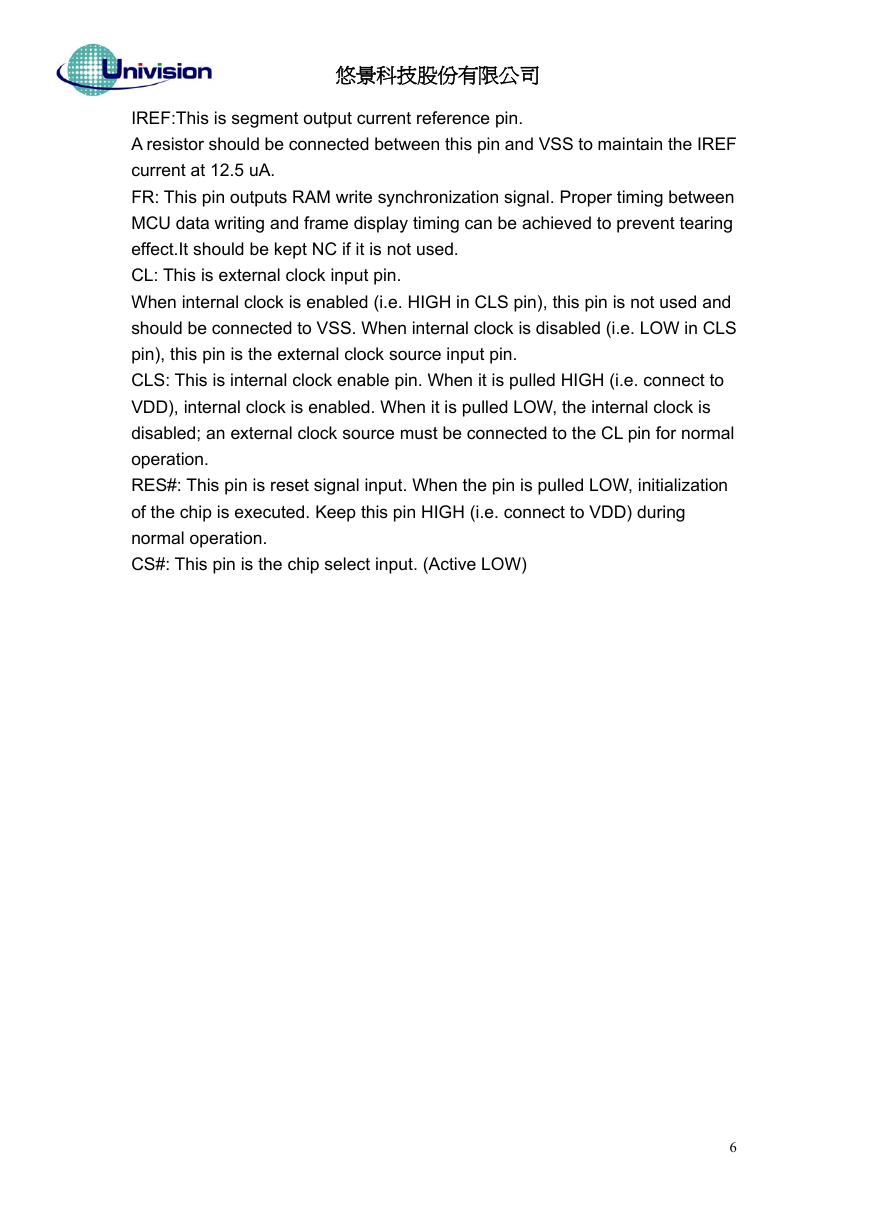

IREF:This is segment output current reference pin.

A resistor should be connected between this pin and VSS to maintain the IREF

current at 12.5 uA.

FR: This pin outputs RAM write synchronization signal. Proper timing between

MCU data writing and frame display timing can be achieved to prevent tearing

effect.It should be kept NC if it is not used.

CL: This is external clock input pin.

When internal clock is enabled (i.e. HIGH in CLS pin), this pin is not used and

should be connected to VSS. When internal clock is disabled (i.e. LOW in CLS

pin), this pin is the external clock source input pin.

CLS: This is internal clock enable pin. When it is pulled HIGH (i.e. connect to

VDD), internal clock is enabled. When it is pulled LOW, the internal clock is

disabled; an external clock source must be connected to the CL pin for normal

operation.

RES#: This pin is reset signal input. When the pin is pulled LOW, initialization

of the chip is executed. Keep this pin HIGH (i.e. connect to VDD) during

normal operation.

CS#: This pin is the chip select input. (Active LOW)

6

�

悠景科技股份有限公司

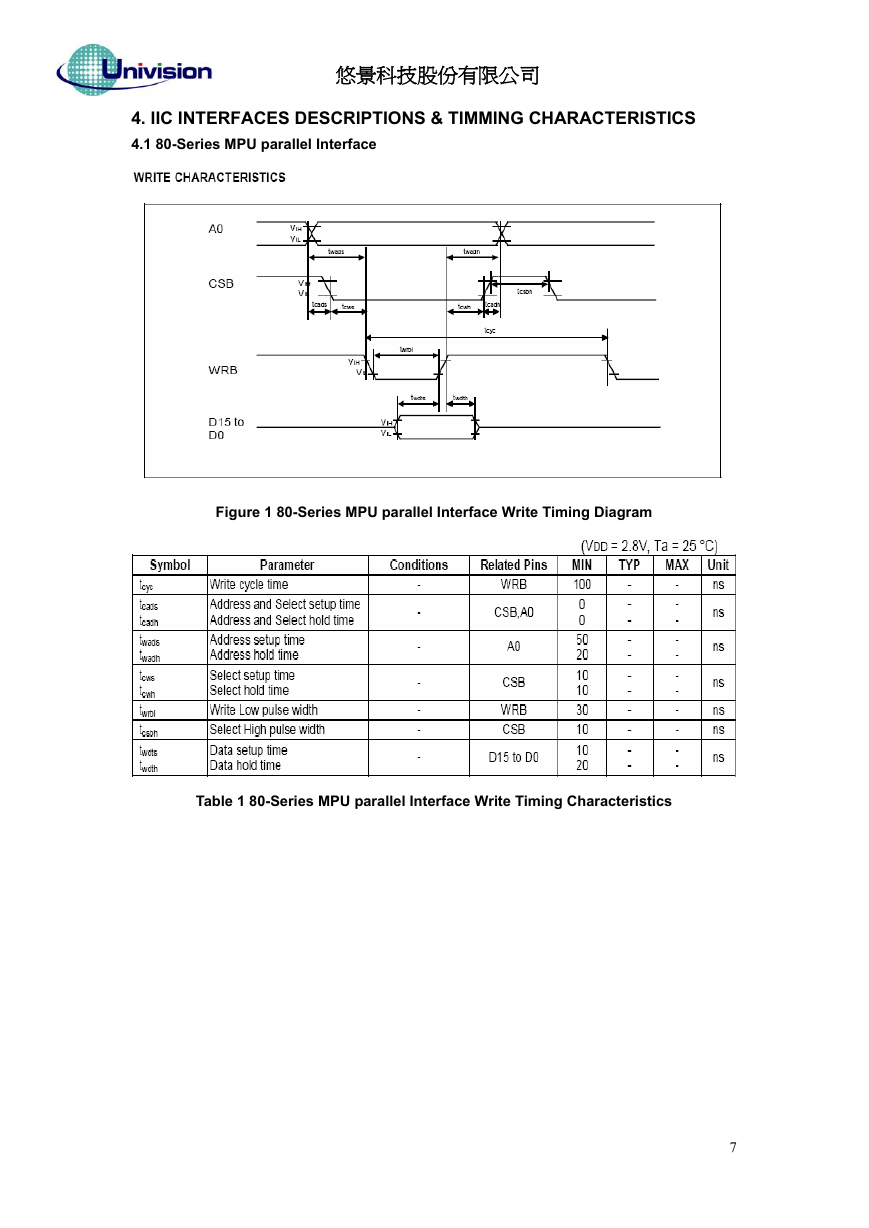

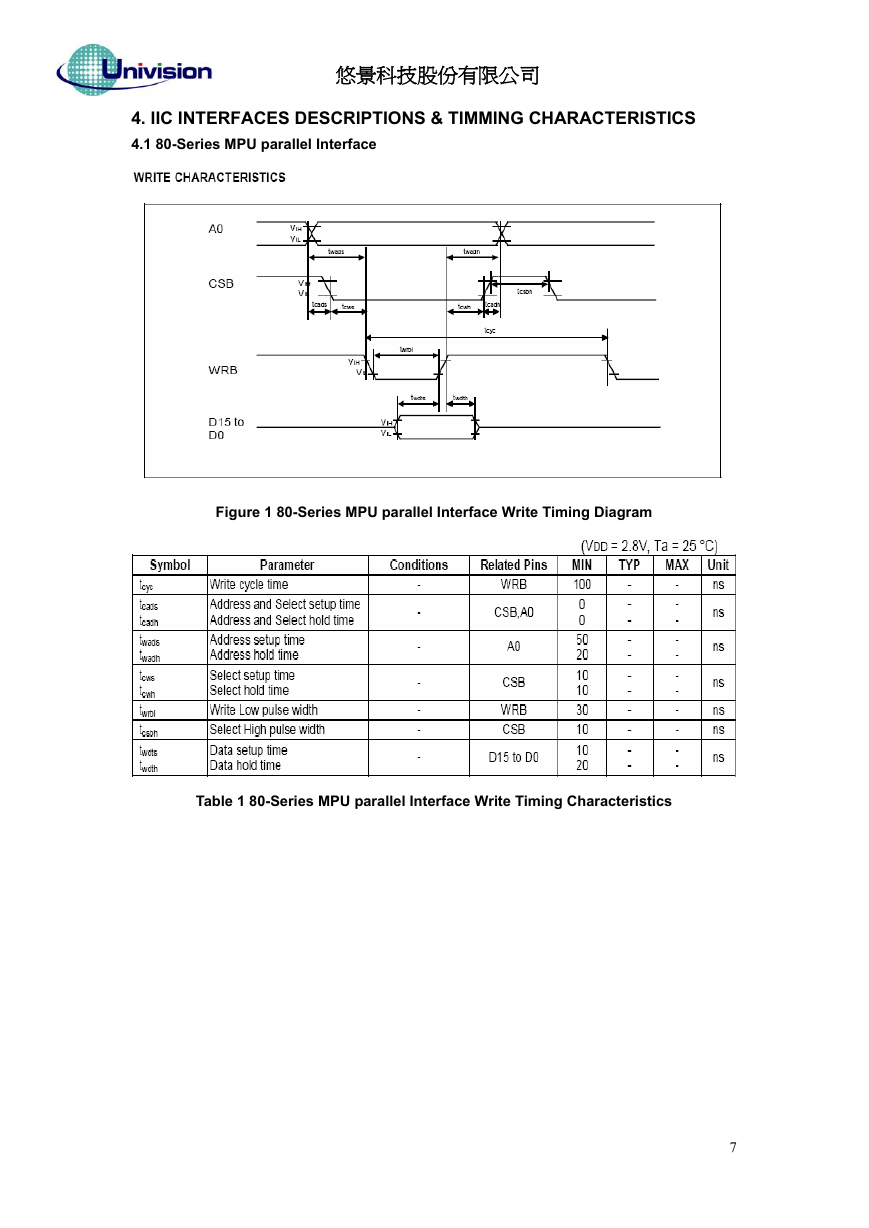

4. IIC INTERFACES DESCRIPTIONS & TIMMING CHARACTERISTICS

4.1 80-Series MPU parallel Interface

Figure 1 80-Series MPU parallel Interface Write Timing Diagram

Table 1 80-Series MPU parallel Interface Write Timing Characteristics

7

�

悠景科技股份有限公司

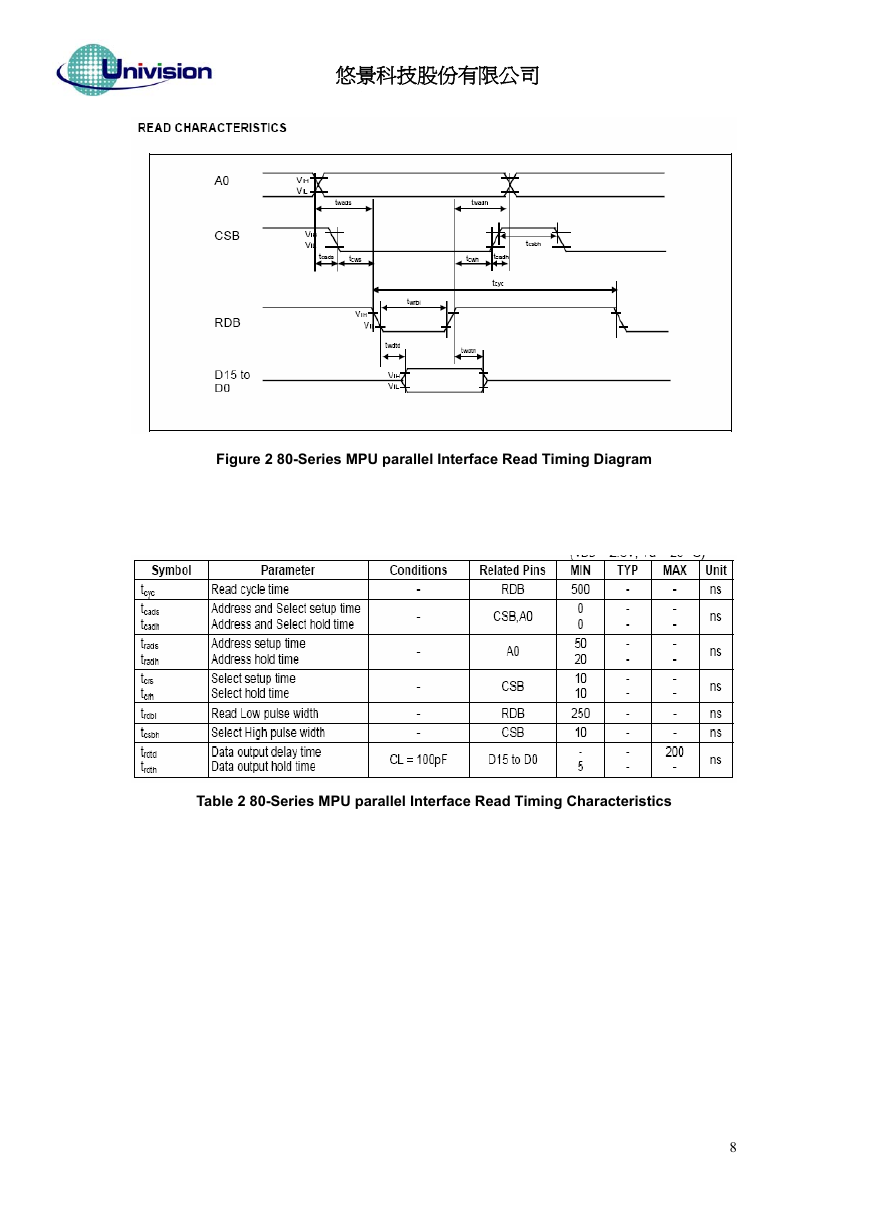

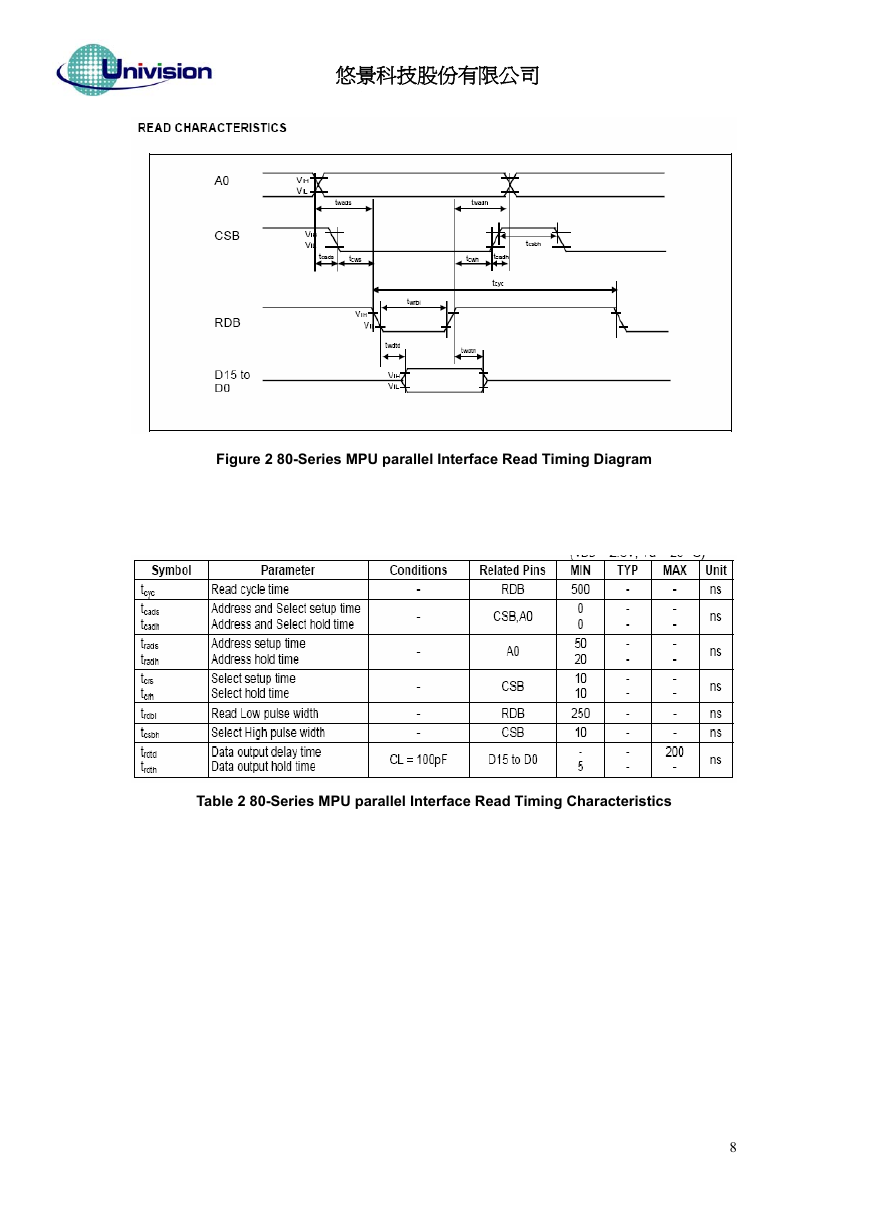

Figure 2 80-Series MPU parallel Interface Read Timing Diagram

Table 2 80-Series MPU parallel Interface Read Timing Characteristics

8

�