【资料截图】

【资料目录】

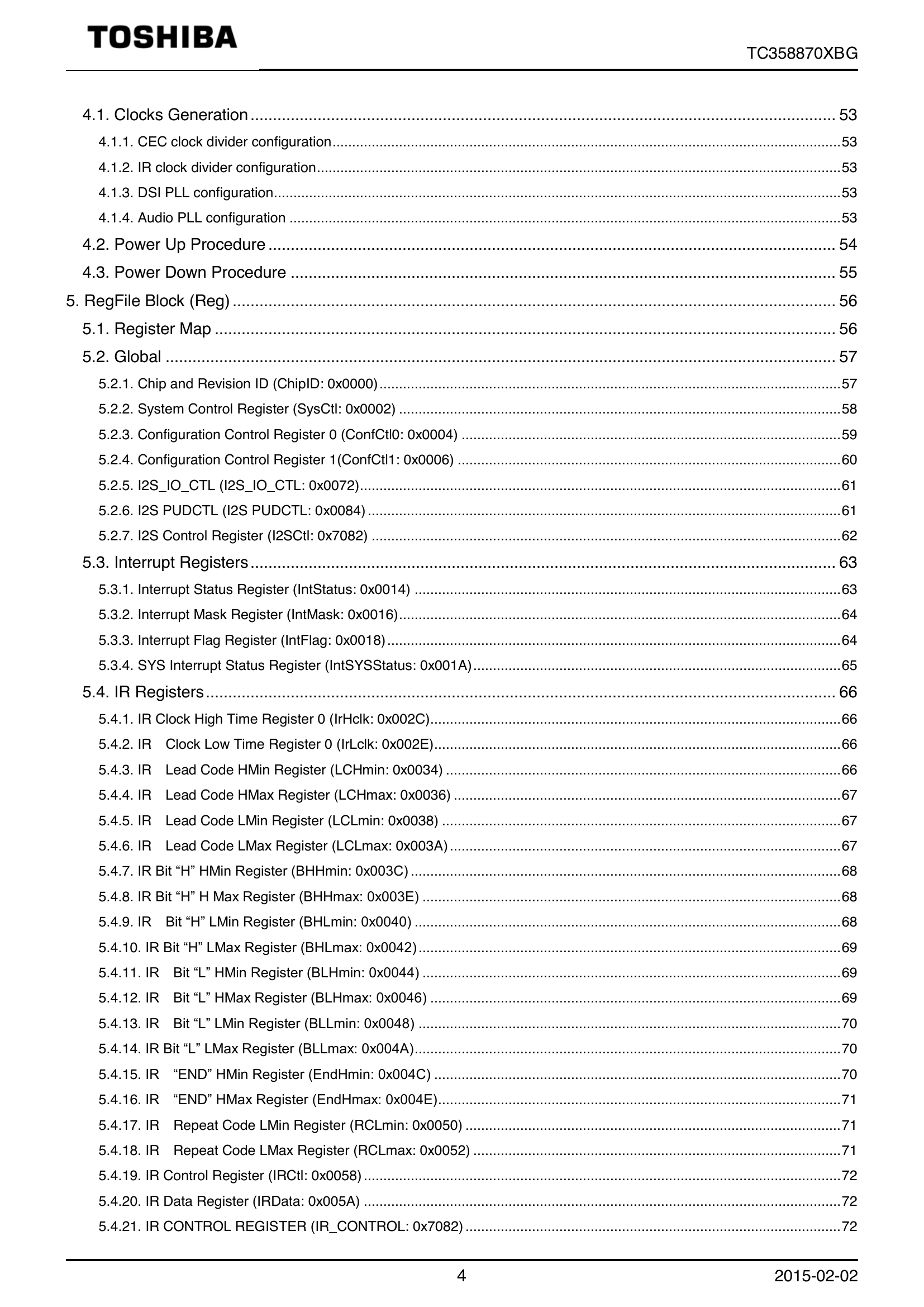

Table of content

REFERENCES................................................................................................................................................... 20

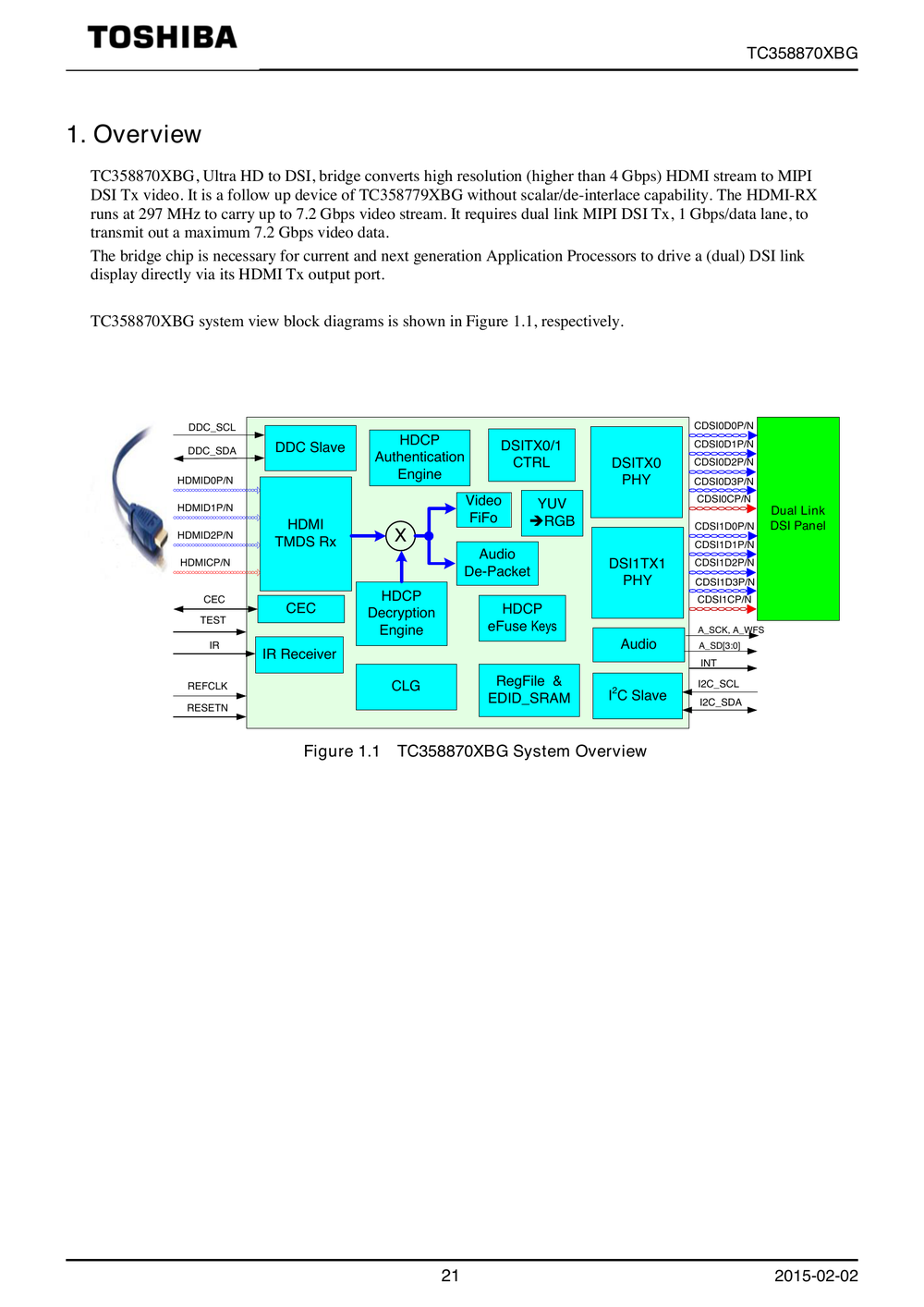

1. Overview ........................................................................................................................................................ 21

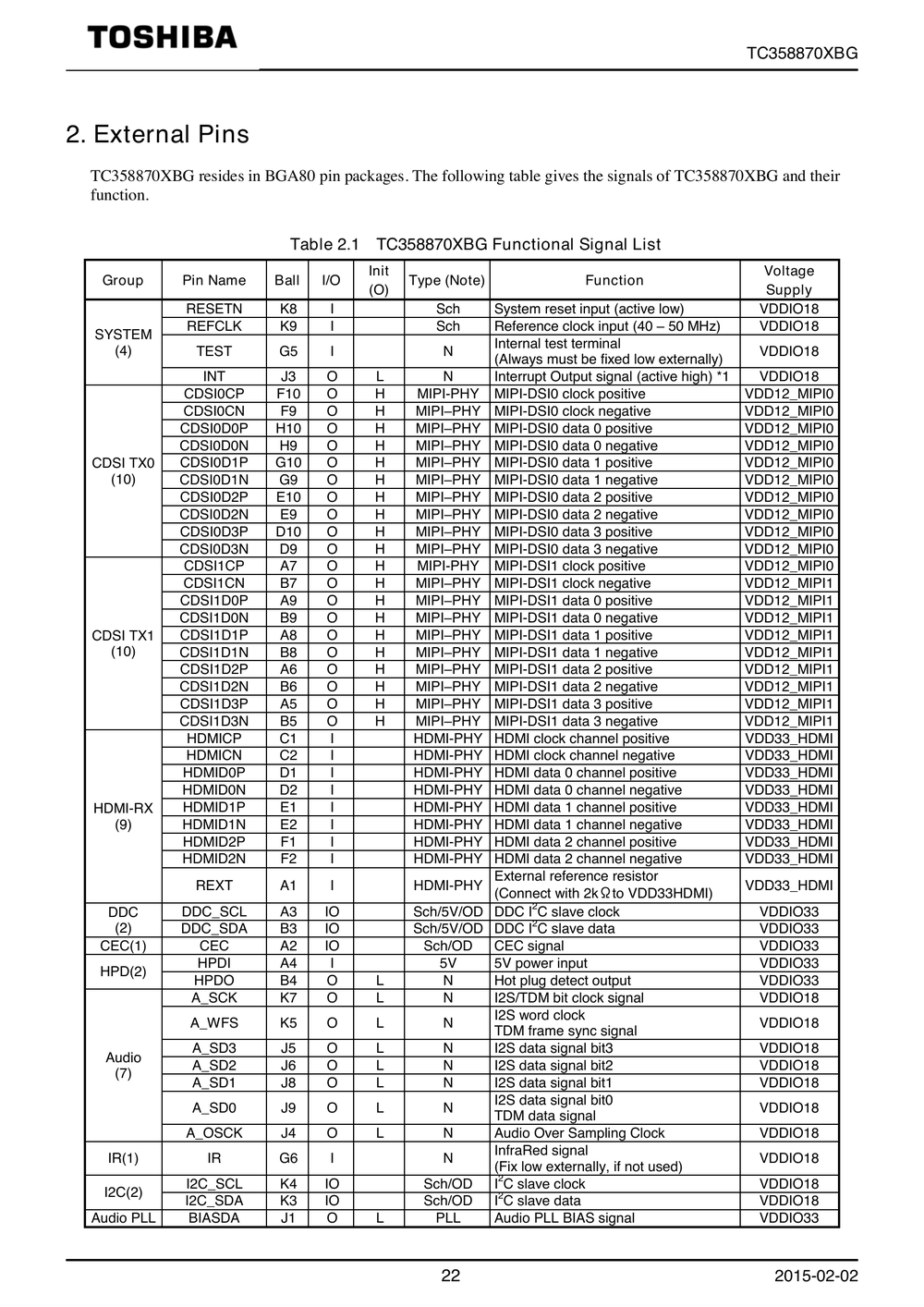

2. External Pins .................................................................................................................................................. 22

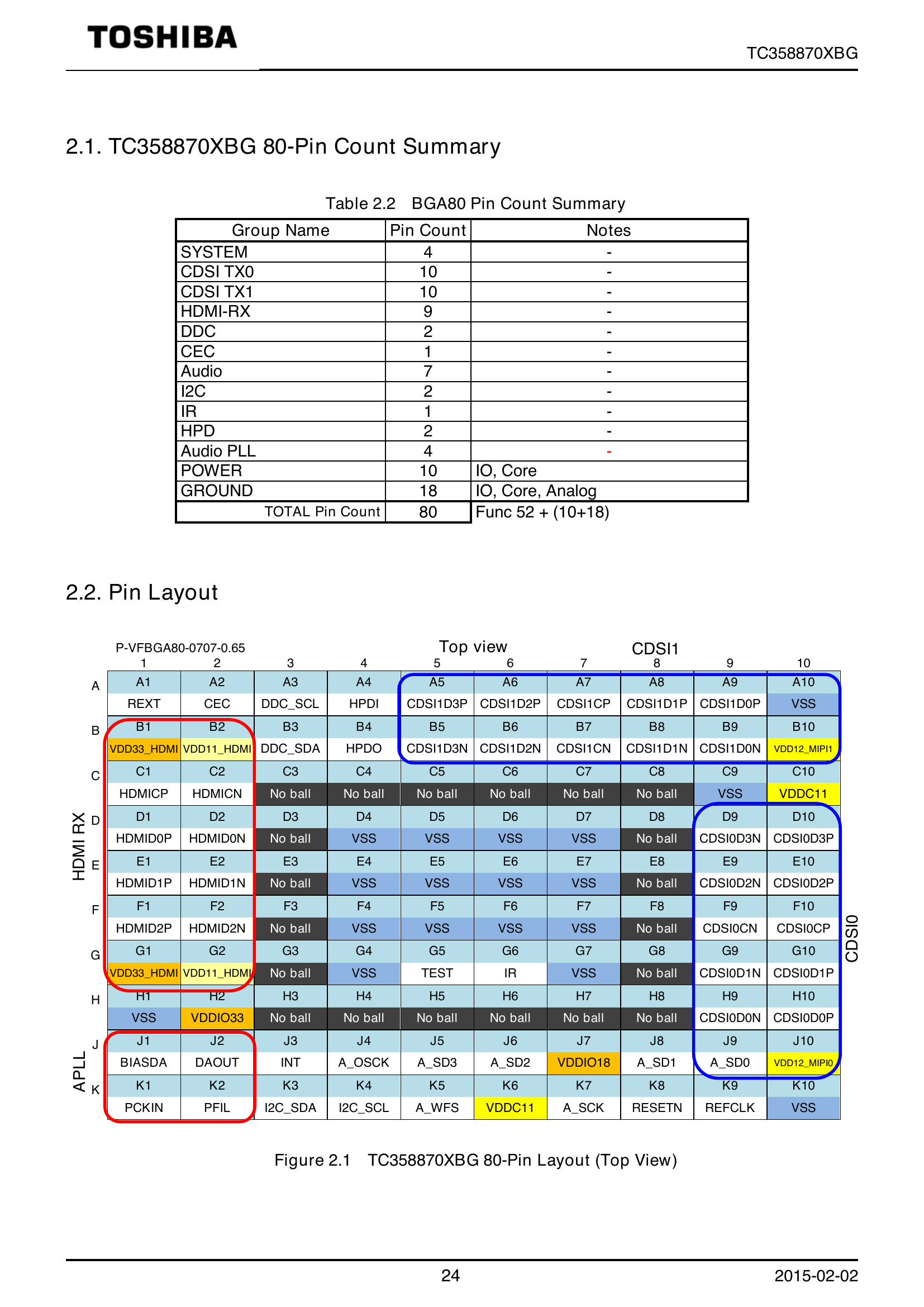

2.1. TC358870XBG 80-Pin Count Summary ................................................................................................. 24

2.2. Pin Layout................................................................................................................................................ 24

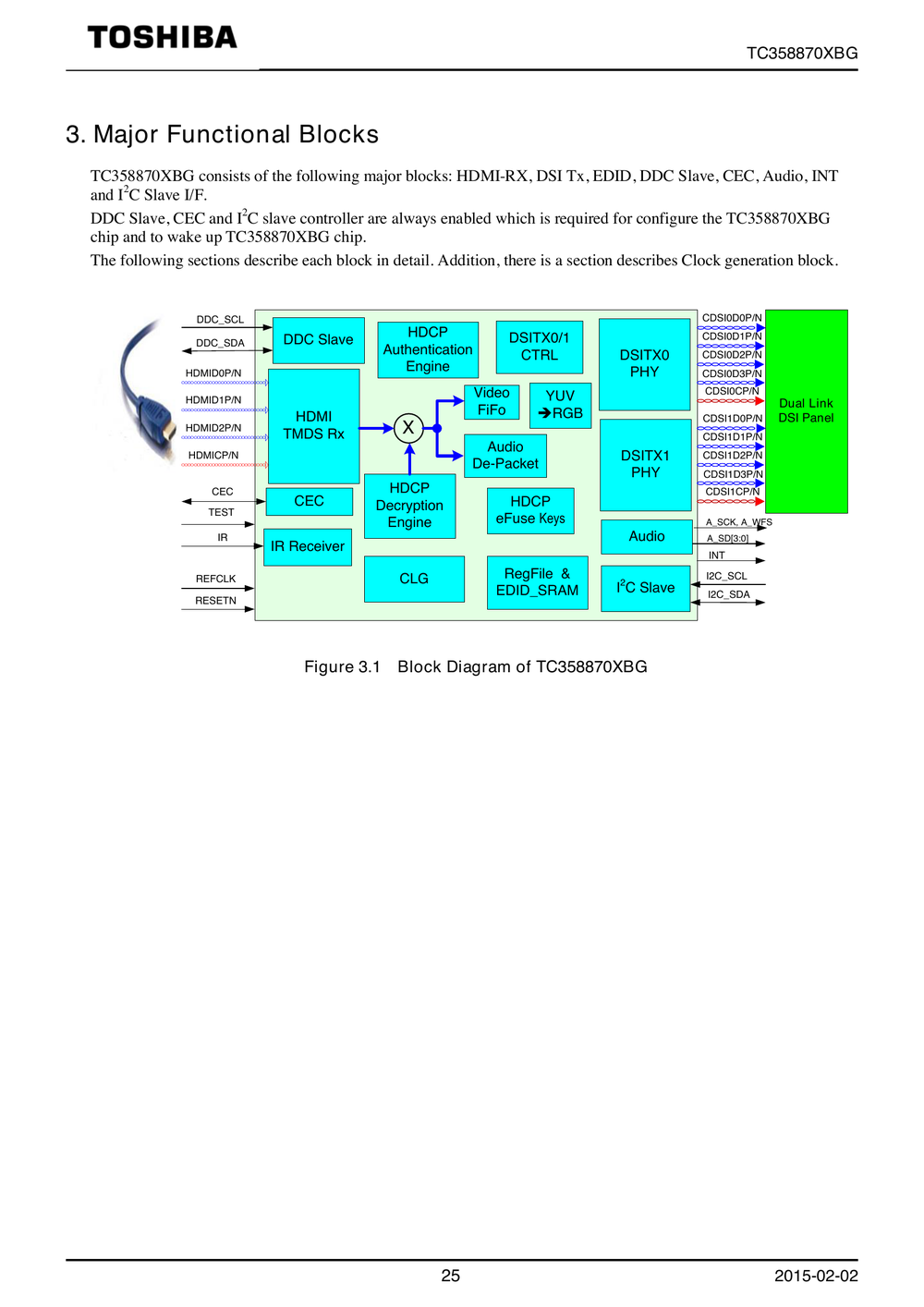

3. Major Functional Blocks ................................................................................................................................. 25

3.1. HDMI-RX ................................................................................................................................................. 26

3.1.1. 3D Support .................................................................................................................................................................26

3.1.2. InfoFrame Data...........................................................................................................................................................26

3.2. Line Split.................................................................................................................................................. 28

3.3. DSI Tx Controller..................................................................................................................................... 30

3.3.1. DSI TX Application .....................................................................................................................................................30

3.3.1.1. Program/Initialize DSI Panel..........................................................................................................................................30

3.3.2. DSI TX Command Packet Operation..........................................................................................................................30

3.3.3. TX Short Packet (DCS) Write Command....................................................................................................................31

3.3.4. TX Long Packet Write Command (limited to 512-byte in length)................................................................................32

3.3.5. LPRX Packet Read Command ...................................................................................................................................34

3.3.6. 3D Support .................................................................................................................................................................35

3.4. CEC Controller ........................................................................................................................................ 35

3.4.1. Receive Operation Sequence.....................................................................................................................................35

3.4.1.1. Noise cancellation time .................................................................................................................................................36

3.4.1.2. Start bit detection ..........................................................................................................................................................36

3.4.1.3. Waveform Error Detection.............................................................................................................................................37

3.4.1.4. Data sampling timing.....................................................................................................................................................37

3.4.2. Transmit Operation Sequence....................................................................................................................................38

3.4.2.1. Wait Time for Bus to be Free.........................................................................................................................................38

3.4.2.2. Transmission Timing .....................................................................................................................................................39

3.4.3. Arbitration lost.............................................................................................................................................................39

3.4.4. Low level functions .....................................................................................................................................................40

3.5. Audio Output Function............................................................................................................................. 41

3.5.1. I2S Interface ...............................................................................................................................................................41

3.5.1.1. Normal Mode.................................................................................................................................................................41

3.5.1.2. HBR Split over I2S ........................................................................................................................................................44

3.5.2. TDM (Time Division Multiplexed) Audio Interface.......................................................................................................45

3.6. InfraRed (IR) Interface............................................................................................................................. 46

3.6.1. Programmable timing .................................................................................................................................................47

3.6.2. Basic Operation..........................................................................................................................................................48

3.7. I2C............................................................................................................................................................ 48

Providing Register Address over I2

3.7.1. C Bus ...................................................................................................................49

I

2

3.7.2. C Write Access Translation......................................................................................................................................50

I

2

3.7.3. C Read Access Translation......................................................................................................................................50

4. Clock and System .......................................................................................................................................... 51

TC358870XBG

4 2015-02-02

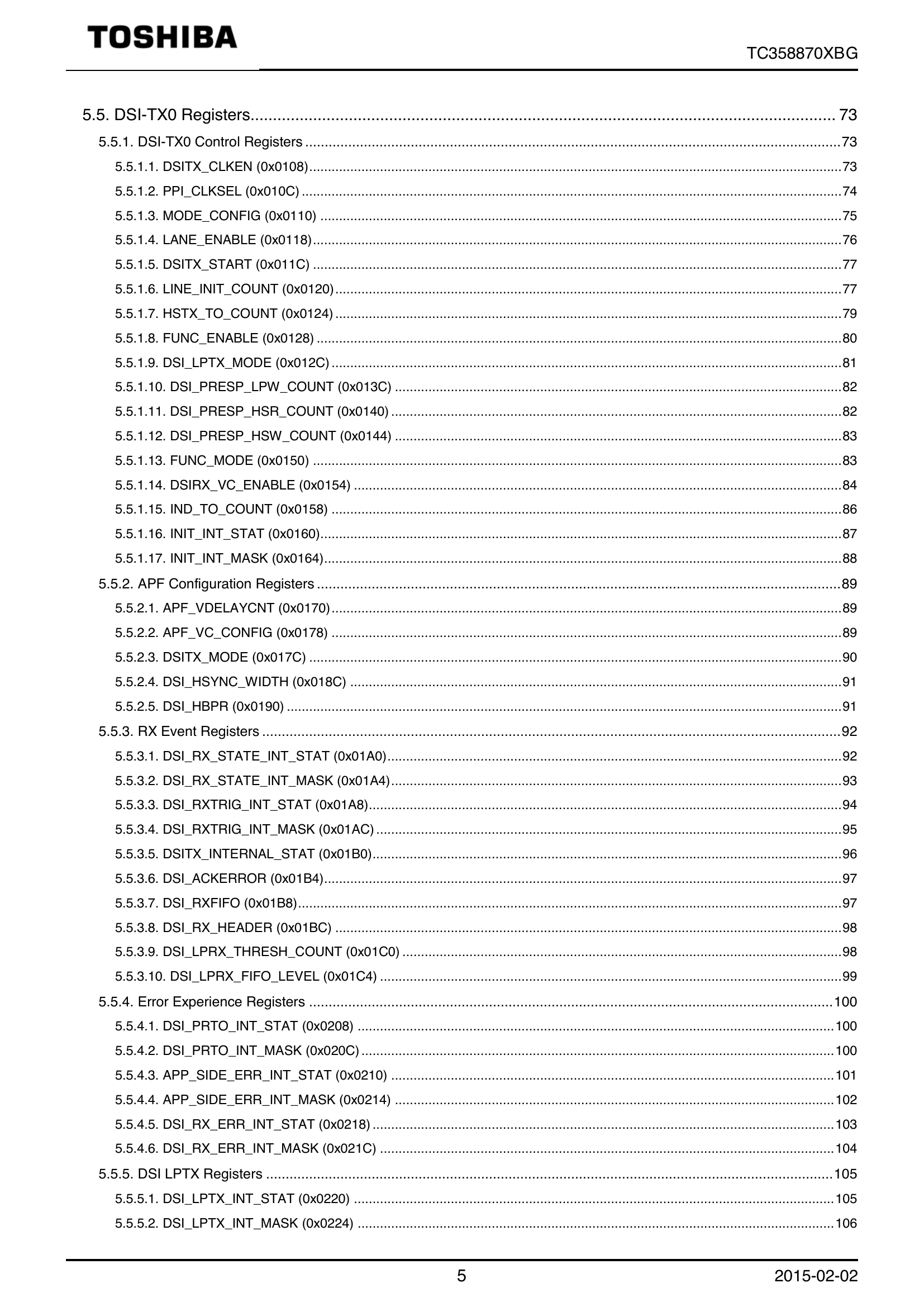

4.1. Clocks Generation................................................................................................................................... 53

4.1.1. CEC clock divider configuration..................................................................................................................................53

4.1.2. IR clock divider configuration......................................................................................................................................53

4.1.3. DSI PLL configuration.................................................................................................................................................53

4.1.4. Audio PLL configuration .............................................................................................................................................53

4.2. Power Up Procedure ............................................................................................................................... 54

4.3. Power Down Procedure .......................................................................................................................... 55

5. RegFile Block (Reg)....................................................................................................................................... 56

5.1. Register Map ........................................................................................................................................... 56

5.2. Global ...................................................................................................................................................... 57

5.2.1. Chip and Revision ID (ChipID: 0x0000)......................................................................................................................57

5.2.2. System Control Register (SysCtl: 0x0002) .................................................................................................................58

5.2.3. Configuration Control Register 0 (ConfCtl0: 0x0004) .................................................................................................59

5.2.4. Configuration Control Register 1(ConfCtl1: 0x0006) ..................................................................................................60

5.2.5. I2S_IO_CTL (I2S_IO_CTL: 0x0072)...........................................................................................................................61

5.2.6. I2S PUDCTL (I2S PUDCTL: 0x0084).........................................................................................................................61

5.2.7. I2S Control Register (I2SCtl: 0x7082) ........................................................................................................................62

5.3. Interrupt Registers................................................................................................................................... 63

5.3.1. Interrupt Status Register (IntStatus: 0x0014) .............................................................................................................63

5.3.2. Interrupt Mask Register (IntMask: 0x0016).................................................................................................................64

5.3.3. Interrupt Flag Register (IntFlag: 0x0018)....................................................................................................................64

5.3.4. SYS Interrupt Status Register (IntSYSStatus: 0x001A)..............................................................................................65

5.4. IR Registers............................................................................................................................................. 66

5.4.1. IR Clock High Time Register 0 (IrHclk: 0x002C).........................................................................................................66

5.4.2. IR Clock Low Time Register 0 (IrLclk: 0x002E)........................................................................................................66

5.4.3. IR Lead Code HMin Register (LCHmin: 0x0034) .....................................................................................................66

5.4.4. IR Lead Code HMax Register (LCHmax: 0x0036) ...................................................................................................67

5.4.5. IR Lead Code LMin Register (LCLmin: 0x0038) ......................................................................................................67

5.4.6. IR Lead Code LMax Register (LCLmax: 0x003A)....................................................................................................67

5.4.7. IR Bit “H” HMin Register (BHHmin: 0x003C) ..............................................................................................................68

5.4.8. IR Bit “H” H Max Register (BHHmax: 0x003E) ...........................................................................................................68

5.4.9. IR Bit “H” LMin Register (BHLmin: 0x0040) .............................................................................................................68

5.4.10. IR Bit “H” LMax Register (BHLmax: 0x0042)............................................................................................................69

5.4.11. IR Bit “L” HMin Register (BLHmin: 0x0044) ...........................................................................................................69

5.4.12. IR Bit “L” HMax Register (BLHmax: 0x0046) .........................................................................................................69

5.4.13. IR Bit “L” LMin Register (BLLmin: 0x0048) ............................................................................................................70

5.4.14. IR Bit “L” LMax Register (BLLmax: 0x004A).............................................................................................................70

5.4.15. IR “END” HMin Register (EndHmin: 0x004C) ........................................................................................................70

5.4.16. IR “END” HMax Register (EndHmax: 0x004E).......................................................................................................71

5.4.17. IR Repeat Code LMin Register (RCLmin: 0x0050) ................................................................................................71

5.4.18. IR Repeat Code LMax Register (RCLmax: 0x0052) ..............................................................................................71

5.4.19. IR Control Register (IRCtl: 0x0058)..........................................................................................................................72

5.4.20. IR Data Register (IRData: 0x005A) ..........................................................................................................................72

5.4.21. IR CONTROL REGISTER (IR_CONTROL: 0x7082)................................................................................................72

TC358870XBG

5 2015-02-02

5.5. DSI-TX0 Registers................................................................................................................................... 73

5.5.1. DSI-TX0 Control Registers .........................................................................................................................................73

5.5.1.1. DSITX_CLKEN (0x0108)...............................................................................................................................................73

5.5.1.2. PPI_CLKSEL (0x010C).................................................................................................................................................74

5.5.1.3. MODE_CONFIG (0x0110) ............................................................................................................................................75

5.5.1.4. LANE_ENABLE (0x0118)..............................................................................................................................................76

5.5.1.5. DSITX_START (0x011C) ..............................................................................................................................................77

5.5.1.6. LINE_INIT_COUNT (0x0120)........................................................................................................................................77

5.5.1.7. HSTX_TO_COUNT (0x0124)........................................................................................................................................79

5.5.1.8. FUNC_ENABLE (0x0128) .............................................................................................................................................80

5.5.1.9. DSI_LPTX_MODE (0x012C).........................................................................................................................................81

5.5.1.10. DSI_PRESP_LPW_COUNT (0x013C) ........................................................................................................................82

5.5.1.11. DSI_PRESP_HSR_COUNT (0x0140).........................................................................................................................82

5.5.1.12. DSI_PRESP_HSW_COUNT (0x0144) ........................................................................................................................83

5.5.1.13. FUNC_MODE (0x0150) ..............................................................................................................................................83

5.5.1.14. DSIRX_VC_ENABLE (0x0154) ...................................................................................................................................84

5.5.1.15. IND_TO_COUNT (0x0158) .........................................................................................................................................86

5.5.1.16. INIT_INT_STAT (0x0160)............................................................................................................................................87

5.5.1.17. INIT_INT_MASK (0x0164)...........................................................................................................................................88

5.5.2. APF Configuration Registers ......................................................................................................................................89

5.5.2.1. APF_VDELAYCNT (0x0170).........................................................................................................................................89

5.5.2.2. APF_VC_CONFIG (0x0178) .........................................................................................................................................89

5.5.2.3. DSITX_MODE (0x017C) ...............................................................................................................................................90

5.5.2.4. DSI_HSYNC_WIDTH (0x018C) ....................................................................................................................................91

5.5.2.5. DSI_HBPR (0x0190) .....................................................................................................................................................91

5.5.3. RX Event Registers ....................................................................................................................................................92

5.5.3.1. DSI_RX_STATE_INT_STAT (0x01A0)..........................................................................................................................92

5.5.3.2. DSI_RX_STATE_INT_MASK (0x01A4).........................................................................................................................93

5.5.3.3. DSI_RXTRIG_INT_STAT (0x01A8)...............................................................................................................................94

5.5.3.4. DSI_RXTRIG_INT_MASK (0x01AC).............................................................................................................................95

5.5.3.5. DSITX_INTERNAL_STAT (0x01B0)..............................................................................................................................96

5.5.3.6. DSI_ACKERROR (0x01B4)...........................................................................................................................................97

5.5.3.7. DSI_RXFIFO (0x01B8)..................................................................................................................................................97

5.5.3.8. DSI_RX_HEADER (0x01BC) ........................................................................................................................................98

5.5.3.9. DSI_LPRX_THRESH_COUNT (0x01C0) ......................................................................................................................98

5.5.3.10. DSI_LPRX_FIFO_LEVEL (0x01C4) ............................................................................................................................99

5.5.4. Error Experience Registers ......................................................................................................................................100

5.5.4.1. DSI_PRTO_INT_STAT (0x0208) ................................................................................................................................100

5.5.4.2. DSI_PRTO_INT_MASK (0x020C)...............................................................................................................................100

5.5.4.3. APP_SIDE_ERR_INT_STAT (0x0210) .......................................................................................................................101

5.5.4.4. APP_SIDE_ERR_INT_MASK (0x0214) ......................................................................................................................102

5.5.4.5. DSI_RX_ERR_INT_STAT (0x0218)............................................................................................................................103

5.5.4.6. DSI_RX_ERR_INT_MASK (0x021C) ..........................................................................................................................104

5.5.5. DSI LPTX Registers .................................................................................................................................................105

5.5.5.1. DSI_LPTX_INT_STAT (0x0220) .................................................................................................................................105

5.5.5.2. DSI_LPTX_INT_MASK (0x0224) ................................................................................................................................106

TC358870XBG

6 2015-02-02

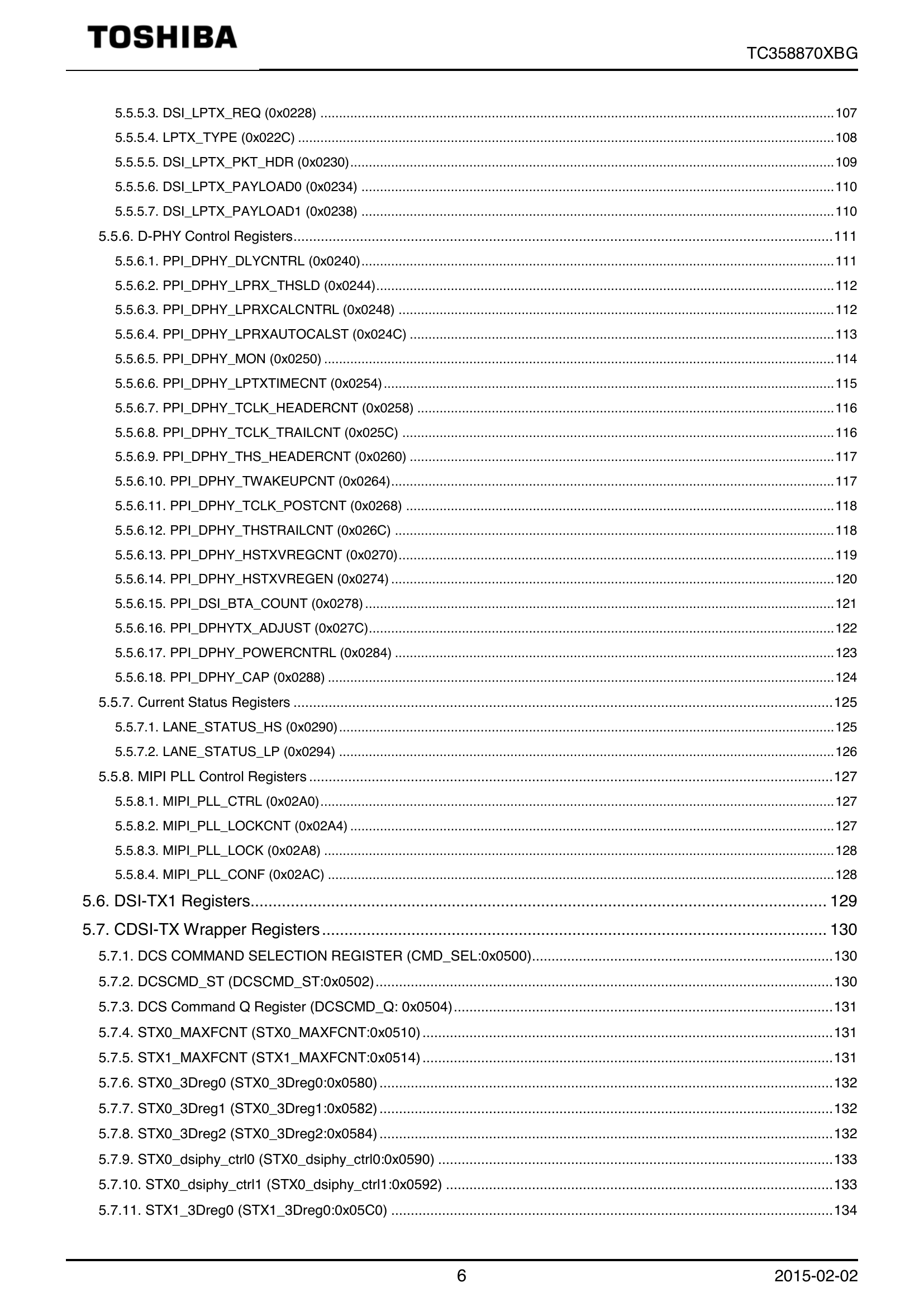

5.5.5.3. DSI_LPTX_REQ (0x0228) ..........................................................................................................................................107

5.5.5.4. LPTX_TYPE (0x022C) ................................................................................................................................................108

5.5.5.5. DSI_LPTX_PKT_HDR (0x0230)..................................................................................................................................109

5.5.5.6. DSI_LPTX_PAYLOAD0 (0x0234) ...............................................................................................................................110

5.5.5.7. DSI_LPTX_PAYLOAD1 (0x0238) ...............................................................................................................................110

5.5.6. D-PHY Control Registers..........................................................................................................................................111

5.5.6.1. PPI_DPHY_DLYCNTRL (0x0240)...............................................................................................................................111

5.5.6.2. PPI_DPHY_LPRX_THSLD (0x0244)...........................................................................................................................112

5.5.6.3. PPI_DPHY_LPRXCALCNTRL (0x0248) .....................................................................................................................112

5.5.6.4. PPI_DPHY_LPRXAUTOCALST (0x024C) ..................................................................................................................113

5.5.6.5. PPI_DPHY_MON (0x0250) .........................................................................................................................................114

5.5.6.6. PPI_DPHY_LPTXTIMECNT (0x0254).........................................................................................................................115

5.5.6.7. PPI_DPHY_TCLK_HEADERCNT (0x0258) ................................................................................................................116

5.5.6.8. PPI_DPHY_TCLK_TRAILCNT (0x025C) ....................................................................................................................116

5.5.6.9. PPI_DPHY_THS_HEADERCNT (0x0260) ..................................................................................................................117

5.5.6.10. PPI_DPHY_TWAKEUPCNT (0x0264).......................................................................................................................117

5.5.6.11. PPI_DPHY_TCLK_POSTCNT (0x0268) ...................................................................................................................118

5.5.6.12. PPI_DPHY_THSTRAILCNT (0x026C) ......................................................................................................................118

5.5.6.13. PPI_DPHY_HSTXVREGCNT (0x0270).....................................................................................................................119

5.5.6.14. PPI_DPHY_HSTXVREGEN (0x0274).......................................................................................................................120

5.5.6.15. PPI_DSI_BTA_COUNT (0x0278)..............................................................................................................................121

5.5.6.16. PPI_DPHYTX_ADJUST (0x027C).............................................................................................................................122

5.5.6.17. PPI_DPHY_POWERCNTRL (0x0284) ......................................................................................................................123

5.5.6.18. PPI_DPHY_CAP (0x0288) ........................................................................................................................................124

5.5.7. Current Status Registers ..........................................................................................................................................125

5.5.7.1. LANE_STATUS_HS (0x0290).....................................................................................................................................125

5.5.7.2. LANE_STATUS_LP (0x0294) .....................................................................................................................................126

5.5.8. MIPI PLL Control Registers ......................................................................................................................................127

5.5.8.1. MIPI_PLL_CTRL (0x02A0)..........................................................................................................................................127

5.5.8.2. MIPI_PLL_LOCKCNT (0x02A4) ..................................................................................................................................127

5.5.8.3. MIPI_PLL_LOCK (0x02A8) .........................................................................................................................................128

5.5.8.4. MIPI_PLL_CONF (0x02AC) ........................................................................................................................................128

5.6. DSI-TX1 Registers................................................................................................................................. 129

5.7. CDSI-TX Wrapper Registers................................................................................................................. 130

5.7.1. DCS COMMAND SELECTION REGISTER (CMD_SEL:0x0500).............................................................................130

5.7.2. DCSCMD_ST (DCSCMD_ST:0x0502).....................................................................................................................130

5.7.3. DCS Command Q Register (DCSCMD_Q: 0x0504).................................................................................................131

5.7.4. STX0_MAXFCNT (STX0_MAXFCNT:0x0510).........................................................................................................131

5.7.5. STX1_MAXFCNT (STX1_MAXFCNT:0x0514).........................................................................................................131

5.7.6. STX0_3Dreg0 (STX0_3Dreg0:0x0580)....................................................................................................................132

5.7.7. STX0_3Dreg1 (STX0_3Dreg1:0x0582)....................................................................................................................132

5.7.8. STX0_3Dreg2 (STX0_3Dreg2:0x0584)....................................................................................................................132

5.7.9. STX0_dsiphy_ctrl0 (STX0_dsiphy_ctrl0:0x0590) .....................................................................................................133

5.7.10. STX0_dsiphy_ctrl1 (STX0_dsiphy_ctrl1:0x0592) ...................................................................................................133

5.7.11. STX1_3Dreg0 (STX1_3Dreg0:0x05C0) .................................................................................................................134

TC358870XBG

7 2015-02-02

5.7.12. STX1_3Dreg1 (STX1_3Dreg1:0x05C2) .................................................................................................................134

5.7.13. STX1_3Dreg2 (STX1_3Dreg2:0x05C4) .................................................................................................................134

5.7.14. STX1_dsiphy_ctrl0 (STX1_dsiphy_ctrl0:0x05D0)...................................................................................................135

5.7.15. STX1_dsiphy_ctrl1 (STX1_dsiphy_ctrl1:0x05D2)...................................................................................................135

5.8. CEC Control Registers .......................................................................................................................... 136

5.8.1. CEC Clock High Time Register 0 (CecHclk: 0x0028) ............................................................................................136

5.8.2. CEC Clock Low Time Register 0 (CecLclk: 0x002A) .............................................................................................136

5.8.3. CEC Enable Register (CECEN: 0x0600)..................................................................................................................136

5.8.4. CEC Logical Address Register (CECADD: 0x0604).................................................................................................137

5.8.5. CEC Reset Register (CECRST: 0x0608) .................................................................................................................137

5.8.6. CEC Receive Enable (CECREN: 0x060C) ...............................................................................................................138

5.8.7. CEC Receive Control Register 1 (CECRCTL1: 0x0614) ..........................................................................................138

5.8.8. CEC Receive Control Register 2 (CECRCTL2: 0x0618) ..........................................................................................140

5.8.9. CEC Receive Control Register 3 (CECRCTL3: 0x061C)..........................................................................................141

5.8.10. CEC Transmit Enable Register (CECTEN: 0x0620)...............................................................................................142

5.8.11. CEC Transmit Control Register (CECTCTL: 0x0628)..........................................................................................143

5.8.12. CEC Receive Interrupt Status Register (CECRSTAT: 0x062C) .............................................................................144

5.8.13. CEC Transmit Interrupt Status Register (CECTSTAT: 0x0630) .............................................................................144

5.8.14. CEC Receive Buffer Registers (01-16) (CECRBUF01-16: 0x0634-0x0670) ..........................................................145

5.8.15. CEC Transmit Buffer Registers (01-16) (CECTBUF01-16: 0x0674-0x06B0) .........................................................145

5.8.16. CEC Receive Byte Counter Register (CECRCTR: 0x06B4)...................................................................................145

5.8.17. CEC Interrupt Enable Register (CECIMSK: 0x06C0) .............................................................................................146

5.8.18. CEC Interrupt Clear Register (CECICLR: 0x06CC) .............................................................................................146

5.9. Splitter Control Registers ...................................................................................................................... 147

5.9.1. STX0_CTRL (STX0_CTRL:0x5000).........................................................................................................................147

5.9.2. STX0 Packet ID Register 1 (STX0_PacketID1: 0x5002) ..........................................................................................147

5.9.3. STX0_WC (STX0_WC:0x5008)................................................................................................................................147

5.9.4. STX0_DPX (STX0_DPX:0x500A) ............................................................................................................................148

5.9.5. STX0_FPX (STX0_FPX:0x500C).............................................................................................................................149

5.9.6. STX0_LPX (STX0_LPX:0x500E)..............................................................................................................................149

5.9.7. STX0_DRPX (STX0_DRPX:0x5010)........................................................................................................................150

5.9.8. STX0_DGPX (STX0_DGPX:0x5012) .......................................................................................................................150

5.9.9. STX1_CTRL (STX1_CTRL:0x5080).........................................................................................................................150

5.9.10. STX1 Packet ID Register 1 (STX1_PacketID1: 0x5082) ........................................................................................151

5.9.11. STX0_DBPX (STX0_DBPX:0x5014)......................................................................................................................151

5.9.12. STX1_WC (STX1_WC:0x5088)..............................................................................................................................151

5.9.13. STX1_DPX (STX1_DPX:0x508A) ..........................................................................................................................152

5.9.14. STX1_FPX (STX1_FPX:0x508C)...........................................................................................................................153

5.9.15. STX1_LPX (STX1_LPX:0x508E)............................................................................................................................153

5.9.16. STX1_DRPX (STX1_DRPX:0x5090)......................................................................................................................153

5.9.17. STX1_DGPX (STX1_DGPX:0x5092) .....................................................................................................................154

5.9.18. STX1_DBPX (STX1_DBPX:0x5094)......................................................................................................................154

5.10. Internal Color Bar Generator............................................................................................................... 155

5.10.1. Color Bar Control Register (CB_CTRL: 0x7000) ....................................................................................................155

TC358870XBG

8 2015-02-02

5.10.2. Color Bar HSW Register (CB_HSW: 0x7008) ........................................................................................................155

5.10.3. Color Bar VSW Register (CB_VSW: 0x700A) ........................................................................................................155

5.10.4. Color Bar H-Total Register (CB_HTotal: 0x700C) ..................................................................................................156

5.10.5. Color Bar V-Total Register (CB_VTotal: 0x700E)...................................................................................................156

5.10.6. Color Bar HActive Register (CB_HAct: 0x7010).....................................................................................................156

5.10.7. Color Bar VActive Register (CB_VAct: 0x7012) .....................................................................................................157

5.10.8. Color Bar HStart Register (CB_HStart: 0x7014).....................................................................................................157

5.10.9. Color Bar VStart Register (CB_VStart: 0x7016) .....................................................................................................157

5.11. HDMI Rx System Control .................................................................................................................... 158

5.11.1. PHY CONTROL REGISTER (PHY_CTL) (0x8410)................................................................................................158

5.11.2. PHY ENABLE REGISTER (PHY_ENB) (0x8413)...................................................................................................158

5.11.3. PHY RESET REGISTER (PHY_RSTX) (0x8414)...................................................................................................158

5.11.4. APLL CONTROL REGISTER (APLL_CTL) (0x84F0).............................................................................................159

5.11.5. DDC IO CONTROL REGISTER (DDCIO_CTL) (0x84F4) ......................................................................................159

5.11.6. INTERRUPT0 REGISTER (HDMI_INT0) (0x8500) ................................................................................................159

5.11.7. INTERRUPT1 REGISTER (HDMI_INT1) (0x8501) ................................................................................................160

5.11.8. SYSTEM INTERRUPT (SYS_INT) (0x8502)..........................................................................................................161

5.11.9. CLOCK INTERRUPT (CLK_INT) (0x8503).............................................................................................................162

5.11.10. PACKET INTERRUPT (PACKET_INT) (0x8504) .................................................................................................163

5.11.11. CBIT INTERRUPT (CBIT_INT) (0x8505) .............................................................................................................164

5.11.12. AUDIO Buffer INTERRUPT (AUDIO_INT) (0x8506).............................................................................................165

5.11.13. ERROR INTERRUPT (ERR_INT) (0x8507) .........................................................................................................166

5.11.14. HDCP INTERRUPT (HDCP_INT) (0x8508)..........................................................................................................167

5.11.15. GBD INTERRUPT (GBD_INT) (0x8509) ..............................................................................................................168

5.11.16. MISC INTERRUPT (MISC_INT) (0x850b)............................................................................................................169

5.11.17. SYS INTERRUPT MASK (SYS_INTM) (0x8512) .................................................................................................170

5.11.18. CLK INTERRUPT MASK (CLK_INTM) (0x8513)..................................................................................................171

5.11.19. PACKET INTERRUPT MASK (PACKET_INTM) (0x8514)...................................................................................172

5.11.20. CBIT INTERRUPT MASK (CBIT_INTM) (0x8515).............................................................................................173

5.11.21. AUDIO INTERRUPT MASK (AUDIO_INTM) (0x8516) ......................................................................................174

5.11.22. ERR INTERRUPT MASK (ERR_INTM) (0x8517).................................................................................................175

5.11.23. HDCP INTERRUPT MASK (HDCP_INTM) (0x8518) ...........................................................................................176

5.11.24. GBD INTERRUPT MASK (GBD_INTM) (0x8519) ................................................................................................177

5.11.25. MISC INTERRUPT MASK (MISC_INTM) (0x851b)..............................................................................................178

5.11.26. SYS STATUS (SYS_STATUS) (0x8520) .............................................................................................................179

5.11.27. VIDEO INPUT STATUS (VI_STATUS) (0x8521)..................................................................................................180

5.11.28. VIDEO INPUT STATUS1 (VI_STATUS1) (0x8522)..............................................................................................181

5.11.29. AUDIO STATUS0 (AU_STATUS0) (0x8523)........................................................................................................181

5.11.30. AUDIO STATUS1 (AU_STATUS1) (0x8524)........................................................................................................182

5.11.31. VIDEO INPUT STATUS2 (VI_STATUS2) (0x8525)..............................................................................................183

5.11.32. CLK STATUS (CLK_STATUS) (0x8526)..............................................................................................................184

5.11.33. VI STATUS3 (VI_STATUS3) (0x8528).................................................................................................................185

5.11.34. SYS FREQ0 Register (SYS_FREQ0) (0x8540).................................................................................................185

5.11.35. SYS FREQ1 Register (SYS_FREQ1) (0x8541).................................................................................................186

TC358870XBG

9 2015-02-02

5.11.36. DDC CONTROL (DDC_CTL) (0x8543) ................................................................................................................186

5.11.37. HPD Control Register (HPD_CTL) (0x8544)......................................................................................................187

5.11.38. INIT END REGISTER (INIT_END) (0x854A)........................................................................................................187

5.11.39. HDCP MODE Register (HDCP_MODE) (0x8560) .............................................................................................188

5.11.40. HDCP COMMAND Register (HDCP_CMD) (0x8561) ..........................................................................................188

5.11.41. VIDEO MUTE REGISTER1 (V_MUTE1) (0x857A)............................................................................................189

5.11.42. VIDEO MUTE REGISTER2 (V_MUTE2) (0x857B)............................................................................................189

5.11.43. VIDEO MUTE Timer REGISTER1 (VMUTE_TIMER) (0x857C).........................................................................190

5.11.44. VIDEO MUTE STATUS REGISTER (VMUTE_STATUS) (0x857D)...................................................................190

5.11.45. VIDEO MUTE AUTO REGISTER2 (VMUTE_AUTO) (0x857F) .........................................................................191

5.11.46. Input DE Horizontal Start REGISTER (DE_STR) (0x8580)..................................................................................191

5.11.47. Input DE Horizontal Size REGISTER (DE_HSize) (0x8582) ................................................................................192

5.11.48. Input DE Vertical Start Position A REGISTER (DE_VStartA) (0x8584)................................................................192

5.11.49. Input DE Vertical Start Position B REGISTER (DE_VStartB) (0x8586)................................................................193

5.11.50. Input DE Vertical Start Position C REGISTER (DE_VStartC) (0x8588)................................................................193

5.11.51. Input DE Vertical Start Position D REGISTER (DE_VStartD) (0x858A) ...............................................................194

5.11.52. Input DE Vertical Size REGISTER (DE_VSize) (0x858C)....................................................................................194

5.11.53. Input Horizontal Size REGISTER (IN_HSize) (0x858E) .......................................................................................195

5.11.54. Input Vertical Size REGISTER (IN_VSize) (0x8590)............................................................................................195

5.11.55. Input HV Measurement Clear REGISTER (HV_CLR) (0x8593) ...........................................................................196

5.11.56. HV Status REGISTER (HV_STATUS) (0x85C5)..................................................................................................196

5.11.57. Vertical Range MIN REGISTER (FV_MIN) (0x85C6)...........................................................................................197

5.11.58. Vertical Range MAX REGISTER (FV_MAX) (0x85C8).........................................................................................197

5.11.59. Horizontal Range MIN REGISTER (FH_MIN) (0x85CA) ......................................................................................198

5.11.60. Horizontal Range MAX REGISTER (FH_MAX) (0x85CC)....................................................................................199

5.11.61. EDID MODE REGISTER (EDID_MODE) (0x85E0).........................................................................................200

5.11.62. EDID Length REGISTER 1 (EDID_LEN1) (0x85E3)..........................................................................................201

5.11.63. EDID Length REGISTER 2 (EDID_LEN2) (0x85E4) ............................................................................................201

5.12. HDMI Rx Audio Control ....................................................................................................................... 202

5.12.1. FORCE MUTE (FORCE_MUTE) (0x8600).............................................................................................................202

5.12.2. CMD AUD (CMD_AUD) (0x8601)...........................................................................................................................202

5.12.3. AUDIO AUTO MUTE Command REGISTER (AMute_Auto) (0x8602) ...................................................................203

5.12.4. Auto Command REGISTER 0 (AUTO_CMD1) (0x8603)........................................................................................203

5.12.5. Auto Command REGISTER 0 (AUTO_CMD2) (0x8604)........................................................................................204

5.12.6. Buffer Initialization Start Period (BUFINIT_START) (0x8606) ................................................................................204

5.12.7. FS MUTE REGISTER (FS_MUTE) (0x8607) .........................................................................................................205

5.12.8. AUDIO MUTE MODE REGISTER (MUTE_MODE) (0x8608).................................................................................206

5.12.9. AUDIO LAYOUT MONITOR REGISTER (LAYOUT_MONI) (0x861A) ...................................................................207

5.12.10. AUDIO SAMPLE FREQUENCY MODE REGISTER (FS_SET) (0x8621) ............................................................208

5.12.11. CBIT Byte 0 (CBIT_BYTE0) (0x8622) ..................................................................................................................208

5.12.12. CBIT Byte 1 (CBIT_BYTE1) (0x8623) ..................................................................................................................209

5.12.13. CBIT Byte 2 (CBIT_BYTE2) (0x8624) ..................................................................................................................209

5.12.14. CBIT Byte 3 (CBIT_BYTE3) (0x8625) ..................................................................................................................209

5.12.15. CBIT Byte 4 (CBIT_BYTE4) (0x8626) ..................................................................................................................210

TC358870XBG

10 2015-02-02

5.12.16. CBIT Byte 5 (CBIT_BYTE5) (0x8627) ..................................................................................................................210

5.12.17. Audio Sample Counter Register 0 (Audio_Counter0) (0x862E)............................................................................210

5.12.18. Audio Sample Counter Register 1 (Audio_Counter1) (0x862F)............................................................................211

5.12.19. Audio System Frequency Register A (LOCK_REF_FREQA-C) (0x8630) ............................................................211

5.12.20. Audio System Frequency Register A (LOCK_REF_FREQA-C) (0x8631) ............................................................211

5.12.21. Audio System Frequency Register A (LOCK_REF_FREQA-C) (0x8632) ............................................................211

5.12.22. AUDIO OUTPUT MODE 0 Register (SDO_MODE0) (0x8651).............................................................................212

5.12.23. AUDIO OUTPUT MODE 1 Register (SDO_MODE1) (0x8652).............................................................................213

5.12.24. AUDIO PLL Setting Register (NCO_F0_MOD) (0x8670) .....................................................................................213

5.12.25. AUDIO PLL Setting Register (NCO_48F0A) (0x8671) .........................................................................................214

5.12.26. AUDIO PLL Setting Register (NCO_48F0B) (0x8672) .........................................................................................214

5.12.27. AUDIO PLL Setting Register (NCO_48F0C) (0x8673) .........................................................................................214

5.12.28. AUDIO PLL Setting Register (NCO_48F0D) (0x8674) .........................................................................................214

5.12.29. AUDIO PLL Setting Register (NCO_44F0A) (0x8675) .........................................................................................215

5.12.30. AUDIO PLL Setting Register (NCO_44F0B) (0x8676) .........................................................................................215

5.12.31. AUDIO PLL Setting Register (NCO_44F0C) (0x8677) .........................................................................................215

5.12.32. AUDIO PLL Setting Register (NCO_44F0D) (0x8678) .........................................................................................215

5.12.33. Audio Mode Register (Aud_mode) (0x8680) ........................................................................................................216

5.12.34. Audio Pin Control 0 REGISTER (AOUTSEL0) (0x8690) ......................................................................................217

5.12.35. Audio Pin Control 1 REGISTER (AOUTSEL1) (0x8691) ......................................................................................217

5.13. HDMI Rx InfoFrame Data.................................................................................................................... 218

5.13.1. Clear InfoFrame Packet Register (CLR_INFO) (0x8700) .......................................................................................218

5.13.2. VS INFO PACKET TYPE CODE SETTING (TYP_VS_SET) (0x8701)...................................................................218

5.13.3. AVI INFO PACKET TYPE CODE SETTING (TYP_AVI_SET) (0x8702).................................................................219

5.13.4. SPD INFO PACKET TYPE CODE SETTING (TYP_SPD_SET) (0x8703) .............................................................219

5.13.5. AUD INFO PACKET TYPE CODE SETTING (TYP_AUD_SET) (0x8704).............................................................219

5.13.6. MS INFO PACKET TYPE CODE SETTING (TYP_MS_SET) (0x8705) .................................................................220

5.13.7. ACP INFO PACKET TYPE CODE SETTING (TYP_ACP_SET) (0x8706) .............................................................220

5.13.8. ISRC1 INFO PACKET TYPE CODE SET. (TYP_ISRC1_SET) (0x8707)...............................................................220

5.13.9. ISRC2 INFO PACKET TYPE CODE SETTING (TYP_ISRC2_SET) (0X8708) ......................................................221

5.13.10. PACKET AUTO CLEAR (PK_AUTO_CLR) (0x870A)...........................................................................................221

5.13.11. NO PACKET LIMIT (NO_PK_LIMIT) (0x870B).....................................................................................................222

5.13.12. NO PACKET CLEAR (NO_PK _CLR) (0x870C)...................................................................................................222

5.13.13. ERROR PACKET LIMIT (ERR_PK_LIMIT) (0x870D)...........................................................................................223

5.13.14. NO PACKET LIMIT (NO_PK_LIMIT2) (0x870E)...................................................................................................223

5.13.15. AVI INFO PACKET HEADER BYTE 0 (PK_AVI_0HEAD) (0x8710).....................................................................224

5.13.16. AVI INFO PACKET HEADER BYTE 1 (PK_AVI_1HEAD) (0x8711).....................................................................224

5.13.17. AVI INFO PACKET HEADER BYTE 2 (PK_AVI_2HEAD) (0x8712).....................................................................225

5.13.18. AVI INFO PACKET DATA BYTE 0 (PK_AVI_0BYTE) (0x8713)...........................................................................225

5.13.19. AVI INFO PACKET DATA BYTE 1 (PK_AVI_1BYTE) (0x8714)...........................................................................225

5.13.20. AVI INFO PACKET DATA BYTE 2 (PK_AVI_2BYTE) (0x8715)...........................................................................226

5.13.21. AVI INFO PACKET DATA BYTE 3 (PK_AVI_3BYTE) (0x8716)...........................................................................226

5.13.22. AVI INFO PACKET DATA BYTE 4 (PK_AVI_4BYTE) (0x8717)...........................................................................226

5.13.23. AVI INFO PACKET DATA BYTE 5 (PK_AVI_5BYTE) (0x8718)...........................................................................227

TC358870XBG

11 2015-02-02

5.13.24. AVI INFO PACKET DATA BYTE 6 (PK_AVI_6BYTE) (0x8719)...........................................................................227

5.13.25. AVI INFO PACKET DATA BYTE 7 (PK_AVI_7BYTE) (0x871a)...........................................................................227

5.13.26. AVI INFO PACKET DATA BYTE 8 (PK_AVI_8BYTE) (0x871b)...........................................................................228

5.13.27. AVI INFO PACKET DATA BYTE 9 (PK_AVI_9BYTE) (0x871c)...........................................................................228

5.13.28. AVI INFO PACKET DATA BYTE 10 (PK_AVI_10BYTE) (0x871d).......................................................................228

5.13.29. AVI INFO PACKET DATA BYTE 11 (PK_AVI_11BYTE) (0x871e).......................................................................229

5.13.30. AVI INFO PACKET DATA BYTE 12 (PK_AVI_12BYTE) (0x871f)........................................................................229

5.13.31. AVI INFO PACKET DATA BYTE 13 (PK_AVI_13BYTE) (0x8720).......................................................................229

5.13.32. AVI INFO PACKET DATA BYTE 14 (PK_AVI_14BYTE) (0x8721).......................................................................230

5.13.33. AVI INFO PACKET DATA BYTE 15 (PK_AVI_15BYTE) (0x8722).......................................................................230

5.13.34. AVI INFO PACKET DATA BYTE 16 (PK_AVI_16BYTE) (0x8723).......................................................................230

5.13.35. AUD INFO PACKET HEADER BYTE 0 (PK_AUD_0HEAD) (0x8730) .................................................................231

5.13.36. AUD INFO PACKET HEADER BYTE 1 (PK_AUD_1HEAD) (0x8731) .................................................................231

5.13.37. AUD INFO PACKET HEADER BYTE 2 (PK_AUD_2HEAD) (0x8732) .................................................................231

5.13.38. AUD INFO PACKET DATA BYTE 0 (PK_AUD_0BYTE) (0x8733) .......................................................................232

5.13.39. AUD INFO PACKET DATA BYTE 1 (PK_AUD_1BYTE) (0x8734) .......................................................................232

5.13.40. AUD INFO PACKET DATA BYTE 2 (PK_AUD_2BYTE) (0x8735) .......................................................................232

5.13.41. AUD INFO PACKET DATA BYTE 3 (PK_AUD_3BYTE) (0x8736) .......................................................................233

5.13.42. AUD INFO PACKET DATA BYTE 4 (PK_AUD_4BYTE) (0x8737) .......................................................................233

5.13.43. AUD INFO PACKET DATA BYTE 5 (PK_AUD_5BYTE) (0x8738) .......................................................................233

5.13.44. AUD INFO PACKET DATA BYTE 6 (PK_AUD_6BYTE) (0x8739) .......................................................................234

5.13.45. AUD INFO PACKET DATA BYTE 7 (PK_AUD_7BYTE) (0x873a) .......................................................................234

5.13.46. AUD INFO PACKET DATA BYTE 8 (PK_AUD_8BYTE) (0x873b) .......................................................................234

5.13.47. AUD INFO PACKET DATA BYTE 9 (PK_AUD_9BYTE) (0x873c) .......................................................................235

5.13.48. AUD INFO PACKET DATA BYTE 10 (PK_AUD_10BYTE) (0x873d) ...................................................................235

5.13.49. MS INFO PACKET HEADER BYTE 0 (PK_MS_0HEAD) (0x8740)......................................................................235

5.13.50. MS INFO PACKET HEADER BYTE 1 (PK_MS_1HEAD) (0x8741)......................................................................236

5.13.51. MS INFO PACKET HEADER BYTE 2 (PK_MS_2HEAD) (0x8742)......................................................................236

5.13.52. MS INFO PACKET DATA BYTE 0 (PK_MS_0BYTE) (0x8743)............................................................................236

5.13.53. MS INFO PACKET DATA BYTE 1 (PK_MS_1BYTE) (0x8744)............................................................................237

5.13.54. MS INFO PACKET DATA BYTE 2 (PK_MS_2BYTE) (0x8745)............................................................................237

5.13.55. MS INFO PACKET DATA BYTE 3 (PK_MS_3BYTE) (0x8746)............................................................................237

5.13.56. MS INFO PACKET DATA BYTE 4 (PK_MS_4BYTE) (0x8747)............................................................................238

5.13.57. MS INFO PACKET DATA BYTE 5 (PK_MS_5BYTE) (0x8748)............................................................................238

5.13.58. MS INFO PACKET DATA BYTE 6 (PK_MS_6BYTE) (0x8749)............................................................................238

5.13.59. MS INFO PACKET DATA BYTE 7 (PK_MS_7BYTE) (0x874a)............................................................................239

5.13.60. MS INFO PACKET DATA BYTE 8 (PK_MS_8BYTE) (0x874b)............................................................................239

5.13.61. MS INFO PACKET DATA BYTE 9 (PK_MS_9BYTE) (0x874c)............................................................................239

5.13.62. MS INFO PACKET DATA BYTE 10 (PK_MS_10BYTE) (0x874d)........................................................................240

5.13.63. SPD INFO PACKET HEADER BYTE 0 (PK_SPD_0HEAD) (0x8750)..................................................................240

5.13.64. SPD INFO PACKET HEADER BYTE 1 (PK_SPD_1HEAD) (0x8751)..................................................................240

5.13.65. SPD INFO PACKET HEADER BYTE 2 (PK_SPD_2HEAD) (0x8752)..................................................................241

5.13.66. SPD INFO PACKET DATA BYTE 0 (PK_SPD_0BYTE) (0x8753)........................................................................241

5.13.67. SPD INFO PACKET DATA BYTE 1 (PK_SPD_1BYTE) (0x8754)........................................................................241

5.13.68. SPD INFO PACKET DATA BYTE 2 (PK_SPD_2BYTE) (0x8755)........................................................................242

TC358870XBG

12 2015-02-02

5.13.69. SPD INFO PACKET DATA BYTE 3 (PK_SPD_3BYTE) (0x8756)........................................................................242

5.13.70. SPD INFO PACKET DATA BYTE 4 (PK_SPD_4BYTE) (0x8757)........................................................................242

5.13.71. SPD INFO PACKET DATA BYTE 5 (PK_SPD_5BYTE) (0x8758)........................................................................243

5.13.72. SPD INFO PACKET DATA BYTE 6 (PK_SPD_6BYTE) (0x8759)........................................................................243

5.13.73. SPD INFO PACKET DATA BYTE 7 (PK_SPD_7BYTE) (0x875a)........................................................................243

5.13.74. SPD INFO PACKET DATA BYTE 8 (PK_SPD_8BYTE) (0x875b)........................................................................244

5.13.75. SPD INFO PACKET DATA BYTE 9 (PK_SPD_9BYTE) (0x875c)........................................................................244

5.13.76. SPD INFO PACKET DATA BYTE 10 (PK_SPD_10BYTE) (0x875d)....................................................................244

5.13.77. SPD INFO PACKET DATA BYTE 11 (PK_SPD_11BYTE) (0x875e)....................................................................245

5.13.78. SPD INFO PACKET DATA BYTE 12 (PK_SPD_12BYTE) (0x875f).....................................................................245

5.13.79. SPD INFO PACKET DATA BYTE 13 (PK_SPD_13BYTE) (0x8760)....................................................................245

5.13.80. SPD INFO PACKET DATA BYTE 14 (PK_SPD_14BYTE) (0x8761)....................................................................246

5.13.81. SPD INFO PACKET DATA BYTE 15 (PK_SPD_15BYTE) (0x8762)....................................................................246

5.13.82. SPD INFO PACKET DATA BYTE 16 (PK_SPD_16BYTE) (0x8763)....................................................................246

5.13.83. SPD INFO PACKET DATA BYTE 17 (PK_SPD_17BYTE) (0x8764)....................................................................247

5.13.84. SPD INFO PACKET DATA BYTE 18 (PK_SPD_18BYTE) (0x8765)....................................................................247

5.13.85. SPD INFO PACKET DATA BYTE 19 (PK_SPD_19BYTE) (0x8766)....................................................................247

5.13.86. SPD INFO PACKET DATA BYTE 20 (PK_SPD_20BYTE) (0x8767)....................................................................248

5.13.87. SPD INFO PACKET DATA BYTE 21 (PK_SPD_21BYTE) (0x8768)....................................................................248

5.13.88. SPD INFO PACKET DATA BYTE 22 (PK_SPD_22BYTE) (0x8769)....................................................................248

5.13.89. SPD INFO PACKET DATA BYTE 23 (PK_SPD_23BYTE) (0x876a)....................................................................249

5.13.90. SPD INFO PACKET DATA BYTE 24 (PK_SPD_24BYTE) (0x876b)....................................................................249

5.13.91. SPD INFO PACKET DATA BYTE 25 (PK_SPD_25BYTE) (0x876c)....................................................................249

5.13.92. SPD INFO PACKET DATA BYTE 26 (PK_SPD_26BYTE) (0x876d)....................................................................250

5.13.93. SPD INFO PACKET DATA BYTE 27 (PK_SPD_27BYTE) (0x876e)....................................................................250

5.13.94. VS INFO PACKET HEADER BYTE 0 (PK_VS_0HEAD) (0x8770).......................................................................250

5.13.95. VS INFO PACKET HEADER BYTE 1 (PK_VS_1HEAD) (0x8771).......................................................................251

5.13.96. VS INFO PACKET HEADER BYTE 2 (PK_VS_2HEAD) (0x8772).......................................................................251

5.13.97. VS INFO PACKET DATA BYTE 0 (PK_VS_0BYTE) (0x8773).............................................................................251

5.13.98. VS INFO PACKET DATA BYTE 1 (PK_VS_1BYTE) (0x8774).............................................................................252

5.13.99. VS INFO PACKET DATA BYTE 2 (PK_VS_2BYTE) (0x8775).............................................................................252

5.13.100. VS INFO PACKET DATA BYTE 3 (PK_VS_3BYTE) (0x8776)...........................................................................252

5.13.101. VS INFO PACKET DATA BYTE 4 (PK_VS_4BYTE) (0x8777)...........................................................................253

5.13.102. VS INFO PACKET DATA BYTE 5 (PK_VS_5BYTE) (0x8778)...........................................................................253

5.13.103. VS INFO PACKET DATA BYTE 6 (PK_VS_6BYTE) (0x8779)...........................................................................253

5.13.104. VS INFO PACKET DATA BYTE 7 (PK_VS_7BYTE) (0x877a)...........................................................................254

5.13.105. VS INFO PACKET DATA BYTE 8 (PK_VS_8BYTE) (0x877b)...........................................................................254

5.13.106. VS INFO PACKET DATA BYTE 9 (PK_VS_9BYTE) (0x877c)...........................................................................254

5.13.107. VS INFO PACKET DATA BYTE 10 (PK_VS_10BYTE) (0x877d).......................................................................255

5.13.108. VS INFO PACKET DATA BYTE 11 (PK_VS_11BYTE) (0x877e).......................................................................255

5.13.109. VS INFO PACKET DATA BYTE 12 (PK_VS_12BYTE) (0x877f)........................................................................255

5.13.110. VS INFO PACKET DATA BYTE 13 (PK_VS_13BYTE) (0x8780).......................................................................256

5.13.111. VS INFO PACKET DATA BYTE 14 (PK_VS_14BYTE) (0x8781).......................................................................256

5.13.112. VS INFO PACKET DATA BYTE 15 (PK_VS_15BYTE) (0x8782).......................................................................256

5.13.113. VS INFO PACKET DATA BYTE 16 (PK_VS_16BYTE) (0x8783).......................................................................257

TC358870XBG

13 2015-02-02

5.13.114. VS INFO PACKET DATA BYTE 17 (PK_VS_17BYTE) (0x8784).......................................................................257

5.13.115. VS INFO PACKET DATA BYTE 18 (PK_VS_18BYTE) (0x8785).......................................................................257

5.13.116. VS INFO PACKET DATA BYTE 19 (PK_VS_19BYTE) (0x8786).......................................................................258

5.13.117. VS INFO PACKET DATA BYTE 20 (PK_VS_20BYTE) (0x8787).......................................................................258

5.13.118. VS INFO PACKET DATA BYTE 21 (PK_VS_21BYTE) (0x8788).......................................................................258

5.13.119. VS INFO PACKET DATA BYTE 22 (PK_VS_22BYTE) (0x8789).......................................................................259

5.13.120. VS INFO PACKET DATA BYTE 23 (PK_VS_23BYTE) (0x878a).......................................................................259

5.13.121. VS INFO PACKET DATA BYTE 24 (PK_VS_24BYTE) (0x878b).......................................................................259

5.13.122. VS INFO PACKET DATA BYTE 25 (PK_VS_25BYTE) (0x878c).......................................................................260

5.13.123. VS INFO PACKET DATA BYTE 26 (PK_VS_26BYTE) (0x878d).......................................................................260

5.13.124. VS INFO PACKET DATA BYTE 27 (PK_VS_27BYTE) (0x878e).......................................................................260

5.13.125. ACP INFO PACKET HEADER BYTE 0 (PK_ACP_0HEAD) (0x8790)................................................................261

5.13.126. ACP INFO PACKET HEADER BYTE 1 (PK_ACP_1HEAD) (0x8791)................................................................261

5.13.127. ACP INFO PACKET HEADER BYTE 2 (PK_ACP_2HEAD) (0x8792)................................................................261

5.13.128. ACP INFO PACKET DATA BYTE 0 (PK_ACP_0BYTE) (0x8793)......................................................................262

5.13.129. ACP INFO PACKET DATA BYTE 1 (PK_ACP_1BYTE) (0x8794)......................................................................262

5.13.130. ACP INFO PACKET DATA BYTE 2 (PK_ACP_2BYTE) (0x8795)......................................................................262

5.13.131. ACP INFO PACKET DATA BYTE 3 (PK_ACP_3BYTE) (0x8796)......................................................................263

5.13.132. ACP INFO PACKET DATA BYTE 4 (PK_ACP_4BYTE) (0x8797)......................................................................263

5.13.133. ACP INFO PACKET DATA BYTE 5 (PK_ACP_5BYTE) (0x8798)......................................................................263

5.13.134. ACP INFO PACKET DATA BYTE 6 (PK_ACP_6BYTE) (0x8799)......................................................................264

5.13.135. ACP INFO PACKET DATA BYTE 7 (PK_ACP_7BYTE) (0x879a)......................................................................264

5.13.136. ACP INFO PACKET DATA BYTE 8 (PK_ACP_8BYTE) (0x879b)......................................................................264

5.13.137. ACP INFO PACKET DATA BYTE 9 (PK_ACP_9BYTE) (0x879c)......................................................................265

5.13.138. ACP INFO PACKET DATA BYTE 10 (PK_ACP_10BYTE) (0x879d)..................................................................265

5.13.139. ACP INFO PACKET DATA BYTE 11 (PK_ACP_11BYTE) (0x879e)..................................................................265

5.13.140. ACP INFO PACKET DATA BYTE 12 (PK_ACP_12BYTE) (0x879f)...................................................................266

5.13.141. ACP INFO PACKET DATA BYTE 13 (PK_ACP_13BYTE) (0x87a0)..................................................................266

5.13.142. ACP INFO PACKET DATA BYTE 14 (PK_ACP_14BYTE) (0x87a1)..................................................................266

5.13.143. ACP INFO PACKET DATA BYTE 15 (PK_ACP_15BYTE) (0x87a2)..................................................................267

5.13.144. ACP INFO PACKET DATA BYTE 16 (PK_ACP_16BYTE) (0x87a3)..................................................................267

5.13.145. ACP INFO PACKET DATA BYTE 17 (PK_ACP_17BYTE) (0x87a4)..................................................................267

5.13.146. ACP INFO PACKET DATA BYTE 18 (PK_ACP_18BYTE) (0x87a5)..................................................................268

5.13.147. ACP INFO PACKET DATA BYTE 19 (PK_ACP_19BYTE) (0x87a6)..................................................................268

5.13.148. ACP INFO PACKET DATA BYTE 20 (PK_ACP_20BYTE) (0x87a7)..................................................................268

5.13.149. ACP INFO PACKET DATA BYTE 21 (PK_ACP_21BYTE) (0x87a8)..................................................................269

5.13.150. ACP INFO PACKET DATA BYTE 22 (PK_ACP_22BYTE) (0x87a9)..................................................................269

5.13.151. ACP INFO PACKET DATA BYTE 23 (PK_ACP_23BYTE) (0x87aa)..................................................................269

5.13.152. ACP INFO PACKET DATA BYTE 24 (PK_ACP_24BYTE) (0x87ab)..................................................................270

5.13.153. ACP INFO PACKET DATA BYTE 25 (PK_ACP_25BYTE) (0x87ac)..................................................................270

5.13.154. ACP INFO PACKET DATA BYTE 26 (PK_ACP_26BYTE) (0x87ad)..................................................................270

5.13.155. ACP INFO PACKET DATA BYTE 27 (PK_ACP_27BYTE) (0x87ae)..................................................................271

5.13.156. ISRC1 INFO PACKET HEADER BYTE 0 (PK_ISRC1_0HEAD) (0x87b0) .........................................................271

5.13.157. ISRC1 INFO PACKET HEADER BYTE 1 (PK_ISRC1_1HEAD) (0x87b1) .........................................................271

5.13.158. ISRC1 INFO PACKET HEADER BYTE 2 (PK_ISRC1_2HEAD) (0x87b2) .........................................................272

TC358870XBG

14 2015-02-02

5.13.159. ISRC1 INFO PACKET DATA BYTE 0 (PK_ISRC1_0BYTE) (0x87b3) ...............................................................272

5.13.160. ISRC1 INFO PACKET DATA BYTE 1 (PK_ISRC1_1BYTE) (0x87b4) ...............................................................272

5.13.161. ISRC1 INFO PACKET DATA BYTE 2 (PK_ISRC1_2BYTE) (0x87b5) ...............................................................273

5.13.162. ISRC1 INFO PACKET DATA BYTE 3 (PK_ISRC1_3BYTE) (0x87b6) ...............................................................273

5.13.163. ISRC1 INFO PACKET DATA BYTE 4 (PK_ISRC1_4BYTE) (0x87b7) ...............................................................273

5.13.164. ISRC1 INFO PACKET DATA BYTE 5 (PK_ISRC1_5BYTE) (0x87b8) ...............................................................274

5.13.165. ISRC1 INFO PACKET DATA BYTE 6 (PK_ISRC1_6BYTE) (0x87b9) ...............................................................274

5.13.166. ISRC1 INFO PACKET DATA BYTE 7 (PK_ISRC1_7BYTE) (0x87ba) ...............................................................274

5.13.167. ISRC1 INFO PACKET DATA BYTE 8 (PK_ISRC1_8BYTE) (0x87bb) ...............................................................275

5.13.168. ISRC1 INFO PACKET DATA BYTE 9 (PK_ISRC1_9BYTE) (0x87bc) ...............................................................275

5.13.169. ISRC1 INFO PACKET DATA BYTE 10 (PK_ISRC1_10BYTE) (0x87bd) ...........................................................275

5.13.170. ISRC1 INFO PACKET DATA BYTE 11 (PK_ISRC1_11BYTE) (0x87be) ...........................................................276

5.13.171. ISRC1 INFO PACKET DATA BYTE 12 (PK_ISRC1_12BYTE) (0x87bf) ............................................................276

5.13.172. ISRC1 INFO PACKET DATA BYTE 13 (PK_ISRC1_13BYTE) (0x87c0) ...........................................................276

5.13.173. ISRC1 INFO PACKET DATA BYTE 14 (PK_ISRC1_14BYTE) (0x87c1) ...........................................................277

5.13.174. ISRC1 INFO PACKET DATA BYTE 15 (PK_ISRC1_15BYTE) (0x87c2) ...........................................................277

5.13.175. ISRC2 INFO PACKET HEADER BYTE 0 (PK_ISRC2_0HEAD) (0x87d0) .........................................................277

5.13.176. ISRC2 INFO PACKET HEADER BYTE 1 (PK_ISRC2_1HEAD) (0x87d1) .........................................................278

5.13.177. ISRC2 INFO PACKET HEADER BYTE 2 (PK_ISRC2_2HEAD) (0x87d2) .........................................................278

5.13.178. ISRC2 INFO PACKET DATA BYTE 0 (PK_ISRC2_0BYTE) (0x87d3) ...............................................................278

5.13.179. ISRC2 INFO PACKET DATA BYTE 1 (PK_ISRC2_1BYTE) (0x87d4) ...............................................................279