华为面试数字芯片提纲

1、 时序逻辑/ 组合逻辑

同步逻辑/ 异步逻辑

同步时钟/ 异步时钟

2、亚稳态的概念/ 可能出现的场合和抑制手段

3、异步 FIFO 原理/ FIFO 的深度计算/ 同步 FIFO/ 要求自己写异步 FIFO 代码/ 自己尝试添加约束

4、双端口 RAM 的实现/ 要求自己写双端口 RAM

5、两级触发器同步/ 应用场合/ MTBF 的计算以及 2-FF 的计算

6、握手机制

7、同步复位/ 异步复位/ 异步复位同步释放/ 三者比较/ 代码

8、恢复时间/ 去除时间/

9、触发器组成/ 锁存器组成/ 区别

10、脉冲检测电路(非同步时钟如何处理,快到慢,慢到快,同频,长脉冲化为单时钟短脉冲)

11、可综合和不可综合概念/ timescale 的理解

12、组合逻辑环路概念

13、静态时序分析 STA/ 动态时序分析/ 二者对比

14、建立时间/ 保持时间/ 数据到达时间/ 数据需求时间/ 建立时间裕量/ 保持时间裕量

15、四类时序路径及起点终点/ 完整的时序路径包含三部分/ 建立时间检查,保持时间检查/ 恢复时间检查,去除

时间检查/ 检查违例的解决方案

16、时序约束/ 时钟约束/ 输入输出约束/ 时序例外约束/ 多周期路径约束(Multicycle paths)/ 伪路径约束(False

paths)/ min-max 约束/ bus skew

17、竞争冒险/ 消除方法

18、状态机分类/ 状态转移图/ 一段两段三段式状态机区别特征(优缺点,本质特征,状态数差别,输出改变时间

差别,状态机也分为同步状态机(有 CLK 控制输出)和异步状态机)/ 思考具体的状态机实例(饮料售卖)

19、系统级/ 算法级/ RTL 级/ 门级/ 开关级

20、阻塞赋值/ 非阻塞赋值

21、function/ task/ repeat/ while/ for

22、详细研究对于运算数为 X/Z 以及逻辑运算中有 X/Z 的情况下结果分别如何/ reg 和 wire 缺省值/ 关系符 ===以

及 !==的具体用法/ 一元简约运算符用法/ 位运算数位不对齐的情况/ 算数运算操作数的位数对不齐的情况运算结

果以及被赋值的数位不够的情况/ 运算数存在有符号数的情况

23、Case /if 用法对比/ casez/ casex

24、Verilog 常见编码风格/ 串并转换/ 乒乓操作/ 流水线/ 面积速度互换/ 逻辑复用/ 流水线设计全加器,注意细

节,注意位宽匹配/ 流水线乘法器(用逻辑门)/ 超前进位加法器

25、奇数分频/ 偶数分频/ 小数分频/ N+0.5 分频/ PLL 原理

�

26、Verilog 仿真常用关键词和用法/ 常用原语

27、FPGA 内部资源以及结构/

FPGA 烧写模式/ FPGA 和 CPLD 比较

28、提高系统工作频率的方法/

29、验证的概念/ 形式验证/ 常用验证方法

30、CMOS 功耗类别/ 数字芯片设计低功耗方案

31、SPI/ I2C/ RS232/ RS485/ UART 常见协议以及电平标准/ 波特率/ 比特率

32、DDR/ SDRAM/ SRAM/ DRAM/ ROM 原理速度功耗价格容量等等比较

33、数字滤波器/ 模拟滤波器/ 传递函数/ 如何画数字滤波器框图

34、二进制数运算/ 定点数浮点数/ 源码反码补码/ 相关数据的运算

35、逻辑代数表达式/ 化简公式/ 最大项最小项/ 卡诺图化简/ 真值表/ 状态转移图

36、CMOS 与非门/ 或非门/ 反相器(优良特性)/ 三态门/ 线与逻辑/ 传输门/ MOS 工作原理

37、施密特触发器

38、AD/DA 基本原理和结构

39、Serdes 接口知识/ 预加重/ 去加重/ 均衡/ 常用编码方式/ 时钟数据恢复(CDR)原理,参考时钟作用/

�

华为面试数字芯片提纲解答以及要点备注

1、 时序逻辑/ 组合逻辑

时序逻辑电路主要由组合逻辑电路和触发器等记忆元件组成,输出不仅取决于当前输入,还和电路原来状态有

关(这里原来状态是指的中间的触发器等记忆元件部分的端口值也可能会影响到当前的电路总的输出);组合逻辑

电路主要由组合逻辑器件构成,电路无存储元件,输出仅仅取决于当前的输入。

同步逻辑/ 异步逻辑

同步逻辑是指的电路驱动时钟是有固定因果关系的逻辑,异步逻辑是电路驱动时钟之间没有固定因果关系的逻

辑。通常同步逻辑电路的驱动时钟来源于同一个时钟源产生的相同时钟或者相位差可预知的不同时钟,这里不包括

相位差在一定时钟周期内(例如 1000clk)依然无法确定公共周期的同源时钟;异步逻辑的电路驱动时钟来自不同

源时钟或者相位差关系不确定的时钟。

同步时钟/ 异步时钟

同步时钟指的是时钟源来自于同一个时钟源生成的时钟,其相位差可计算预知,这里不包括来自同一时钟源但

是在一定时钟周期内(例如 1000clk)依然无法确定公共周期的时钟,通常为由 PLL 生成的非整数分频或者倍频时钟。

异步时钟是指的相位差无法预测的时钟,通常来自于不同的时钟源。

2、亚稳态的概念/ 可能出现的场合和抑制手段

亚稳态是指触发器的建立时间或者保持时间不能满足时触发器的输出介于 0 或者 1 两者之间的某个不稳定态。

理想的触发器在时钟到来时刻采样数据,但现实之中时钟边沿通常具有一定斜率,因此数据需要在时钟到来的前后

各一段时间内保持稳定,使得触发器能够准确采样数据,否则就可能出现亚稳态。

亚稳态通常出现在同步时钟驱动电路的异步复位信号来临和消失的时候,或者是异步时钟域之间数据传递的时

候。前者解决方案是采用同步复位(通常会导致电路逻辑资源占用面积增加)/或者是异步复位同步释放方式避免

亚稳态;后者通常考虑用异步 FIFO,双端口 RAM,双触发器,或者是握手机制等方法进行同步。此外还有例如降频,

使用速度较快的触发器,改善时钟质量也会有一定效果。

3、异步 FIFO 原理/ FIFO 的深度计算/ 同步 FIFO/ 要求自己写异步 FIFO 代码/ 自己尝试添加约束

(H:\Desktop\Hardware_study\Async_FIFO)

异步 FIFO 主要用于实现异步时钟域之间的数据传输。异步 FIFO 由以下几部分构成。

BRAM/DRAM 组成的缓冲区。用于缓存数据流,其深度的设定需要根据输入输出数据的时钟差别以及最大

连续输入/输出数据量确定。

读写指针。其变化需要根据 FIFO 的空满状态以及当前的读写请求指令共同确定。当缓存为空则不可读,读

指针不变;当缓存为满不可写,写指针不变。

空满状态标志。由于异步 FIFO 工作在不同时钟域,因此对空满状态的判断依赖于不同时钟域的读指针和写

指针。为了便于区分“快一圈”的现象,可以考虑将指针位宽多设置一位,当最高位相同时候,读指针等于写

�

指针认为是读空,当最高位不同的时候,读指针等于写指针认为是写满;

同步电路。由于两者读写指针比较是在不同时钟域下进行,因此为了避免亚稳态需要进行同步设计。此处

通常采用格雷码进行比较(传输端首先 BIN TO GRAY,经过两级触发器在目的端同步,然后 GRAY TO BIN,进行

下一步的比较,得出空满状态),保证一次只有一位数据变化,利用格雷码结合两级触发器进行同步后,可以

严格保证至少数据不会出错(起码是原地踏步,不会造成满状态写入的情况),中间加的两级触发器会对实际

状态做延迟比较(避免了空读和满写),也属于保守预估,最多是不是真空/真满情况下告知空满,但是不会

导致数据出错,属于保守的方法。

FIFO 深度计算,计算主要考虑最坏的情况,例如 100wclk 里面进来 80 个这种,需要考虑 200 个时钟内连

续进来 160 个的情况,然后计算深度也是根据“平均进来一个出去几个,然后乘以最大连续量即可得到 FIFO

深度”这样的方式考虑最大深度。

同步 FIFO 由于驱动时钟同步,因此可省去中间同步器以及格雷码编码机制,其作用原理和异步 FIFO 类似。

4、双端口 RAM 的实现/ 要求自己写双端口 RAM(H:\Desktop\Hardware_study\Async_Dual_port_ram)

FPGA 内部 RAM 资源分为 Block RAM 和 Distribute RAM,前者一般用于大量数据的缓存,后者多用于小部分数据

缓存。就速度而言由于 Distribute RAM 利用 FPGA 内部 Slicem 的 LUT 存储资源,少量存储的话速度比较快,但是大

量存储会对布线造成影响,难以保证时序。

FPGA 可以配置 Single-port-ram, Simple-port-ram, True-port-ram 等形式的 RAM,读写模式有 write-first, read-first,

no-change 等模式,write-first 表明输出端口的数据和写入的数据相同,read-first 表明输出端口的数据为当前地址之

前存储的数据,no-change 表明输出数据为写入之前一刻的数据不变;

Single-port-ram 同时只能进行读或写操作;True-port-ram 可同时进行读写操作,但是要避免地址冲突,不能两

个端口同时对一个地址写入,Simple-port-ram 实际上是 True-port-ram 只开启了 A 端口的写入和 B 端口的输出。

5、两级触发器同步/ 应用场合/ MTBF 的计算以及 2-FF 的计算

两级触发器通常用于异步时钟域之间的单比特信号传输,通常是控制信号。其抑制亚稳态传播的原理并不是避

免亚稳态的发生,也无法避免出错信号的继续传输,而是尽量减少亚稳态传播的概率。根据触发器 MTBF(平均故

障时间间隔)计算,一级触发器的 MTBF = (e^(tmet/c1) / c2*f*a) 两级触发器 MTBF = (MTBF1)*(MTBF2),相当于不稳

定态在第一级触发器后被阻断了传播。如果条件更苛刻可考虑三级触发器。

6、握手机制/ 代码(H:\Desktop\Hardware_study\Async_Dual_port_ram)

握手机制通常用于数据传输速率要求不高但要求准确的场合,两边的握手信号都需要各自时钟域的同步器进行

同步。当接收端经过同步电路接收到 req 信号后锁存总线数据,然后发出 ack 信号,ack 经过同步电路后到达发送端,

发送端接受后撤销 req 信号,接收端也撤销掉 ack 信号,一次握手完成。

�

7、同步复位/ 异步复位/ 异步复位同步释放/ 三者比较/ 代码

同步复位指的是时钟有效沿来临的时候进行复位操作,同步复位使得电路为同步电路,能够利于仿真,缺点是

要求复位信号要大于一个周期,否则无法保证成功复位,此外综合出来的电路实际上并没有利用器件的复位端,而

是在输入端插入额外的逻辑电路,这样增加了额外的逻辑资源消耗。

异步复位是指的在任何时候只要复位信号有效即可复位,不占用额外的逻辑资源,充分利用器件的复位引脚,

但是由于来临和结束时间未知,容易引起亚稳态现象。

对于 FPGA 的 Flip-Flop,一般有同步复位,置位引脚 RST/S 和异步复位,置位引脚 CLR/PRE,对于同步复位,需

要引入额外的 MUX 电路控制 RST/S,对资源有一定的占用。

比较理想的方式是异步复位同步释放,既充分利用了器件的复位引脚,又能够有效避免亚稳态的产生。

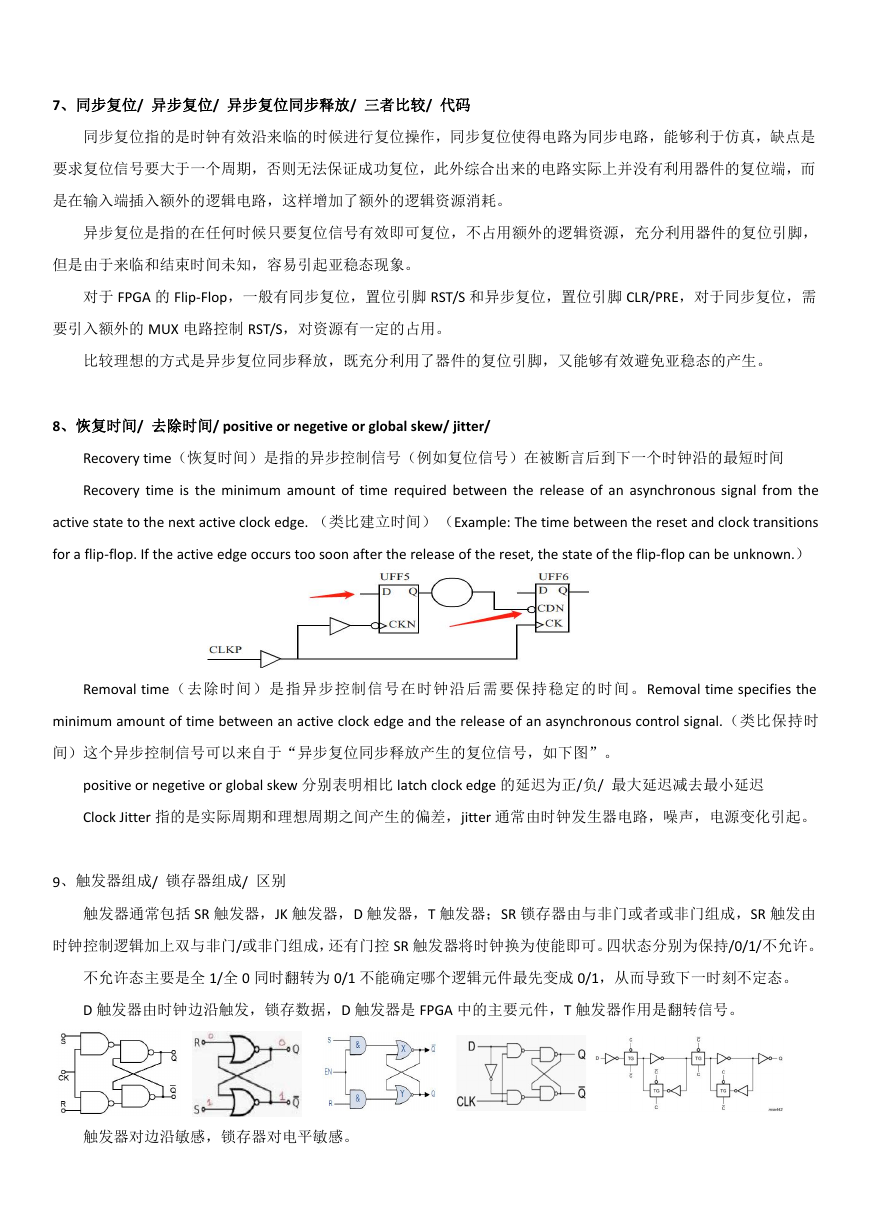

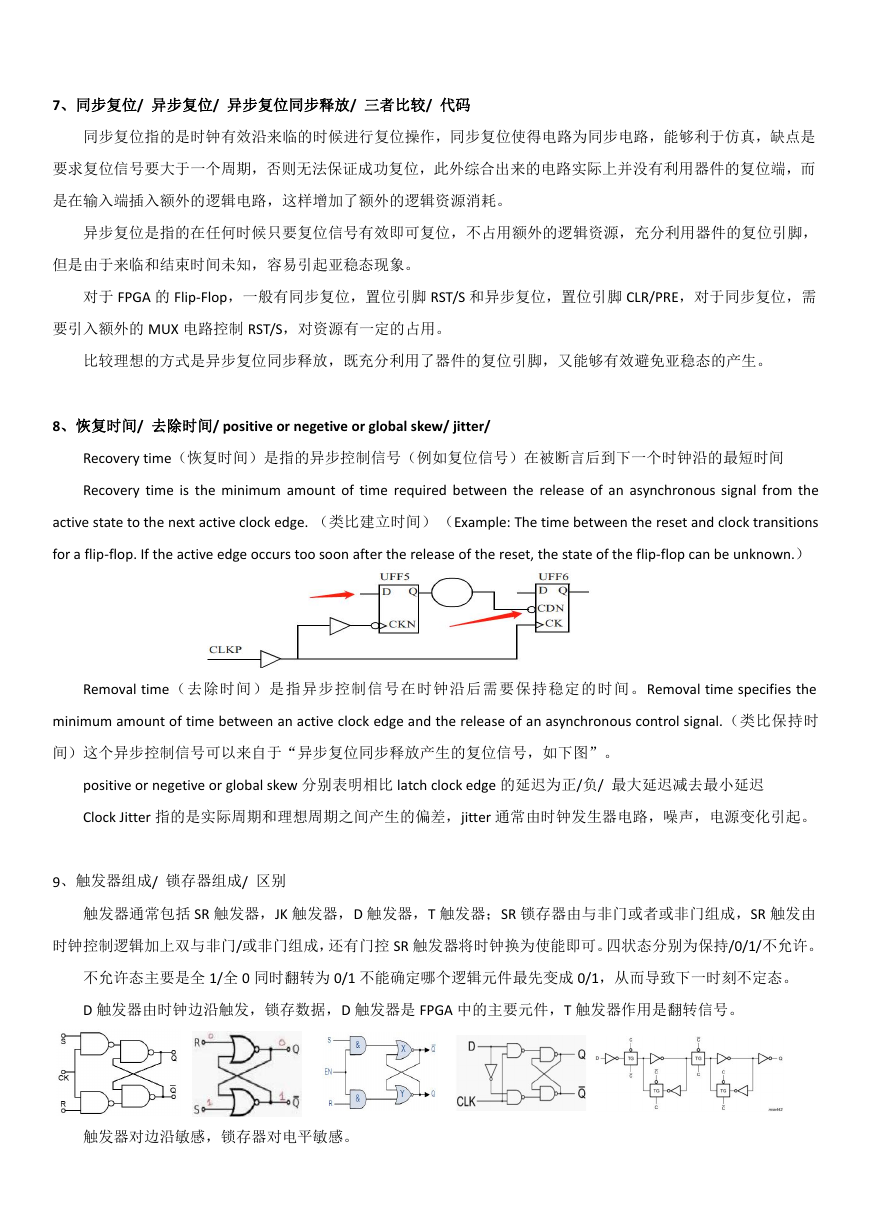

8、恢复时间/ 去除时间/ positive or negetive or global skew/ jitter/

Recovery time(恢复时间)是指的异步控制信号(例如复位信号)在被断言后到下一个时钟沿的最短时间

Recovery time is the minimum amount of time required between the release of an asynchronous signal from the

active state to the next active clock edge. (类比建立时间) (Example: The time between the reset and clock transitions

for a flip-flop. If the active edge occurs too soon after the release of the reset, the state of the flip-flop can be unknown.)

Removal time(去除时间)是指异步控制信号在时钟沿后需要保持稳定的时间。Removal time specifies the

minimum amount of time between an active clock edge and the release of an asynchronous control signal.(类比保持时

间)这个异步控制信号可以来自于“异步复位同步释放产生的复位信号,如下图”。

positive or negetive or global skew 分别表明相比 latch clock edge 的延迟为正/负/ 最大延迟减去最小延迟

Clock Jitter 指的是实际周期和理想周期之间产生的偏差,jitter 通常由时钟发生器电路,噪声,电源变化引起。

9、触发器组成/ 锁存器组成/ 区别

触发器通常包括 SR 触发器,JK 触发器,D 触发器,T 触发器;SR 锁存器由与非门或者或非门组成,SR 触发由

时钟控制逻辑加上双与非门/或非门组成,还有门控 SR 触发器将时钟换为使能即可。四状态分别为保持/0/1/不允许。

不允许态主要是全 1/全 0 同时翻转为 0/1 不能确定哪个逻辑元件最先变成 0/1,从而导致下一时刻不定态。

D 触发器由时钟边沿触发,锁存数据,D 触发器是 FPGA 中的主要元件,T 触发器作用是翻转信号。

触发器对边沿敏感,锁存器对电平敏感。

�

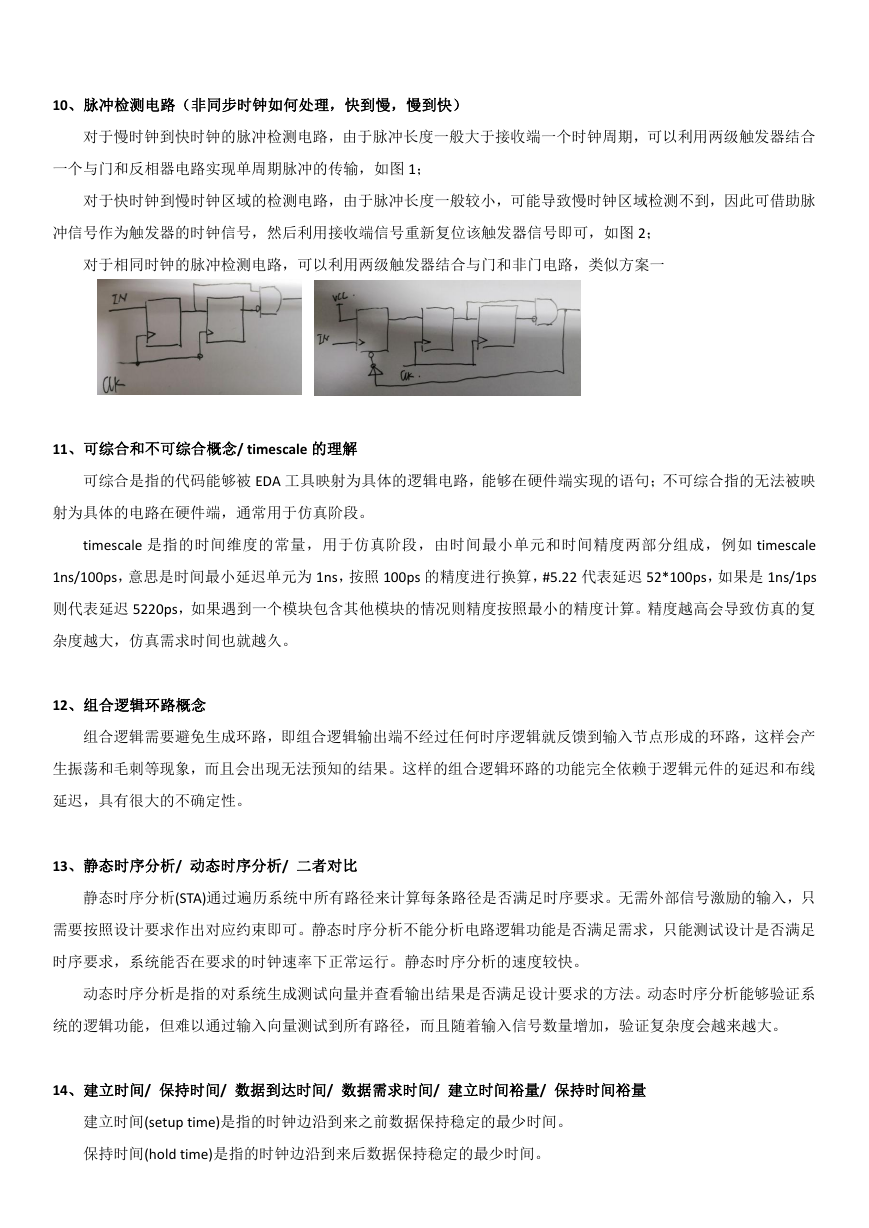

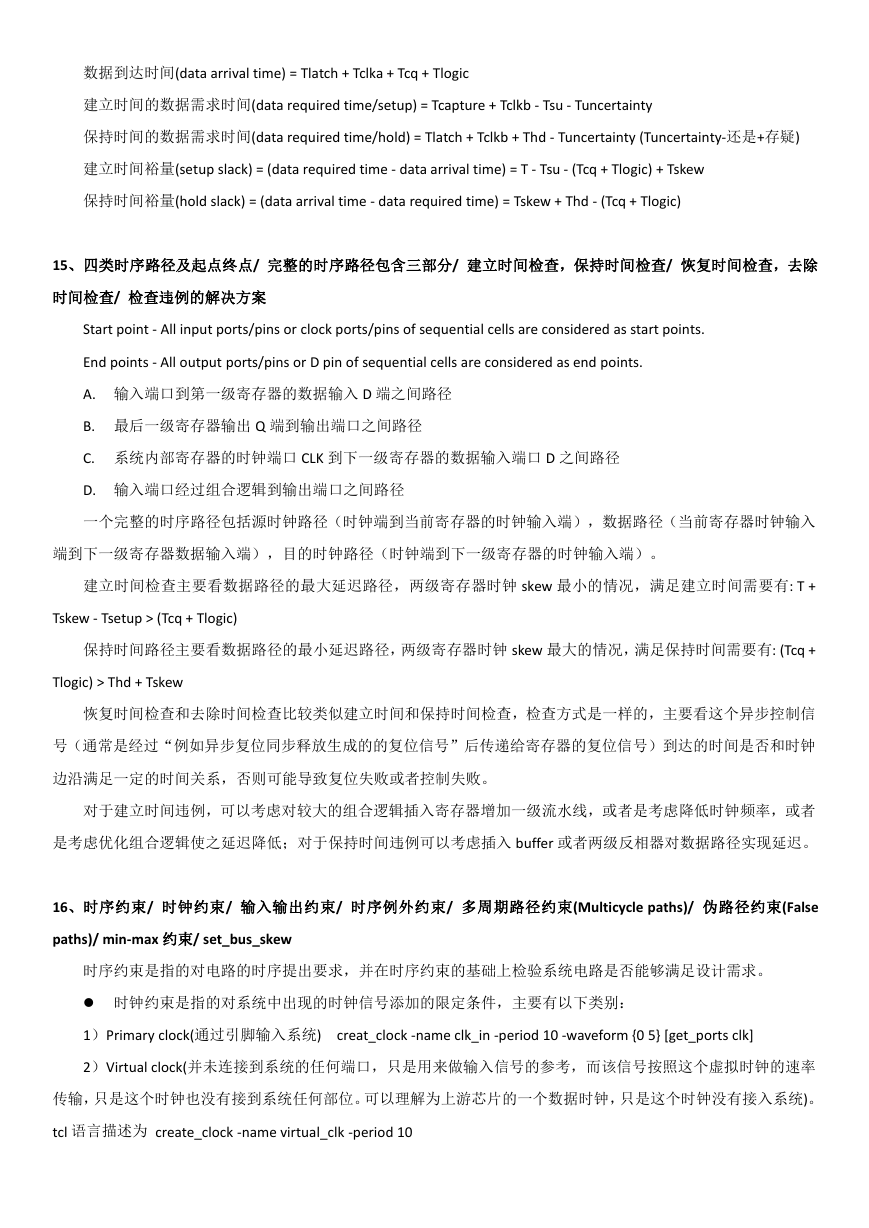

10、脉冲检测电路(非同步时钟如何处理,快到慢,慢到快)

对于慢时钟到快时钟的脉冲检测电路,由于脉冲长度一般大于接收端一个时钟周期,可以利用两级触发器结合

一个与门和反相器电路实现单周期脉冲的传输,如图 1;

对于快时钟到慢时钟区域的检测电路,由于脉冲长度一般较小,可能导致慢时钟区域检测不到,因此可借助脉

冲信号作为触发器的时钟信号,然后利用接收端信号重新复位该触发器信号即可,如图 2;

对于相同时钟的脉冲检测电路,可以利用两级触发器结合与门和非门电路,类似方案一

11、可综合和不可综合概念/ timescale 的理解

可综合是指的代码能够被 EDA 工具映射为具体的逻辑电路,能够在硬件端实现的语句;不可综合指的无法被映

射为具体的电路在硬件端,通常用于仿真阶段。

timescale 是指的时间维度的常量,用于仿真阶段,由时间最小单元和时间精度两部分组成,例如 timescale

1ns/100ps,意思是时间最小延迟单元为 1ns,按照 100ps 的精度进行换算,#5.22 代表延迟 52*100ps,如果是 1ns/1ps

则代表延迟 5220ps,如果遇到一个模块包含其他模块的情况则精度按照最小的精度计算。精度越高会导致仿真的复

杂度越大,仿真需求时间也就越久。

12、组合逻辑环路概念

组合逻辑需要避免生成环路,即组合逻辑输出端不经过任何时序逻辑就反馈到输入节点形成的环路,这样会产

生振荡和毛刺等现象,而且会出现无法预知的结果。这样的组合逻辑环路的功能完全依赖于逻辑元件的延迟和布线

延迟,具有很大的不确定性。

13、静态时序分析/ 动态时序分析/ 二者对比

静态时序分析(STA)通过遍历系统中所有路径来计算每条路径是否满足时序要求。无需外部信号激励的输入,只

需要按照设计要求作出对应约束即可。静态时序分析不能分析电路逻辑功能是否满足需求,只能测试设计是否满足

时序要求,系统能否在要求的时钟速率下正常运行。静态时序分析的速度较快。

动态时序分析是指的对系统生成测试向量并查看输出结果是否满足设计要求的方法。动态时序分析能够验证系

统的逻辑功能,但难以通过输入向量测试到所有路径,而且随着输入信号数量增加,验证复杂度会越来越大。

14、建立时间/ 保持时间/ 数据到达时间/ 数据需求时间/ 建立时间裕量/ 保持时间裕量

建立时间(setup time)是指的时钟边沿到来之前数据保持稳定的最少时间。

保持时间(hold time)是指的时钟边沿到来后数据保持稳定的最少时间。

�

数据到达时间(data arrival time) = Tlatch + Tclka + Tcq + Tlogic

建立时间的数据需求时间(data required time/setup) = Tcapture + Tclkb - Tsu - Tuncertainty

保持时间的数据需求时间(data required time/hold) = Tlatch + Tclkb + Thd - Tuncertainty (Tuncertainty-还是+存疑)

建立时间裕量(setup slack) = (data required time - data arrival time) = T - Tsu - (Tcq + Tlogic) + Tskew

保持时间裕量(hold slack) = (data arrival time - data required time) = Tskew + Thd - (Tcq + Tlogic)

15、四类时序路径及起点终点/ 完整的时序路径包含三部分/ 建立时间检查,保持时间检查/ 恢复时间检查,去除

时间检查/ 检查违例的解决方案

Start point - All input ports/pins or clock ports/pins of sequential cells are considered as start points.

End points - All output ports/pins or D pin of sequential cells are considered as end points.

A. 输入端口到第一级寄存器的数据输入 D 端之间路径

B. 最后一级寄存器输出 Q 端到输出端口之间路径

C. 系统内部寄存器的时钟端口 CLK 到下一级寄存器的数据输入端口 D 之间路径

D. 输入端口经过组合逻辑到输出端口之间路径

一个完整的时序路径包括源时钟路径(时钟端到当前寄存器的时钟输入端),数据路径(当前寄存器时钟输入

端到下一级寄存器数据输入端),目的时钟路径(时钟端到下一级寄存器的时钟输入端)。

建立时间检查主要看数据路径的最大延迟路径,两级寄存器时钟 skew 最小的情况,满足建立时间需要有: T +

Tskew - Tsetup > (Tcq + Tlogic)

保持时间路径主要看数据路径的最小延迟路径,两级寄存器时钟 skew 最大的情况,满足保持时间需要有: (Tcq +

Tlogic) > Thd + Tskew

恢复时间检查和去除时间检查比较类似建立时间和保持时间检查,检查方式是一样的,主要看这个异步控制信

号(通常是经过“例如异步复位同步释放生成的的复位信号”后传递给寄存器的复位信号)到达的时间是否和时钟

边沿满足一定的时间关系,否则可能导致复位失败或者控制失败。

对于建立时间违例,可以考虑对较大的组合逻辑插入寄存器增加一级流水线,或者是考虑降低时钟频率,或者

是考虑优化组合逻辑使之延迟降低;对于保持时间违例可以考虑插入 buffer 或者两级反相器对数据路径实现延迟。

16、时序约束/ 时钟约束/ 输入输出约束/ 时序例外约束/ 多周期路径约束(Multicycle paths)/ 伪路径约束(False

paths)/ min-max 约束/ set_bus_skew

时序约束是指的对电路的时序提出要求,并在时序约束的基础上检验系统电路是否能够满足设计需求。

时钟约束是指的对系统中出现的时钟信号添加的限定条件,主要有以下类别:

1)Primary clock(通过引脚输入系统)

creat_clock -name clk_in -period 10 -waveform {0 5} [get_ports clk]

2)Virtual clock(并未连接到系统的任何端口,只是用来做输入信号的参考,而该信号按照这个虚拟时钟的速率

传输,只是这个时钟也没有接到系统任何部位。可以理解为上游芯片的一个数据时钟,只是这个时钟没有接入系统)。

tcl 语言描述为 create_clock -name virtual_clk -period 10

�

3)Generated clock(通过 PLL 或者内部逻辑,如计数分频生成的时钟)

example1:

create_generated_clock -name

clk_div2 -source [get_ports clkin] -divide_by 2 [get_pins clk_div2];

example2:

create_generated_clock -name

clk_div_mul -source [get_pins mmcm0/clkin] -multiply_by 4 -divide_by 3 [get_pins mmcm0/clkout];

4)Clock groups(主要对异步时钟组之间约束,避免对异步时钟之间进行无效的时序分析,例如两个独立的时钟

以及他们生成的时钟网络之间,或者是虽然来自同一个时钟源但是生成的时钟在 1000clk 内无法确定公共周期的时

钟之间) set_clock_groups -name async_clk -asynchronous -group clk1 -group clk2; set_clock_groups -name clkunexclusive

-group clk0 -group clk1;

5)Clock latency(由于 EDA 工具通常会自动计算内部网络的时钟延迟,因此通常只需要提供器件外部时钟走线延

迟即可) set_clock_latency -source -early 0.2 [get_ports sysclk];

set_clock_latency -source -late 0.5 [get_ports sysclk]

6)Clock jitter(包含 input_jitter 和 system_jitter)

set_input_jitter sysclk 0.3;

set_system_jitter 0.11

7)Clock uncertainty( 为 特 定 的 时 钟 或 者 时 钟 之 间 约 束 ) set_clock_uncertainty 0.1 [get_clocks clk];

set_clock_uncertainty 0.2 from [get_ports clk1] to [get_clocks clk2]

输入输出约束

1)set_input_delay(用于确定和系统某个时钟相关的输入信号的外部路径延迟,通常取决于外部器件输出的最后

一级寄存器的 Tcq 和中间走线延迟。Consequently, the input delay value can be positive or negative, depending on the

clock and data relative phase at the interface of the device,这个相关的时钟可以来自于系统的某个时钟或者虚拟时钟)

example1: set_input_delay -clock sysclk [get_ports din];

example2: set_input_delay -clock sysclk -max 4 [get_ports din]

example3: create_clock -name clk_virtual - period 10

set_input_delay -clock clk_virtual -min 2 [get_ports din2]

2)set_output_delay(用于确定和系统某个时钟相关的输出信号的外部路径延迟,通常取决于外部走线延迟和下

游芯片第一级输入寄存器的建立时间和保持时间)

example: set_output_delay -clock sysclk -min 2 [get_ports dout]

时序例外包含多周期路径约束,伪路径约束,最大最小延迟约束

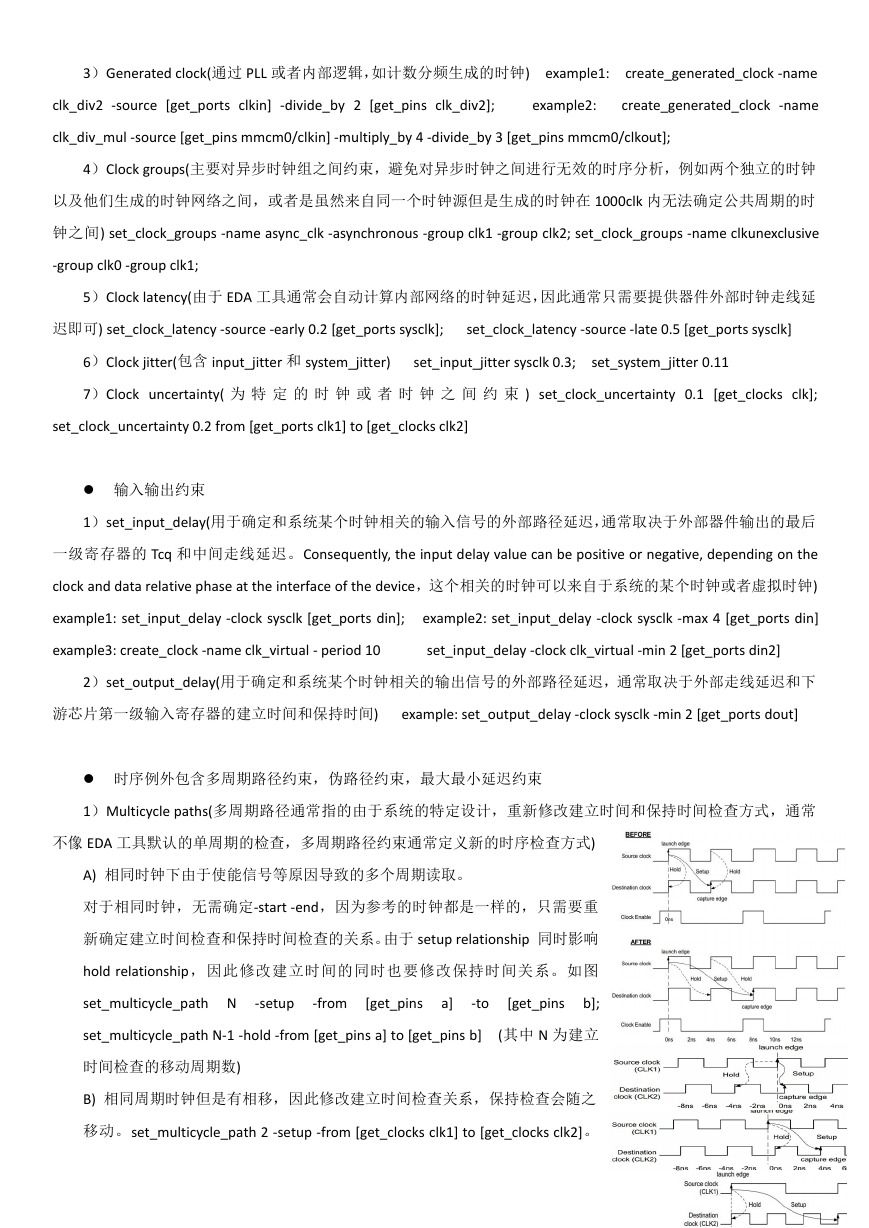

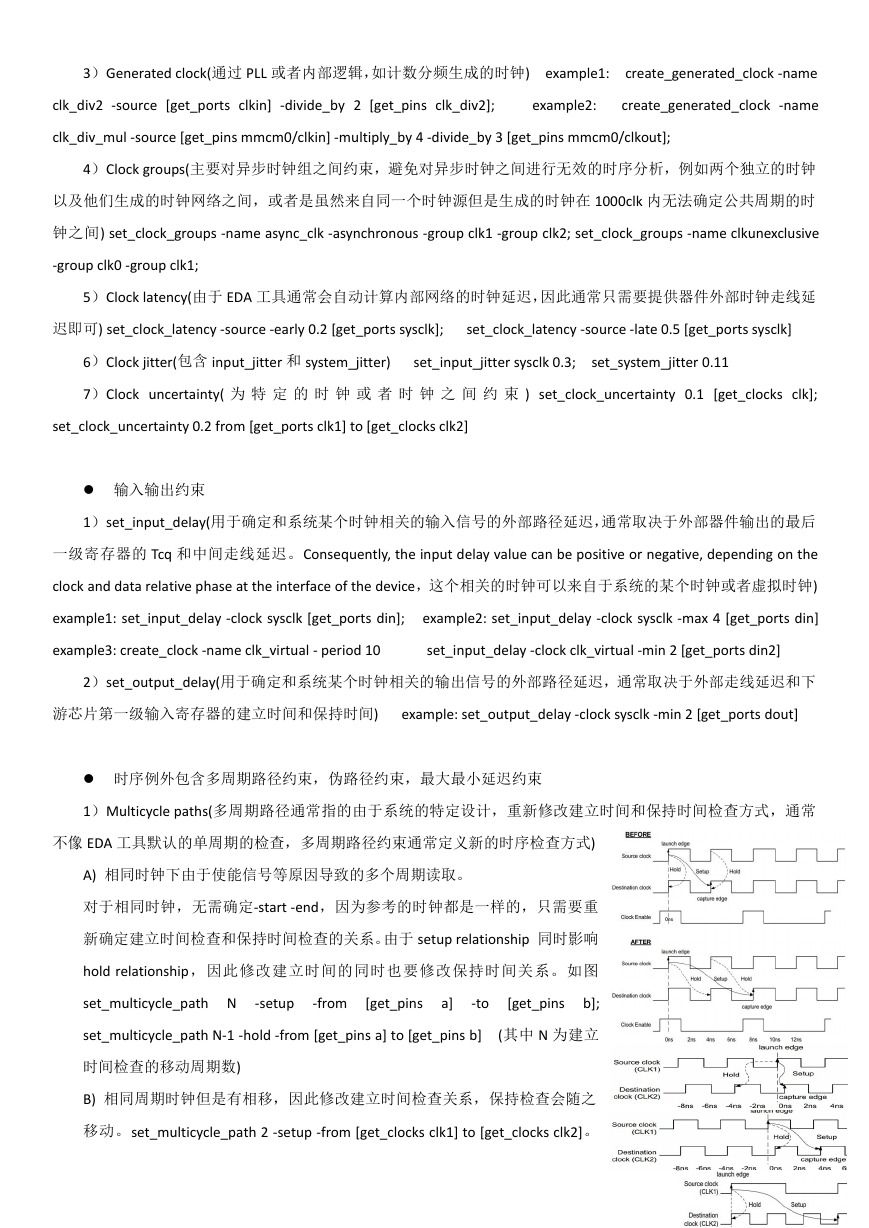

1)Multicycle paths(多周期路径通常指的由于系统的特定设计,重新修改建立时间和保持时间检查方式,通常

不像 EDA 工具默认的单周期的检查,多周期路径约束通常定义新的时序检查方式)

A) 相同时钟下由于使能信号等原因导致的多个周期读取。

对于相同时钟,无需确定-start -end,因为参考的时钟都是一样的,只需要重

新确定建立时间检查和保持时间检查的关系。由于 setup relationship 同时影响

hold relationship,因此修改建立时间的同时也要修改保持时间关系。如图

set_multicycle_path N -setup

-from [get_pins

a]

-to

[get_pins

b];

set_multicycle_path N-1 -hold -from [get_pins a] to [get_pins b]

(其中 N 为建立

时间检查的移动周期数)

B) 相同周期时钟但是有相移,因此修改建立时间检查关系,保持检查会随之

移动。set_multicycle_path 2 -setup -from [get_clocks clk1] to [get_clocks clk2]。

�